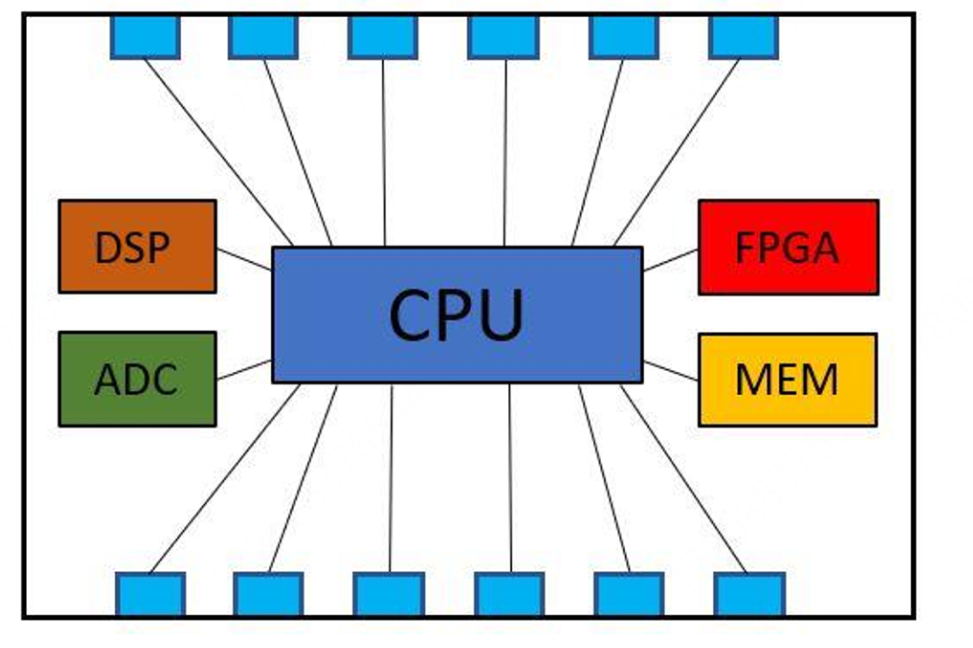

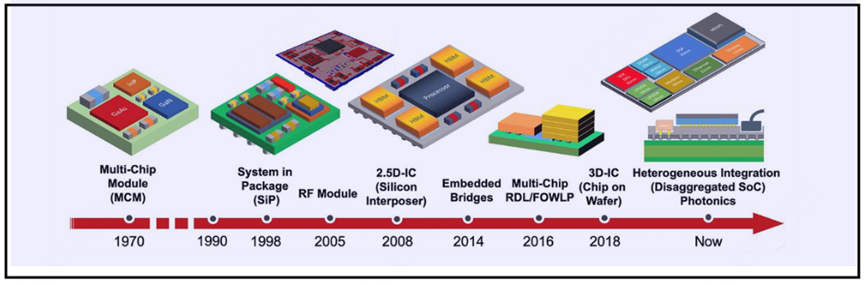

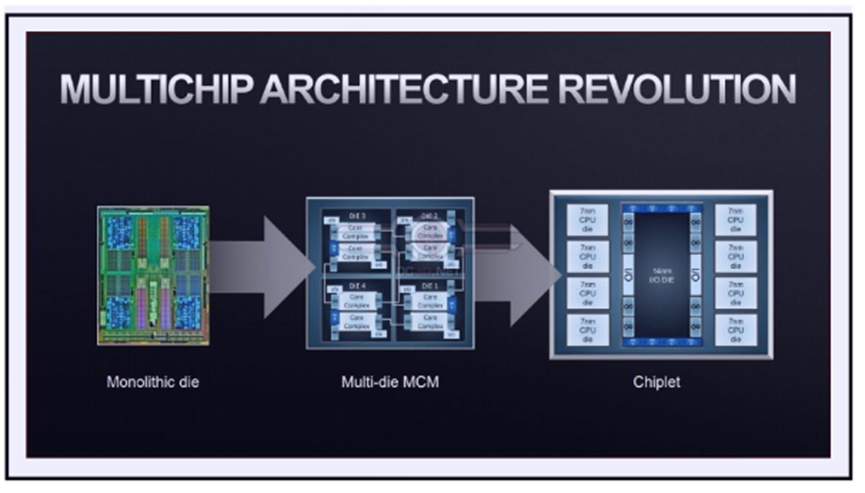

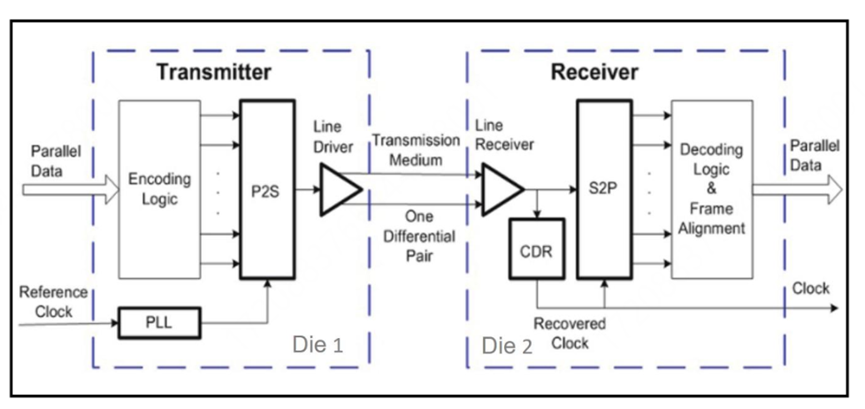

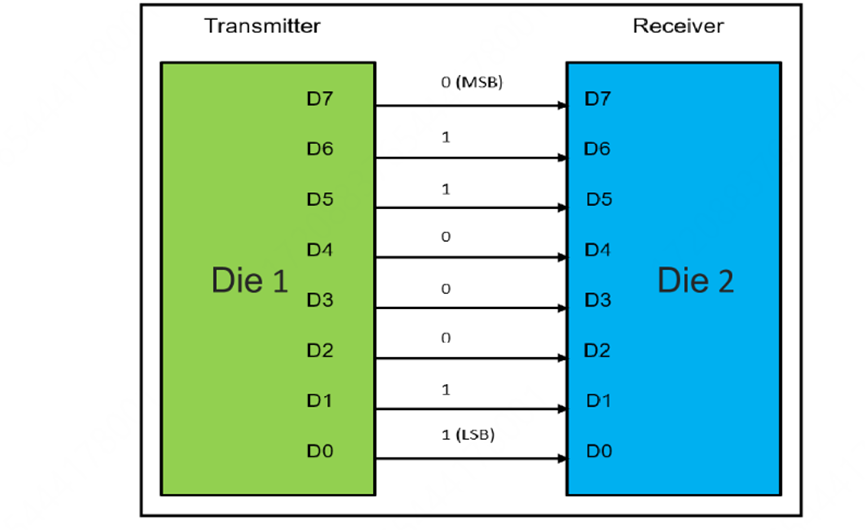

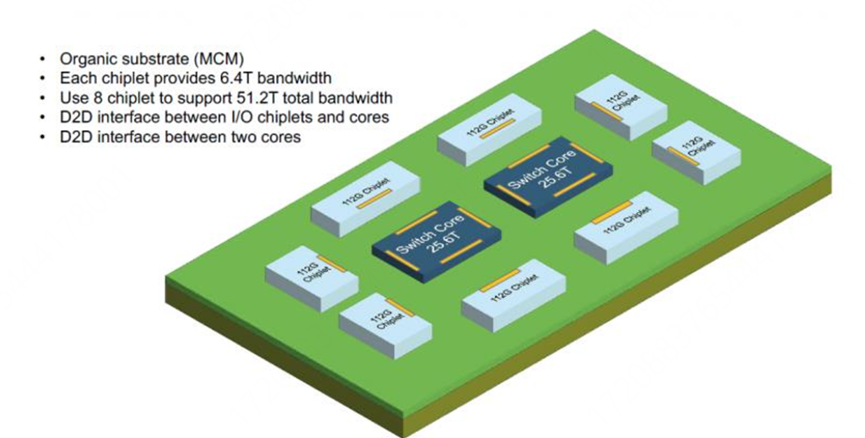

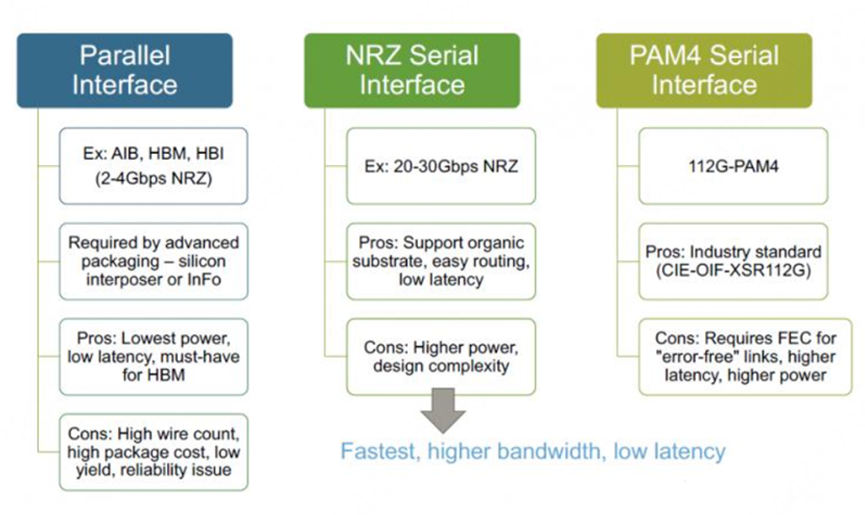

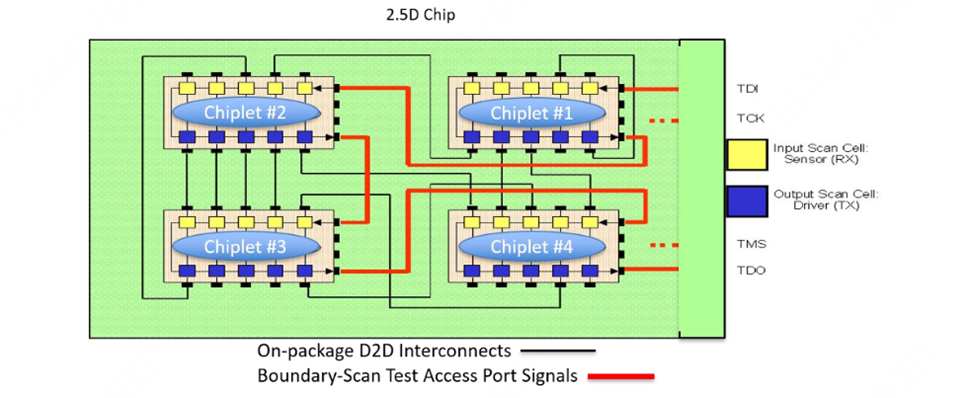

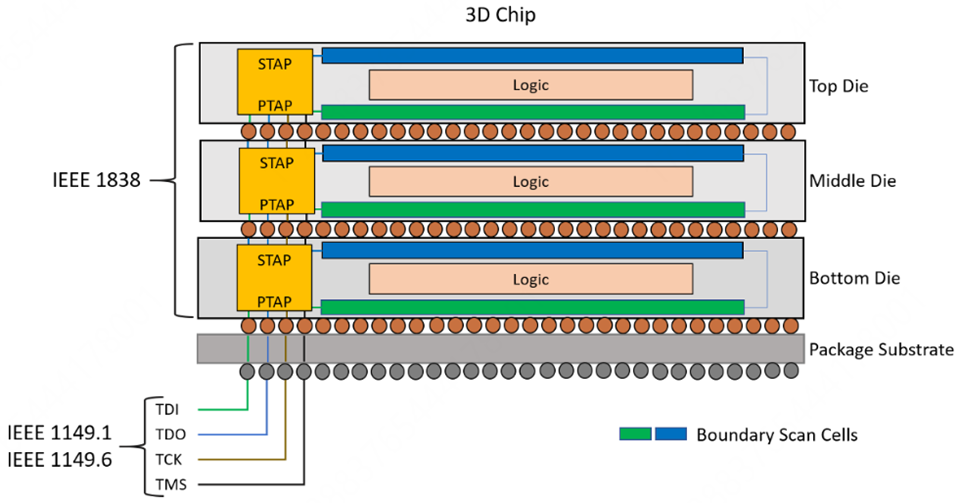

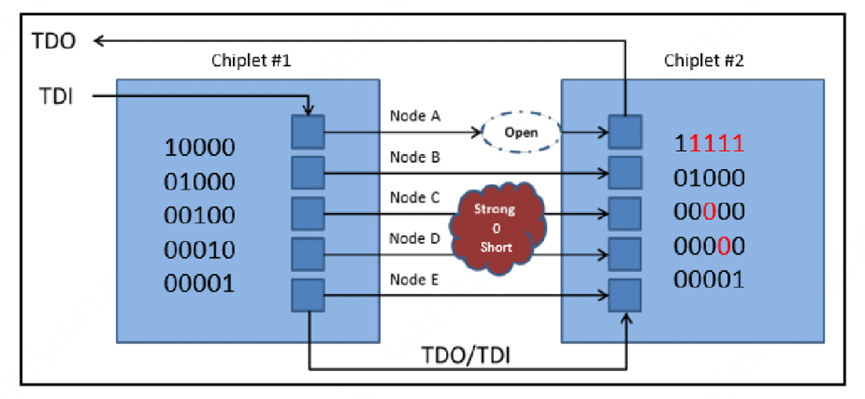

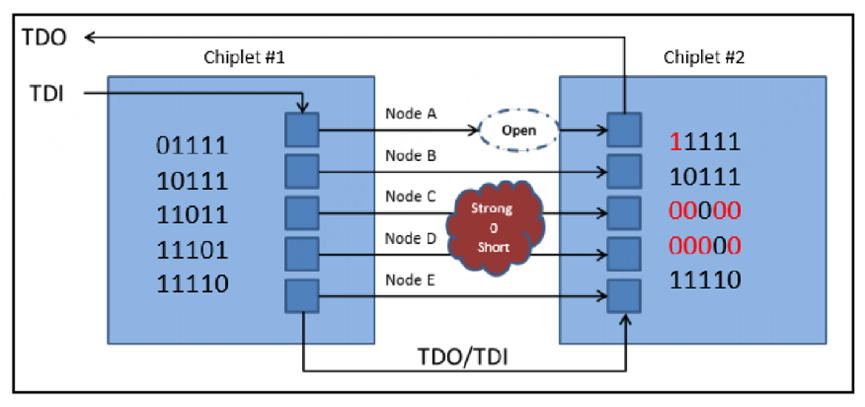

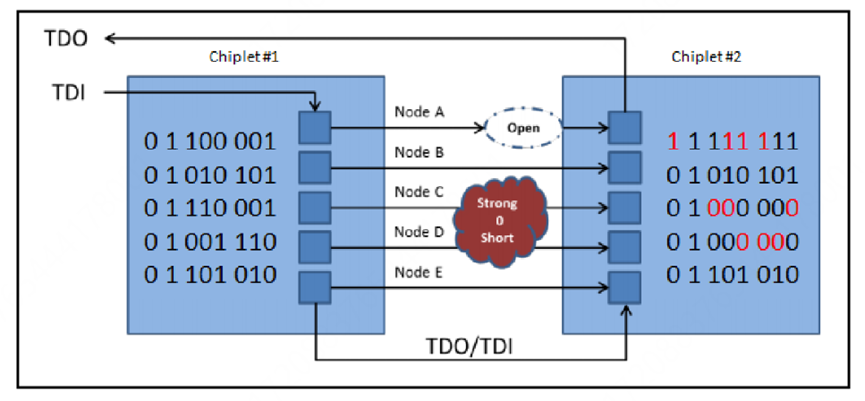

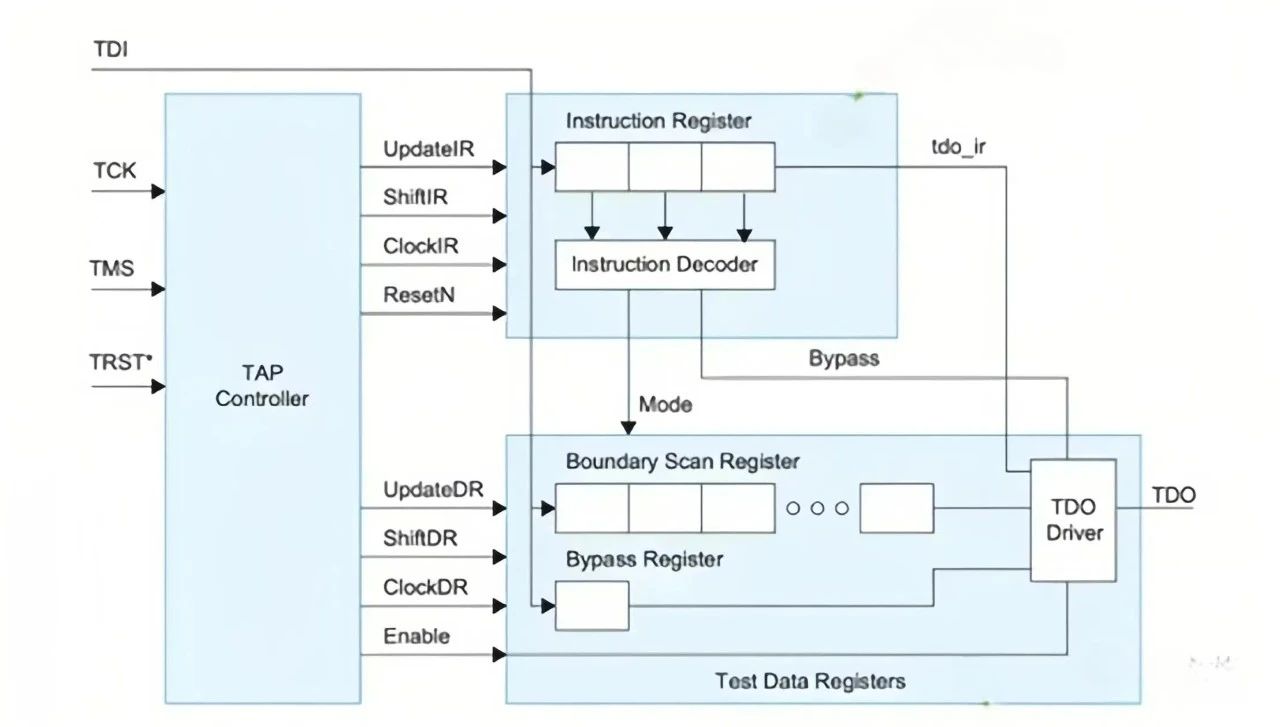

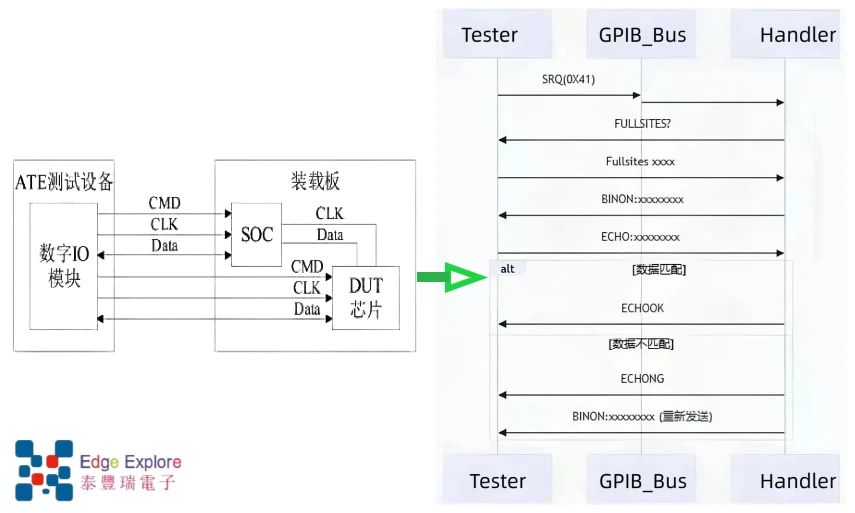

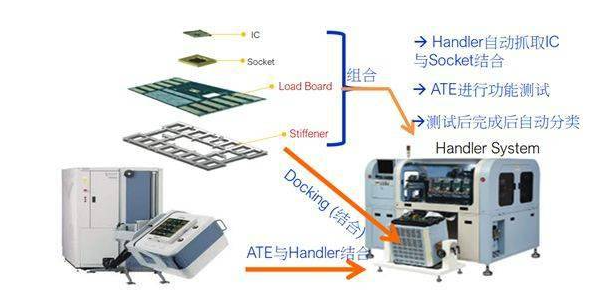

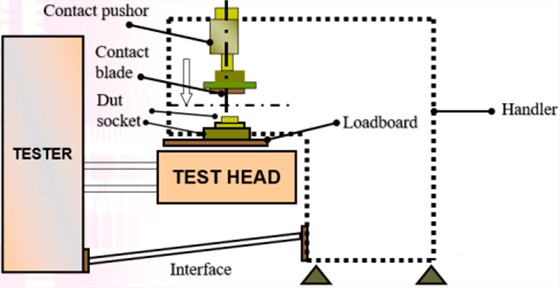

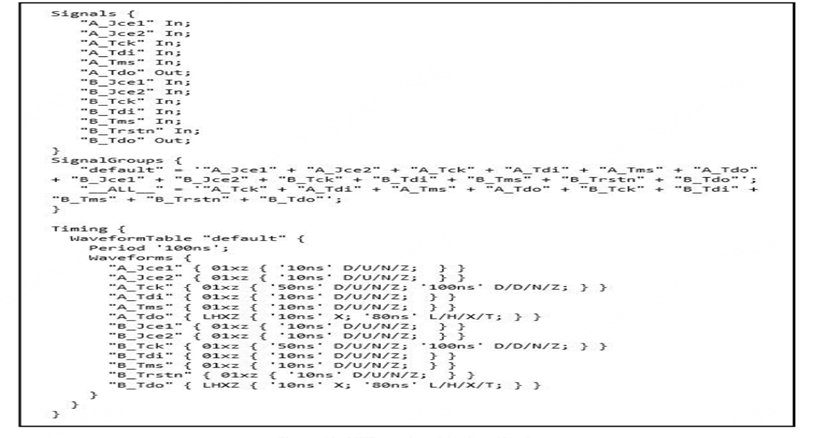

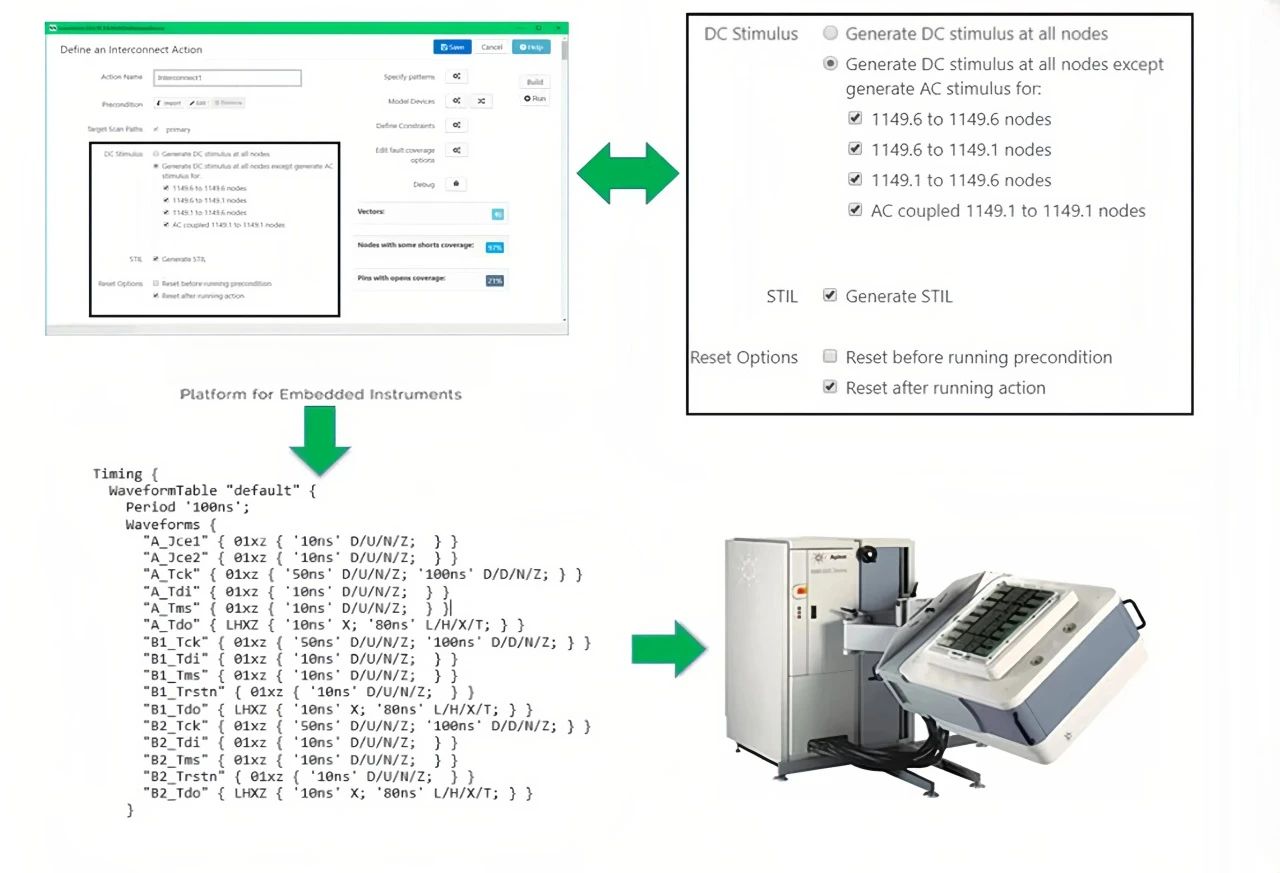

ATE与Handler用于边界扫描的芯片级互连测试一.概述 基于芯片的多芯片器件作为异构集成设计方法的产物,在当今芯片设计和实现策略中扮演着重要角色。实现多芯片器件的动力始于20世纪70年代,当时采用了一种封装创新方法,包括在封装规模的基板上放置多个互连的芯片。  这些器件被称为多芯片模块 (MCMs)。随着时间的推移,出现了其他的封装创新,如系统级封装 (SiP) 、系统级集成芯片 (SoIC)。2.5D集成电路 (ICs) 和3D-IC封装。多芯片封装创新使得半导体行业能够创造出更小、更快、可配置和更低功耗的IC。  图1.先进封装技术的时间线 类似于放置在印刷电路板 (PCB) 上的封装芯片,多芯片封装内小芯片之间的互连必须经过结构完整性测试。结构测试通常在制造过程中在芯片级自动化测试设备上进行,然后再将器件运送给最终用户。 Chiplet die到die(D2D) 结构测试涉及数字测试向量的应用,这些向量被格式化为在芯片级测试中使用。这些数字测试向量可能是用于设计小芯片的电子设计自动化 (EDA) 工具的产物。测试向量由嵌入式仪器使用小芯片的输入/输出 (IO) 资源进行应用。本文研究导致半导体行业异构集成设计和D2D互连测试方法发展的行业趋势。 二.基于芯片级封装的多裸片器件 随着半导体行业继续朝着创造更高效、成本更低的芯片制造和设计方法迈进,一种创新封装趋势已经出现。这种趋势最初是在20世纪60年代提出的。这种方法建议将多个晶片器件封装在一个单个芯片封装内,这是一种被称为异质集成的设计方法。 异构集成涉及将各种不同的元素结合成一个功能系统。这些不同元素是硅芯片(以下简称“小芯片”);当它们组合在一个中介层或硅基板上时,就构成了一个结构化的功能性系统。小芯片是一种集成电路,专门设计为与其他小芯片一起工作,以形成更大、更复杂的芯片。多片器件中的小芯片可以根据所需的芯片功能进行选择、排列和组装。 异构集成允许封装具有不同功能、不同工艺技术,有时甚至来自不同芯片制造商的片上系统。这些组合在一起的芯片可以有不同的功能(例如处理器、信号处理器、缓存器、传感器、光子学、射频和MEMS)和技术(例如:一个优化了晶片尺寸而另一个则优化了低功耗)。这些组装而成的不同硅芯片可以在各种选项中进行封装。单片晶片难以超过一定尺寸,制造包含更多功能的大芯片成本更高。考虑到这些事实,半导体行业需要一种方法来扩大产品规模以提高性能、提供高硅产量并降低成本。作为先进封装技术发展的例子,AMD的第一代EPYC处理器。从单一设计迁移到利用四个相互连接的八核处理器的MCM。  图2.从单片芯片到基于小芯片的封装架构 展望未来,AMD设计了芯片级组件来处理特定的处理器任务。AMD第二代EPYC和第三代Ryzen处理器提供了更高的扩展性,并允许每个硅片优化以使用小型7纳米和14纳米芯片级组件提供最佳延迟和功率特性。先进的封装创新产生了: 1. 更小的封装 2. 低功率器件 3. 更大的芯片可配置性 4. 更快的芯片上市时间 5. 整体制造成本降低 三.多芯片器件D2D互连 多芯片器件内的高速D2D互连可以在GHz范围内运行,同时提供GT/s的数据。与异构集成设计相关的一个挑战是在操作模式下适应每个小芯片之间移动的大量数据。为了适应这种高速传输,在尽量减少噪声的同时,数字串行器/解串器(也称为SerDes)被用作小芯片D2D互连。 虽然在先进的封装解决方案方面取得了巨大进步,但选择一种能够容纳大量数据且与封装解决方案兼容的互连技术非常重要。理想的多芯片互连技术是可扩展、低功耗、面积效率高,并且可以在低成本硅和封装技术中构建。多芯片器件中使用的D2D互连技术有两类: · 中程和长距串行器/解串器(SerDes) · 短距离超距离SerDes(USR/XSR)  图3. SerDes D2D互连 这些D2D互连适应高速数据传输,同时最小化噪声和最小化D2D互连的数量。诸如高带宽存储器、高级接口总线、束线(HBM,AIB,BoW)等并行接口链路技术易于实现且具有高带宽;但可能需要许多导线才能完全实施。  图4.并行D2D互连 图中的MCM是一个以太网芯片,有8个周边的芯片小块,在操作模式下为交换机核心提供6.4TB的数据。为了适应这种高速传输,并尽量减少噪声,SerDes用于芯片小块之间的D2D互连。在信号方案方面,D2D互连有几个技术选择: 01并行 02 非零返回(NRZ) 03 脉冲幅度调制4级(PAM4) 当需要较低带宽时,使用并行接口。在选择SerDes方法时,会利用NRZ和PAM4信号方案来实现较高带宽。多芯片器件中最佳的D2D通信在于优化六个经常相互竞争但又相互关联的因素: • 可用的晶片面积 • 功耗 • 可扩展性  图5. 8个芯片的以太网交换机芯片 一个关键的设计考虑因素是封装上的D2D接口,如上图中黄色突出显示。下表对用于评估D2D互连的技术选项进行了分类。 芯片级分布式数据处理需要在芯片之间进行高速数据传输。并行和串行是两种数据传输方式。与仅需一对连接的串行数据传输相比, 并行数据传输需要多个芯片之间的连接。互连比并行D2D互连具有几个优点。  表1.用于D2D互连的评估技术选项 四.测试多芯片器件的D2D互连 IEEE 1149.1测试访问端口(TAP)和边界扫描架构的标准是在1980年代构思并在1990年被采用为标准的。边界扫描测试通过连接器和四线串行接口 称为测试访问端口 (TAP) 应用于PCB。实现时,这个接口通常被称为 “JTAG端口”。 边界扫描标准已被业界广泛采用,并且现在被部署在芯片、PCB和系统中。由于其广泛的接受度,边界扫描嵌入式仪器已经被其他应用所采纳,并为其提供了其他测试标准的基础。一个相关的标准,IEEE 1149.6 高级数字网络边界扫描测试标准,用于测试高速差分和AC耦合互连之间的芯片在PCB和系统上的连接。 IEEE 1838三维堆叠集成电路测试访问架构标准是一个以芯片为中心的标准; 它适用于旨在成为多芯片堆栈一部分的芯片。本标准定义了芯片级特征,当兼容芯片以堆栈的形式聚集在一起时,包含一个堆栈级架构,该架构能够传输用于测试的控制和数据信号。在 (a) 预堆叠和 (b) 后堆叠情况下的芯片内电路和 (c) 芯片间互连,后者适用于在预封装、后封装和板级情况下的部分堆栈和完整堆栈。本标准所涉及的芯片间互连技术的主要焦点是硅通孔 (TSVs); 然而,这并不排除其与其他互连技术如与引线键合一起使用。 由于多芯片封装和D2D互连让人想起PCB上芯片之间的互连,适用于PCB的测试方法可以应用于测试D2D互连。由IEEE 1149.1标准(用于测试访问端口和边界扫描架构)和IEEE1149.6标准(用于高级数字网络的边界扫描测试)生成的测试模式适合于结构测试包含多芯片封装的D2D互连。 边界扫描是一种基于静态矢量的测试技术,使用片上嵌入式仪器进行结构测试。因此,边界扫描可以非常快速地执行短路、开路、粘滞和桥接故障测试和检测,芯片是封装和安装在PCB上还是在多芯片器件中堆叠芯片。提供的诊断是对器件芯片和网络/引脚级别的诊断。边界扫描提供了一种非常有效的检测和诊断原位组装缺陷的方法,因为在许多情况下,网络访问不可用或探测网络不可靠。边界扫描适用于发现单端和差分网络上的缺陷。  图6.符合IEEE标准的2.5D芯片测试  图7.可使用IEEE标准进行测试的3D芯片 五.D2D互连测试模式 01.测试概述 电平1,电平0,以及TAP控制器模式用于测试多芯片器件的D2D互连之间的短路、开路、粘滞和桥接故障。今天的边界扫描工具,在提供网络列表、边界扫描描述语言(BSDL)文件和器件模型时,使用其内置的自动生成测试模式或测试向量(ATPG),为任何大小的设计创建D2D互连测试模式。这些D2D互连测试向量可以在制造现场几秒钟内应用。 02.电平1模式 电平1:模式可用于测试多芯片器件的小芯片之间的D2D互连。此测试的名称来自测试期间写入的位值。电平1测试模式涉及在第一个向量步骤期间在第一个网络上发送单个 “1”,而其他n-1网络设置为 “0”。在第二向量步骤中,“1” 应用于第二个网,而其他n-1网设置为 “0”。以这种方式,在所有n个网络中应用 (“行走”) 的 “1” 在许多步骤中。由于测试步骤的数量随着被测网线数量的增加而呈线性增长因此更高效的算法可能更为可取。  图8.使用电平1模式的芯片级D2D测试 该图显示了在一组网上的电平1模式的概念,这些网由左端的传输边界扫描单元应用,并且右端接收边界扫描单元捕获值。红色中的数值表示由于检测到故障而引起的位错误比较。 03.电平0模式 电平0模式可用于测试多芯片器件的小芯片之间的D2D互连。此测试的名称来自测试期间写入的位值。电平0测试模式涉及在第一个向量步骤期间在第一个网络上发送单个 “0”,而其他n-1网络设置为 “1”。在第二个向量步长中,“0” 应用于第二个网络,而其他n-1网络设置为 “1”。以这种方式,在所有n个网络中应用 (“行走”) 的 “0” 在许多步骤中。由于测试步骤的数量随着被测网线数量的增加而呈线性增长,因此更高效的算法可能更为可取。  图9.使用电平模式进行芯片级D2D测试 该图显示了在一组网上的电平 0 模式,这些模式由左端的传输边界扫描单元应用,并且由右端接收边界扫描单元捕获。红色值表示由于检测到故障而引起的位错误比较。 04.TAP多组网测试模式 TAP控制器多组网模式是一种扩展的二进制计数模式。多组网模式为短路、开路、粘滞和桥接故障提供了100%的故障覆盖率。测试步骤的数量随着被测网线数量的增长而呈对数增长,而不是线性增长。模式在确保完全覆盖和高效诊断的同时最小化了模式大小。多组网模式不需要与其他模式配对以增加测试覆盖率。  图10.使用多组网模式进行芯片级D2D测试 该图显示了在左侧传输边界扫描单元上应用的一组网上的多组网测试模式的概念,以及右侧接收边界扫描单元捕获的值。红色中的数值表示由于检测到故障而引起的位错误比较。瓦格纳模式是优化测试覆盖率和诊断效率最有效的模式。  图11.基本的TAP架构图  图12.ATE与Handler 测试原理图  图13.ATE与Handdler测试  图14.ATE与Hander测试示意图  图15.ATE与三温分选机(Triple TempHandler) 六.标准测试接口语言 IEEE 1450 标准测试接口语言(STIL)提供了一种数字测试模式和波形的通用测试语言。这些测试模式和波形可以移植到另一个测试环境或ATE平台中,用于多芯片器件之间的互连。在模拟数字芯片时,可以通过EDA工具生成STIL测试模式和波形。还可以通过后处理第三方工具输出的测试模式和波形来创建STIL。 EDA-to-Test流程充满了各种不同的测试信息格式。这些不同格式不仅存在于EDA工具和芯片供应商之间的接口,还存在于芯片供应商和ATE的接口中。由于这些差异,需要一种标准语言。STIL于1999年由工具和测试器联盟标准化,并由芯片和ATE行业的企业领导者组成。STIL测试模式和波形可以通过EDA工具生成。 STIL的创建是为了专门解决EDA工具生成大量数字测试数据以及在不同平台之间传输这些数字测试数据时日益增长的关注。EDA工具和芯片供应商之间没有直接接口,芯片供应商和ATE之间也没有直接接口。 因此,STIL 对创建测试数据的 EDA 供应商、处理测试数据的芯片供应商和接受测试数据的 ATE 供应商都有好处。STIL 可以移植到芯片 ATE,以应用于 D2D 互连,STIL 模式就会通过边界扫描单元应用于 D2D 互连。用STIL编写的测试程序一般由定义STIL的七个块组成:标题、信号、信号组、计时、模式突发、模式执行和模式。每个块都是根据要测试的芯片级互连D2D设计描述创建的。  图16.生成STIL标准测试接口语言 七.STIL标准测试接口语言在D2D测试中的应用 边界扫描测试一直使用其自动测试模式生成(ATPG)功能提供板级短路、开路、粘滞和桥接故障测试。随着最近的增强,现在可以生成STIL向量,芯片ATE可以应用这些 模式来测试芯片之间的D2D互连的短路、开路、粘滞和桥接故障。 STIL选项根据芯片BSDL和描述芯片如何相互连接的网表生成测试模式。使用STIL选项对芯片制造商和板卡设计人员具有几个关键价值: · 多芯片器件供应商可向下游电路板设计人员和制造商提供用于生成 STIL 模式的测试项目 · 电路板设计人员可对电路板和多芯片器件进行 D2D 互连测试,以确认质量 · 多芯片器件发现的问题可追溯到封装供应商,后者在其 ATE 上进行了相同的测试,以帮助调试是电路板问题还是多芯片封装问题  图17.STIL流程 八.总结 异构硅芯片随着先进封装的演变既带来了重大挑战,也带来了无与伦比的机遇。解决高缺陷密度、复杂热管理等问题,并确保组件间的可靠性,需要创新的解决方案,如先进的 ATPG 算法、 AI 驱动的预测性维护和自我修复互连。虽然生产这些先进封装的初始成本和复杂性较高,但实质性的性能改进和长期利益证明了投资的合理性。 D2D互连测试可以使用IEEE 1149.1测试访问端口和边界扫描架构标准以及IEEE 1149.6高级网络边界扫描测试标准来完成。每个标准都利自动测试模式生成方案来揭示芯片之间芯片互连上的短路、开路、粘滞和桥接故障。边界扫描测试利用硅芯片的嵌入式边界扫描单元基础设施。D2D互连测试在现场产生结构结果。IEEE 1838三维堆叠集成电路测试访问架构标准,定义了测试多堆叠芯片之间互连的测试访问基础设施。 使用STIL进行D2D互连测试符合整体多芯片器年制造测试流程。提供了一种自动化和可扩展的D2D互连测试解决方案,在整个多芯片器件生命周期中均可部署。 |