|

需要JEDEC原版电子文档,关注公众号【莱歌数字】,输入“JEDEC”获取。 电子冷却热工程的主要目标是降低集成电路器件的结温度。定义热阻是确定结温度的一种常用方法,给定了一组环境条件和一个组件的功耗。 然而,只有当所有供应商使用相同的标准测试方法来确定半导体器件的热阻时,这种方法才有意义。  承担在电子行业建立基准任务的实体是JEDEC固态技术协会。该行业集团最初是联合电子器件工程委员会,是电子工业联盟(EIA)的半导体标准化机构,代表了电子行业的所有领域。 JEDEC有50个委员会和小组委员会,所有这些委员会都由JEDEC董事会监督。JEDEC委员会的成员来自290家活跃在半导体行业的公司,无论是半导体组件的制造商还是用户。 JEDEC标准已被全世界的国家所接受。JEDEC标准和出版物的主要目的是通过消除制造商和购买者之间的误解,以及促进产品的互换性和改进,来保护公众利益。 这些标准的另一个功能是帮助JEDEC的非成员以最小的延迟选择和获得合适的产品 JESD51提供了对包含单个芯片半导体器件的封装的热测量方法的概述。实际的方法分布在几个文件中,可以选择性地用于满足特定的热测量要求。 表1给出了完整的JEDEC51标准系列的简要描述。 表1. JEDEC IC封装标准的热测量

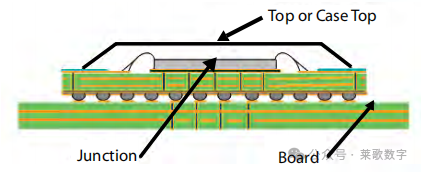

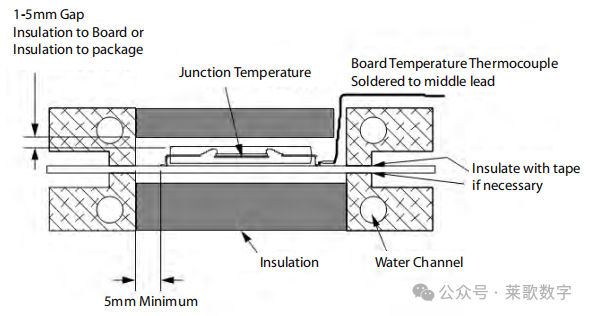

在JEDEC标准中,半导体器件的热表征需要测量结。有许多方法来测量模温度,如红外和液晶传感,但最常用的是前偏置二极管的电压降。 这种二极管是专门设计成热测试模和许多集成电路设备。通过测试二极管的测量电流必须足够大,以不受表面泄漏的影响,但又不够小,足以引起相当大的自热。 测量电流的典型值为100 μA到5 mA,具体取决于二极管的大小。 在JEDEC的标准下,有两种方法来测量结的温度。其中一种被称为静态模式,在监测连接温度的同时,加热功率持续地施加到被测设备(DUT)上。 该方法适用于热测试二极管和一些有源集成电路器件。另一种方法被称为动态模式,在此期间,功率对DUT施加一段特定的时间以达到平衡,然后切换到测量模式。这种方法适用于大多数有源集成电路。 使用JESD51标准生成的半导体的热表征被定义为热阻,并由公式1控制: θjx=(Tj-Tx)/Ph 在上式中, θjx是器件结到特定环境的热阻(°C/W),Tj是器件结温度(°C),Tx是环境的参考温度(°C),Ph是器件内的耗散功率(W)。 在JEDEC标准中使用的另一个定义是热特性参数,并由方程2控制: φjx=(Tj-Tx)/Ph θjx和φjx之间的主要区别在于,热阻θjx是在几乎所有的组件功耗都流过组件的顶部或底部的情况下计算出来的。 另一方面,在计算热表征参数时,功率是芯片中的总功耗,可以通过任何热路径离开芯片,而不仅仅是从封装的顶部或底部。 必须注意并强调的是,热阻和热表征参数值都可以用于比较不同的包装,并估计一个包装在特定应用中的性能。然而,这些估计不能是准确的,因为一个标准化的测试条件将与用户的应用程序不匹配。 为了确定半导体器件的热值,必须进行大量的温度测量。图1显示了这些测量值在单个芯片上的位置。  图1典型的温度位置指定 如表1所示,有12份有关组件包热测量的标准文件。-然而,在本文中,只简要解释了其中的少数标准。 JESD51-2 本标准规定了确定在自然对流条件(静止空气)下单个设备的热特性的准则。该方法要求建造一个测试夹具和一个30 x 30 x 30厘米(立方英尺)的外壳,并在其中进行测量。环境条件与安装在标准测试板上的表面测量包有关。 该板被放置在一个水平的位置,包装起来,在一个外壳中,以防止外来的气流,并只允许自然对流。该条件下的结-环境热阻由公式3指定并据此计算,这与公式1相似,其中特定的参考环境作为环境。 θja=(Tj-Ta)/Ph JESD51-2还包括一个确定热表征参数φjt的指南,从连接到包装的顶部中心。这个有用的值允许估计结的温度,并由方程4计算出来。此方程与式2相同,其中将特定的参考环境作为设备包的顶中心。 φjt=(Tj-Tt)/Ph JESD51-6 本标准规定了确定强制对流中集成电路装置的热特性的环境条件。该标准包括必须使用的风洞的规范。 这些风洞规范中最重要的是流量均匀性,流量波动不超过测试室截面平均速度的±5%,或沿测试截面长度的±5%。 另一个规格是平均流量的涡流,它必须小于平均流速的5%。流量旋流是用能够测量至少两个方向上的流量的三轴或交叉线风速计来测量的. 本标准还规定了风洞试验段集成电路的位置指南。根据JESD51-3和JESD51-7的规定,IC包安装在测试板上,可以放置在不同流板方向的风洞的试验室部分,必须在风速仪的上游测量流速,读数精度±为4%。 环境温度必须用导线直径不大于0.5 mm的校准热电偶来测量. 连接到空气的热阻被指定为θjma,即从连接到移动空气的阻力。其定义与方程1相似,以特定的参考环境作为移动的空气. 本标准中另一个有用的电阻值是结-板热表征参数φjb,由公式5定义, φjb=(Tj-Tb)/Ph JESD51-8 本标准提供了获得JESD51-7中规定的安装在高导电性板上的集成电路的结到板热阻的指南。电阻见公式6,表示结和板之间水平扩散的热阻。板的温度是在接近板表面的一个包的中心痕迹。 θjb=(Tj-Tb)/Ph 为了将几乎所有的热量转移到板上,使用了一个环式铜冷板。在冷板的顶部和底部的包装开口是绝缘的。冷板被夹在板上至少5毫米的痕迹上。冷板夹具区域必须至少为4毫米宽。进入的冷却液应控制在+2到-5°C的环境室温范围内。 这种冷板的原理图如图2所示  图2.环形冷板ΘJB试验装置横截面示意图 设计、尺寸和功耗。JEDEC测量ΘJC方法的开发正在进行中。 JEDEC-51系列标准已经允许半导体器件制造商以一致的方式报告热信息。这使得最终用户能够正确地理解、解释和使用所报告的数据。从这些标准中获益的一门特殊学科是热工程。 JEDEC热标准使热工工程师能够使用报告的数据对集成电路器件进行热表征,并设计和开发能够管理和保持热量在安全范围内的产品。 这不仅大大延长了电子元件的寿命,而且随着技术的进步,允许设计和实现更快的具有更高热输出的设备。 |