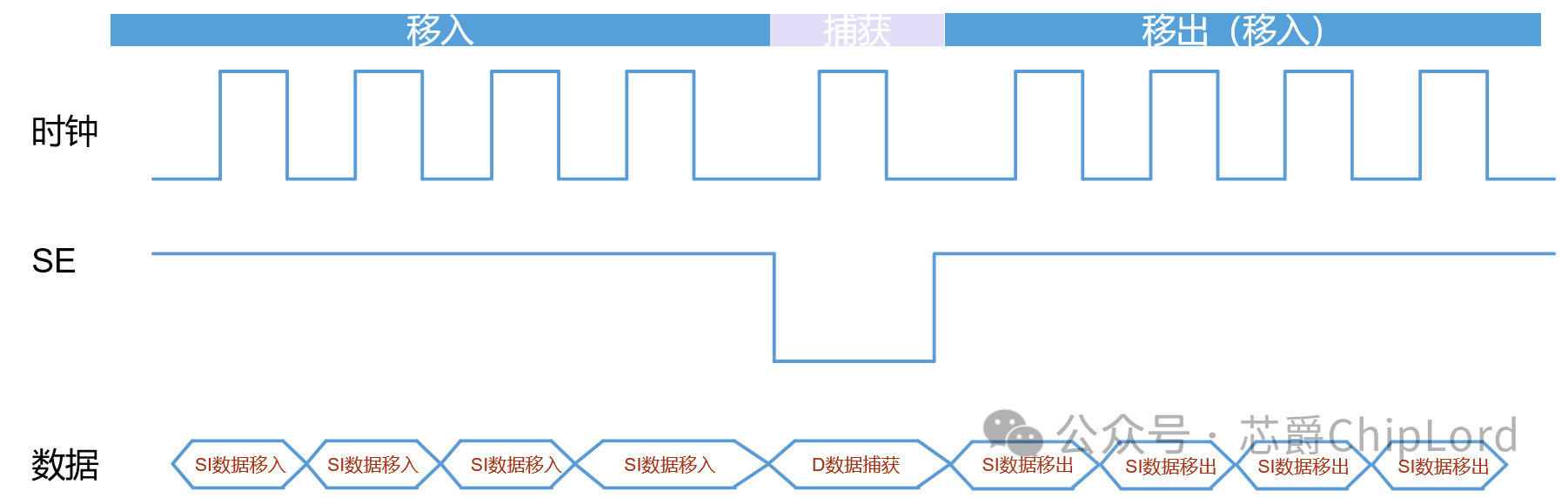

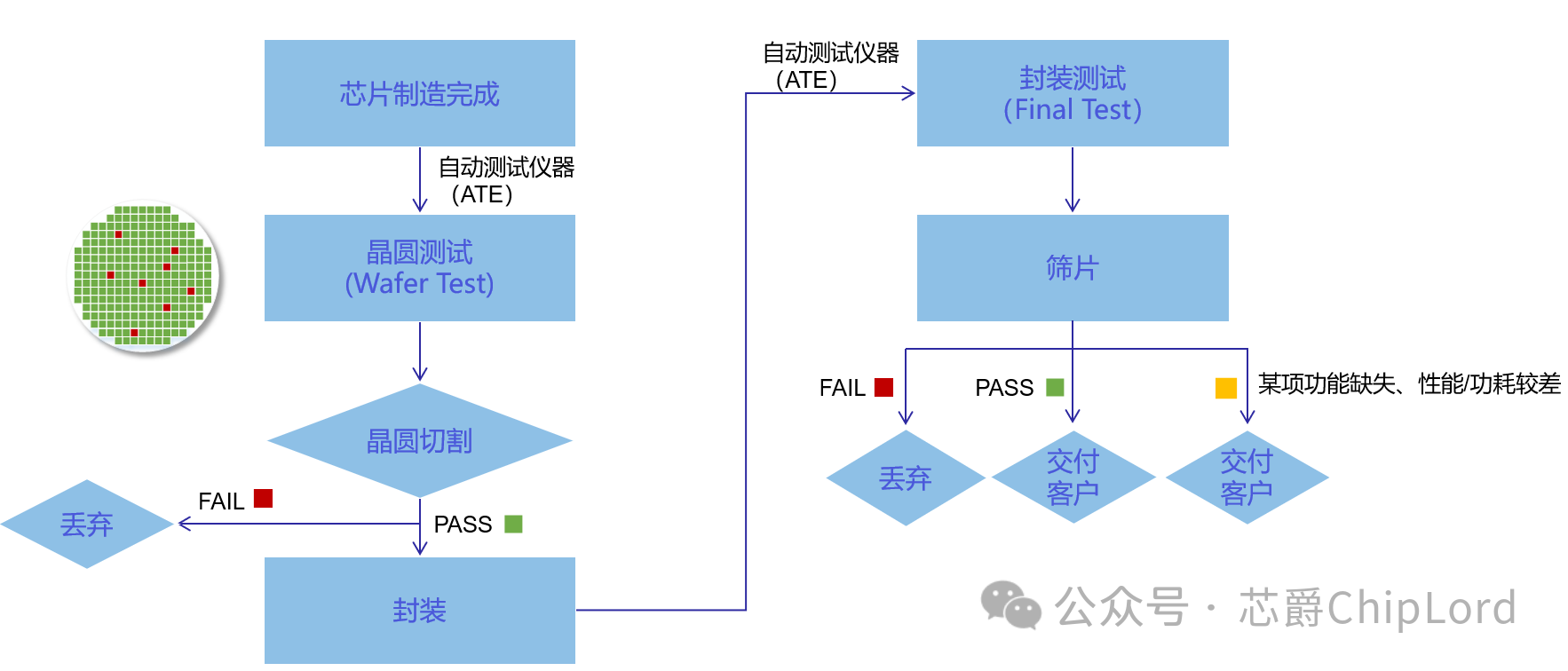

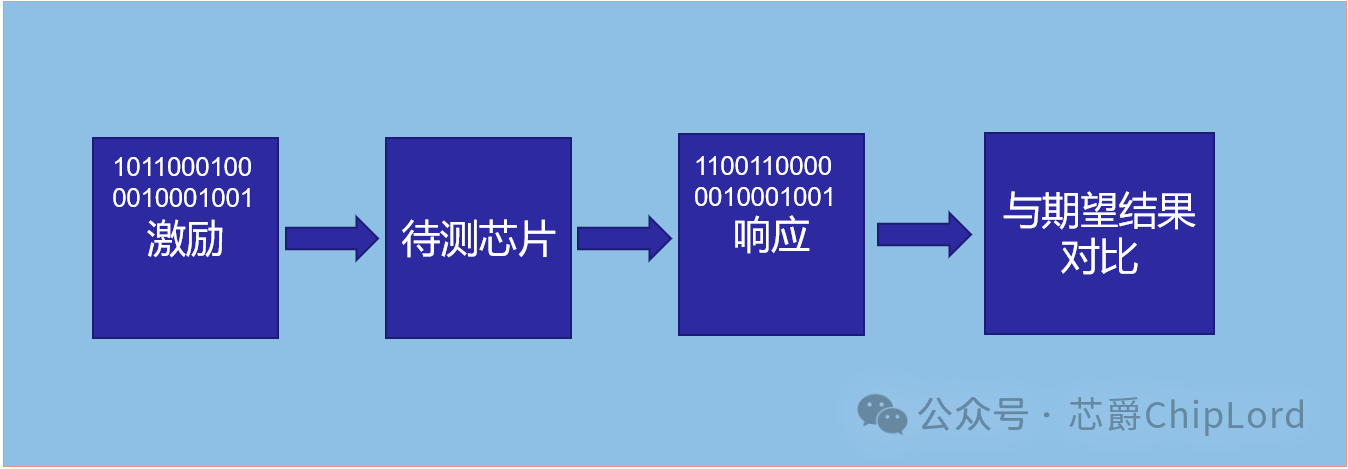

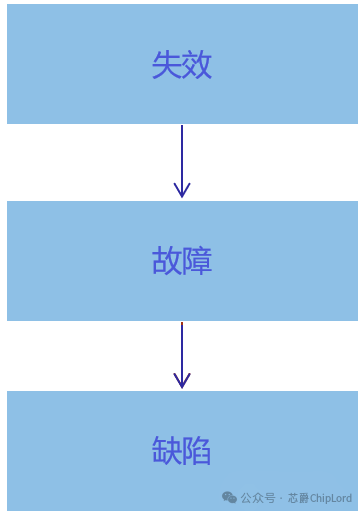

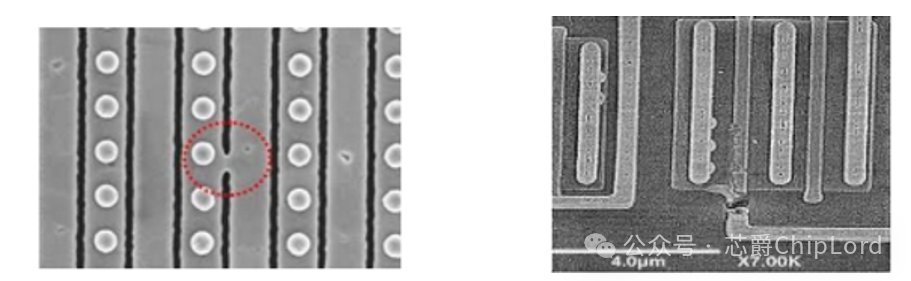

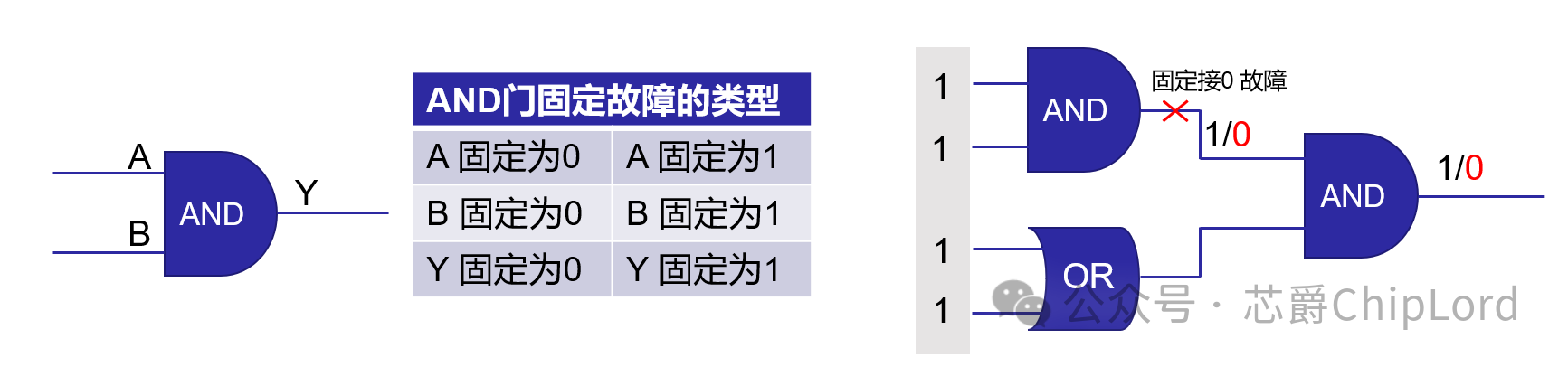

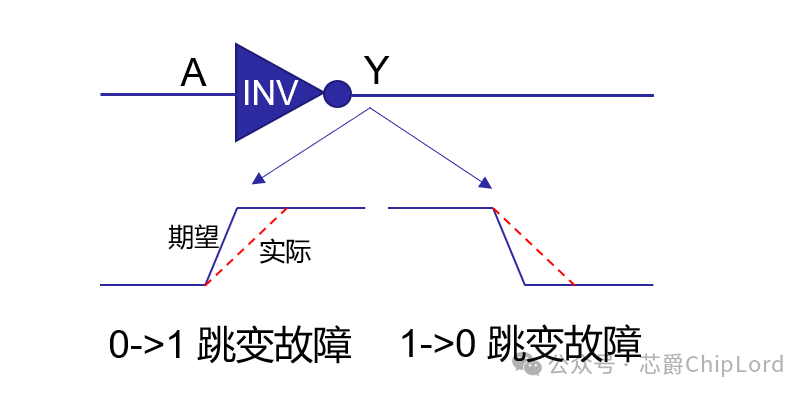

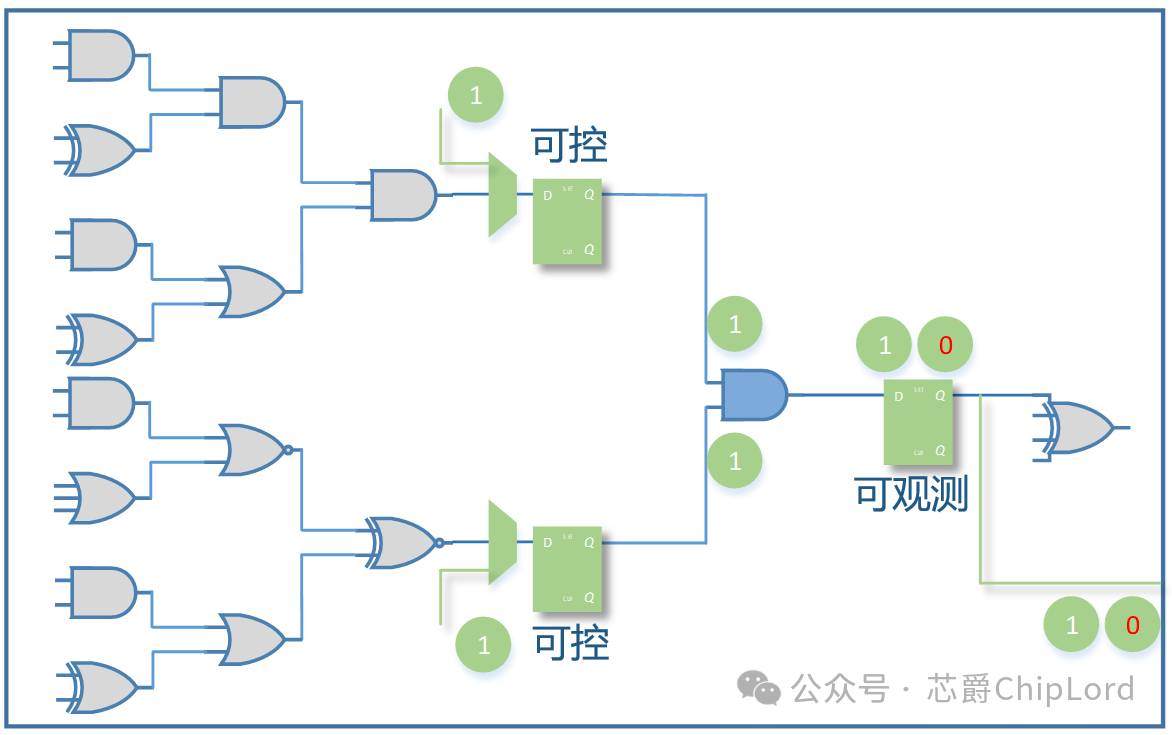

随着芯片技术的不断进步,集成电路的复杂度和逻辑门数量急剧增加,如何确保每个芯片在制造过程中能够正常工作,成为了一个重要的课题。今天,我们将探讨芯片测试中的关键概念——可测性设计(Design for Testability, DFT),以及其在芯片制造和功能验证中的重要作用。 一、测试的基本概念芯片测试是通过在芯片输入端施加已知的激励信号,并观察输出端的响应,来判断芯片是否存在故障。通过将实际输出与期望输出进行对比,可以发现芯片中的缺陷。 测试的分类1. 制造测试(Manufacturing Test):在芯片出厂前进行的一系列结构化测试,主要用于筛选出由于工艺缺陷导致的废片。这包括晶圆测试和封装测试。制造测试的目的是确保每个出厂的芯片都符合设计规范,具有高可靠性。2. 功能测试(Functional Test):作为对芯片功能验证的延续,功能测试主要用于确保芯片在实际应用中的正确性。通过将不同的验证用例施加在芯片上,检查芯片设计是否100%正确。 二、缺陷、故障和失效在芯片制造过程中,可能会出现各种物理缺陷,这些缺陷会导致芯片在电气性能上的故障,最终可能会导致芯片失效。  1. 缺陷(Defect):由于制造工艺的偏差导致芯片元件(如晶体管或互连线)的物理问题。常见的缺陷包括互连线的桥接或断路、CMOS晶体管的栅氧短路、掩膜光刻错误和硅片缺陷等。  2. 故障(Fault):缺陷引起的电气表现形式。故障可以被转换为各种模型,方便软件计算。常见的故障模型有: .固定故障(Stuck-At Fault):例如,门级逻辑的引脚端口或互联线短路到VDD或GND。  跳变故障和路径延时故障(Transition/Path Delay Fault):门级端口的慢升慢降和关键时序路径的延时超过设计允许的范围。  静态电流型故障(IDDQ Fault):导致非常高的静态电流泄露。  3.失效(Failure):如果故障能向后传播并被观测到,导致芯片行为不符合预期,这种现象称为失效。并不是所有的故障都会导致失效,只有那些影响芯片功能的故障才会导致失效。 三、可测性设计的概念随着集成电路复杂度的增加,如何有效地测试芯片成为了一大挑战。可测性设计旨在提高芯片的测试效率和可行性,通过增强芯片的可控性和可观测性来实现。 怎样使设计具有可测性?1. 可控性(Controllability):确保测试时能够方便地施加激励信号到需要测试的逻辑门上。通过设计使得内部节点可以通过外部输入信号进行控制。2. 可观测性(Observability):确保测试响应能够被容易地观测到。设计中增加观测点,使得内部信号可以通过外部输出进行监测。 .

|