|

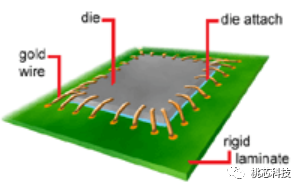

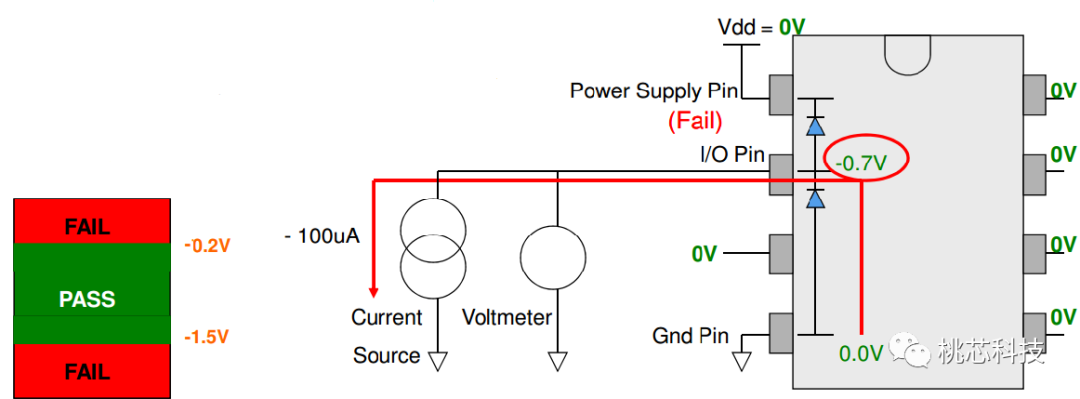

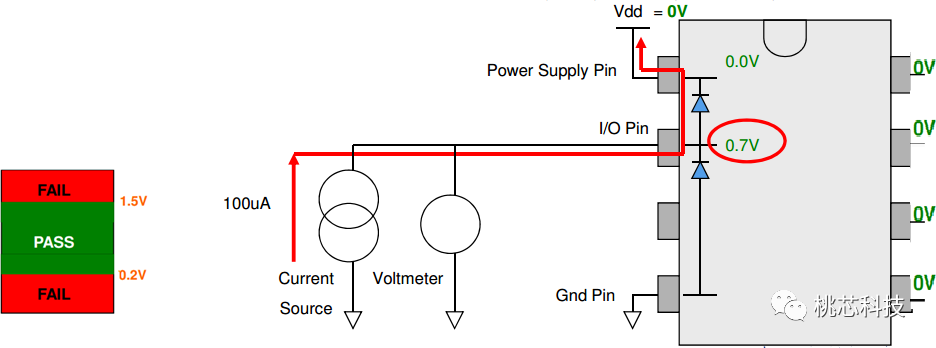

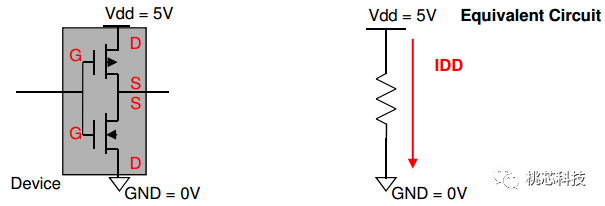

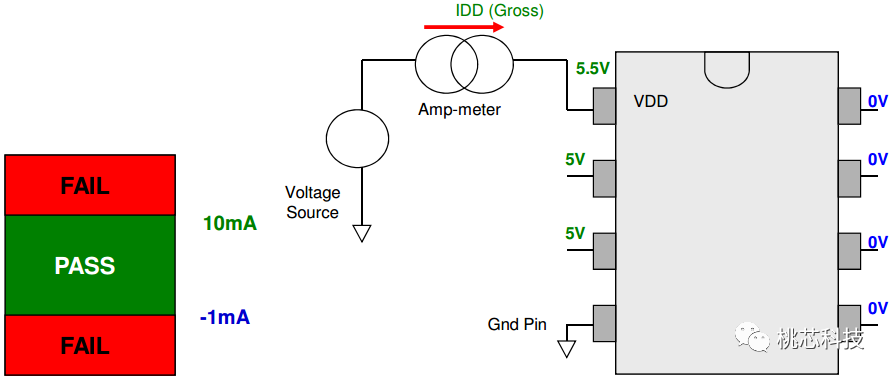

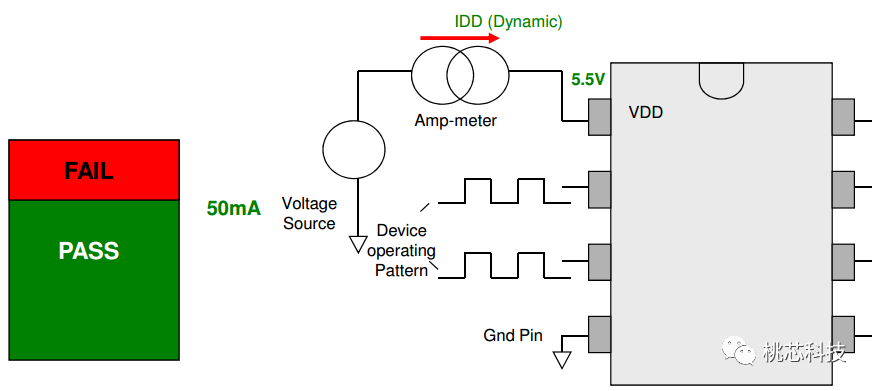

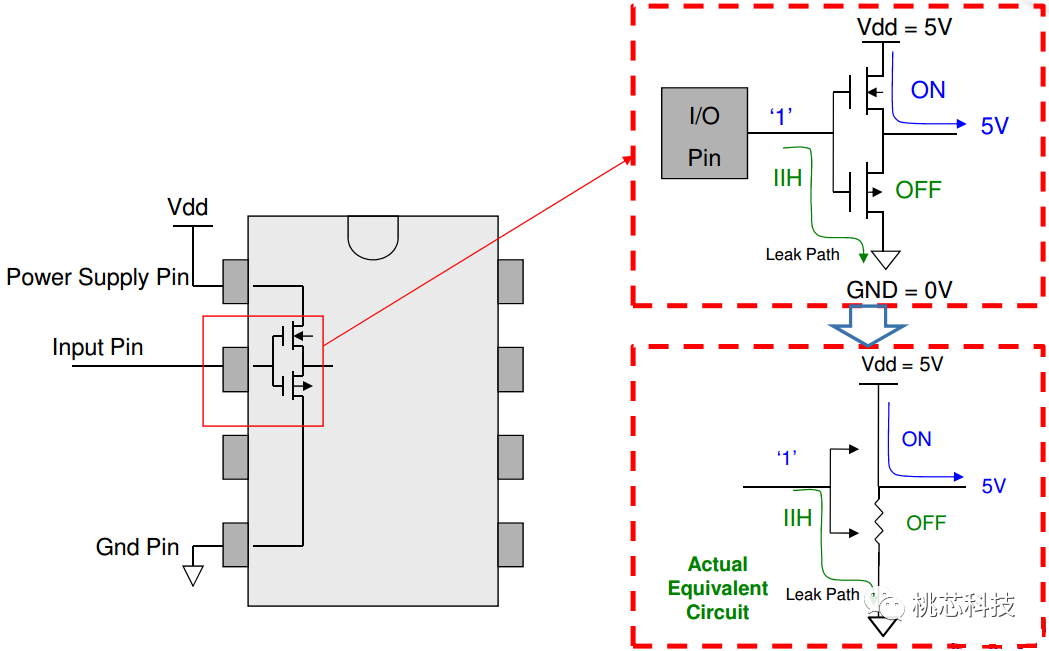

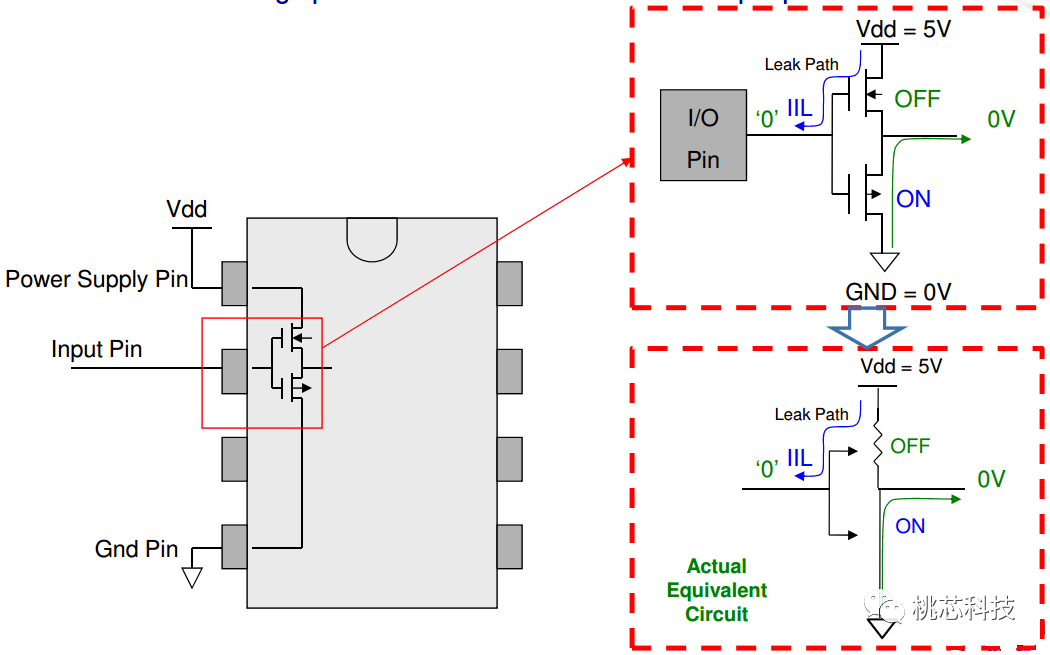

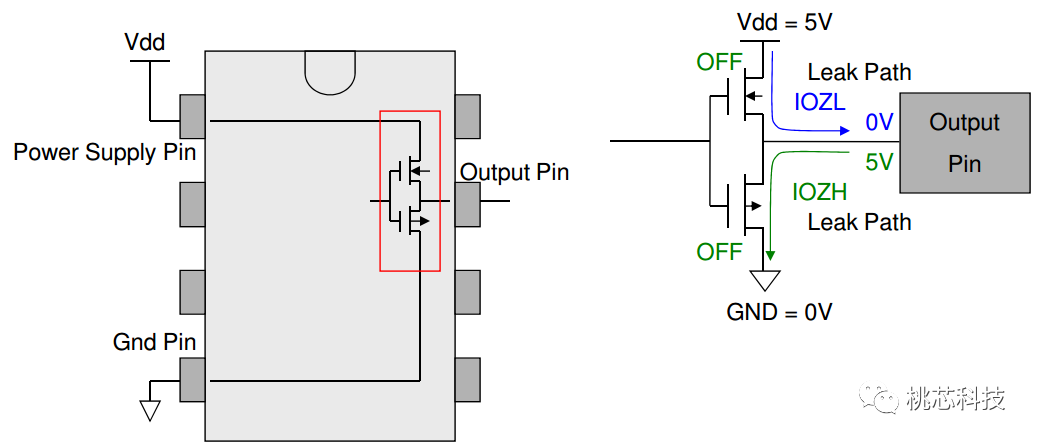

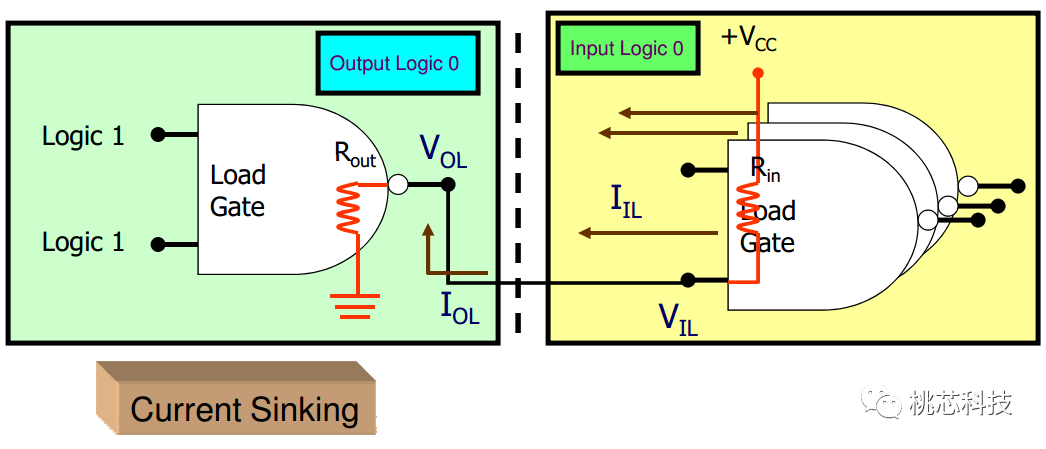

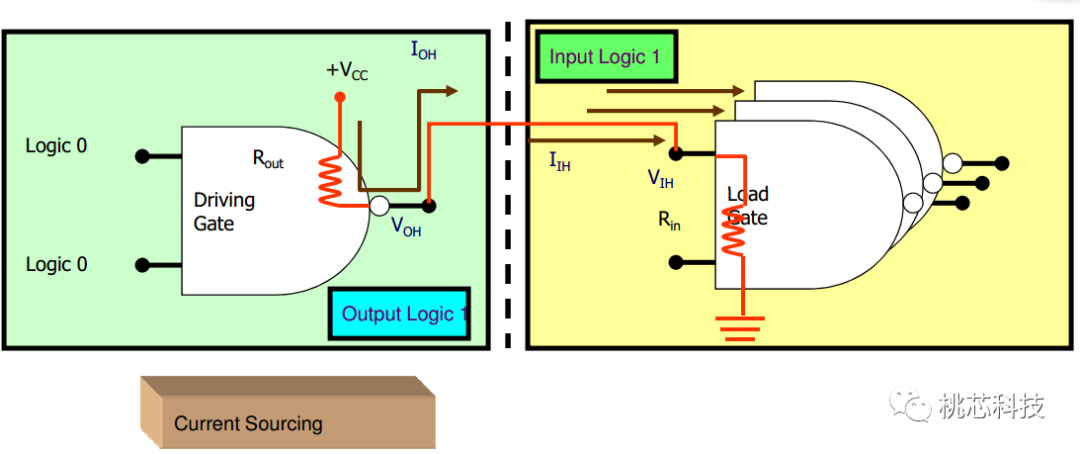

3、其它的Hardware测试介绍 连通性测试介绍 连通性测试是测试芯片的管脚是否有确实连接到测试机之上,芯片的管脚之间是否有短路的一种测试, 通常情况下,这项测试会放在第一项进行,因为连通性测试可以很快发现测试机的setup问题,以及芯片管脚开短路的问题,从而在第一时间发现bad dut,节省测试成本。 如下图(17)所示的一个封装芯片的剖面图,造成连通性失效主要有这几个原因:a) 制造过程中的问题,引起某些pin脚的开短路。b) 封装中的missing bonding wires,会造成开路。c) 静电问题,造成某个pin被打坏从而造成开短路问题。d) 封装过程中造成的die crack或者某个pin脚的弯曲。  图(17) 图(17)这个测试主要是去测试pin的ESD保护二极管。一般情况下,会把open/short测试放在一个项目里同时测试,也有情况是需要分开测试这两个项目。 测试某个pin到ground/其它pin之间的连通性,如下图(18),  图(18) 图(18)Step1: 所有不测试的pin都置0v。Step2: 在需要测试的pin上source一个-100uA的电流。Step3: 量测这个在测试的pin上的电压 --如果tester与这个测试pin接触很好,并且这个pin本身没有任何的开路或者短路到VDD/ground/其它的pin脚上,那么理想的测试到的电压会是-0.7v。--如果这个在测试的pin有开路的fault,会量测到一个大的负电压。--如果这个在测试的pin有短路到vdd/ground/其它的pin上,会量测到一个接近0v的电压。 考虑到实际的电路的情况,一般limit设置为-1.5V ~-0.2V。 测试某个pin到VDD/其它pin之间的连通性,如下图(19)  图(19) 图(19)Step1: 所有不测试的pin都置0v。Step2: 在需要测试的pin上source一个100uA的电流。Step3: 量测这个在测试的pin上的电压。 --如果tester与这个测试pin接触很好,并且这个pin本身没有任何的开路或者短路到VDD/ground/其它的pin脚上,那么理想的测试到的电压会是0.7v。--如果这个在测试的pin有开路的fault,会量测到一个大的正电压。--如果这个在测试的pin有短路到vdd/ground/其它的pin上,会量测到一个接近0v的电压。 考虑到实际的电路的情况,一般limit设置为0.2V~1.5V。 DC参数测试(DC Parameters Test) DC参数的测试,一般都是force电流测试电压或者force电压测试电流,主要是测试阻抗性。一般各种DC参数都会在datasheet里面标明,测试的主要目的是确保delivery的芯片的DC参数值符合规范。 IDD测试 IDD测试(或者叫做ICC测试),在CMOS电路中是测试Drain to Drain的流动电流的,在TTL电路中是测试Collector to Collector的流动电流。如下面图(20)所示:  图(20) 图(20)Gross IDD/ICC Test (power pin short test) 电源pin的短路测试,通常Open/short测试后马上进行,如果在制造过程中有issue,导致了电源到地的短路,会测试到非常大的电流,也会反过来损害到测试机本身。 测试的基本方法如下面图(21)所示  图(21) 图(21)Step1: 给VDD上最高电压,并且tester的电压源设定一个钳制电流,防止电流过大损测试机。Step2: 所有的输入pin置高,所有的输出pin置0. 等待5~10ms。Step3: 量测流过VDD上的电流,正向或者反向电流过高都说明电源到地短路了。 Static IDD/ICC Test (静态功耗测试) 这个项目是测试当芯片在静态或者idle state的情况下,流过VDD的漏电,这个参数对低功耗应用场景特别重要;这项测试也能检测出一些在制造中产生的margin defect,这些defect非常有可能会给芯片带来潜在的可靠性风险。测试方法与下面图(22)所示  图(22) 图(22)Step1: 给VDD上最高电压,并且tester的电压源设定一个钳制电流,防止电流过大损测试机。Step2: 跑pre-condition pattern,把芯片设置到低功耗状态。等待5~10ms。Step3: 量测流过VDD上的电流,根据datasheet中的标识设定limit,超过limit即表示坏品。 Dynamic IDD/ICC Test (动态功耗测试) 这个项目是测试当芯片在不停地运行某种function的情况下,流过VDD的电流。这个类似于某种工作情况下的功耗,需要meet产品spec中的值,对于功耗要求严格的应用方案,此项指标非常重要。测试方法如下面图(23)所示:  图(23) 图(23)Step1: 给VDD上最高电压,并且tester的电压源设定一个钳制电流,防止电流过大损测试机。 Step2: 让芯片持续不断的运行特定的pattern,等待5~10ms。Step3: 量测流过VDD上的电流,根据datasheet中的标识设定limit,超过limit表示坏品。 Leakage测试 芯片内部晶体管不可能在理想的状态,因此或多或少会存在一定的漏电流,需要测试漏电,保证漏电是在正常的允许的范围内,而不是潜在的defect。 Input Leakage Test(IIH and IIL) IIH是当芯片的某个input pin被设定为输入VIH时,从这个input pin到芯片的ground之间的漏电流,如下图(24)所示  图(24) 图(24)IIL是当芯片的某个input pin被设定为输入VIL时,从芯片的VDD 到这个input pin的之间的漏电流,如下图(25)所示  图(25) 图(25)Output Tristate Leakage Test(IOZL and IOZH) Tristate表示的是输出pin是高阻状态,当这个时候,如果输出pin上有电压VDD,那么从输出pin到芯片的ground上会有漏电(IOZH);如果输出pin接地,那么从芯片的VDD到这个输出pin上也会有漏电(IOZL),如下面图(26)所示,这些漏电必须保持在spec规定的范围内,以确保芯片的正常工作,不会有潜在的defect产生。  图(26) 图(26)Output Logic Low DC Test(VOL/IOL) VOL表示的是当输出pin为状态low的时候的最大电压,IOL表示的是在此种状态下这个输出pin的最大的电流驱动能力,这个项目是测试当此状态下的输出pin对地的电阻大小,如下面图(27)所示。  图(27) 图(27)Output Logic High DC Test(VOH/IOH) VOH表示的是当输出pin为状态high的时候的最小电压,IOH表示的是在此种状态下这个输出pin的最大的电流驱动能力,这个项目是测试当此状态下的芯片的VDD到这个输出pin的电阻大小,如下面图(28)所示。  图(28) 图(28)随着芯片工艺越来越先进,晶体管密度越来越高,芯片测试的复杂度和难度也成倍地增长。本文通过各种失效模式及检测机理的讨论,梳理了一下基本的测试概念。后续我们会再针对混合信号测试、RF测试、DFT测试进行一些探讨,谢谢! |