|

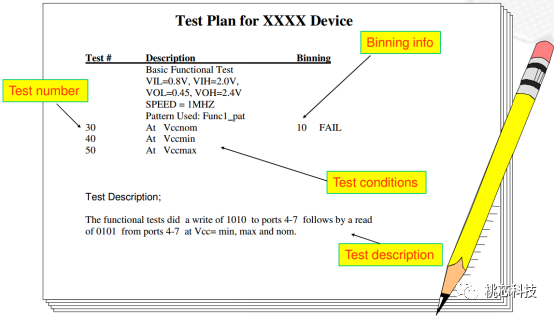

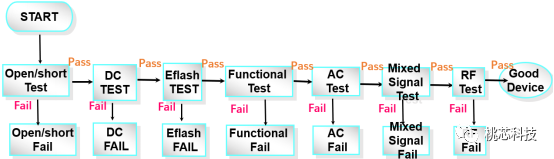

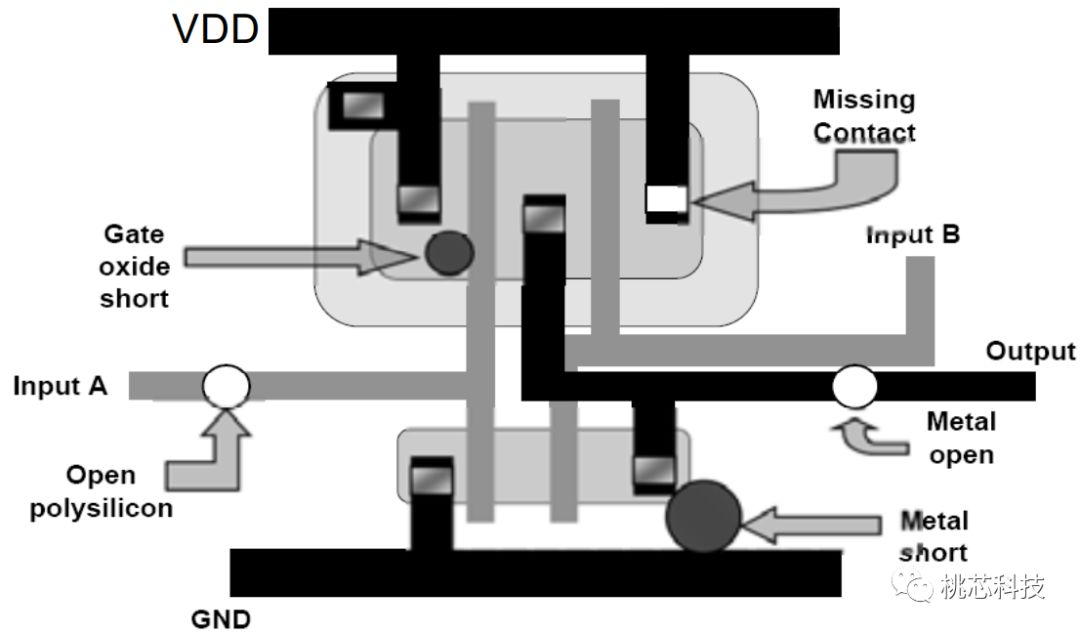

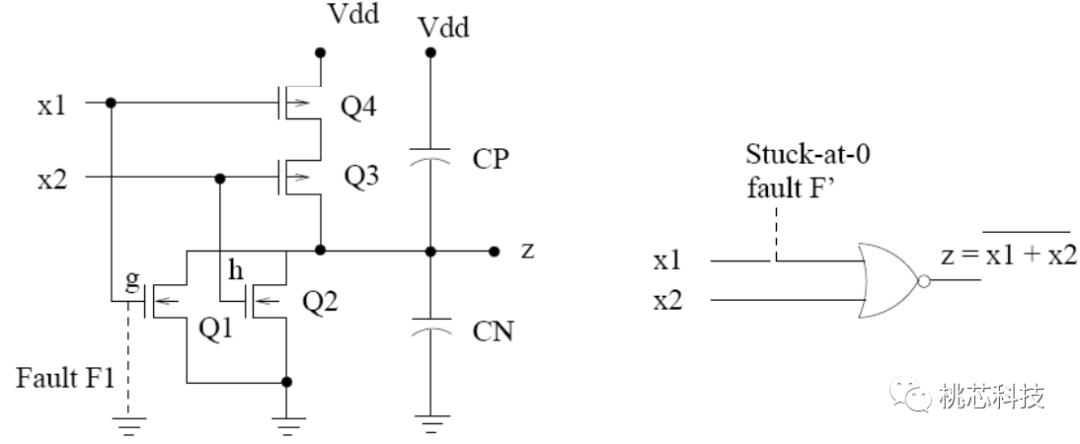

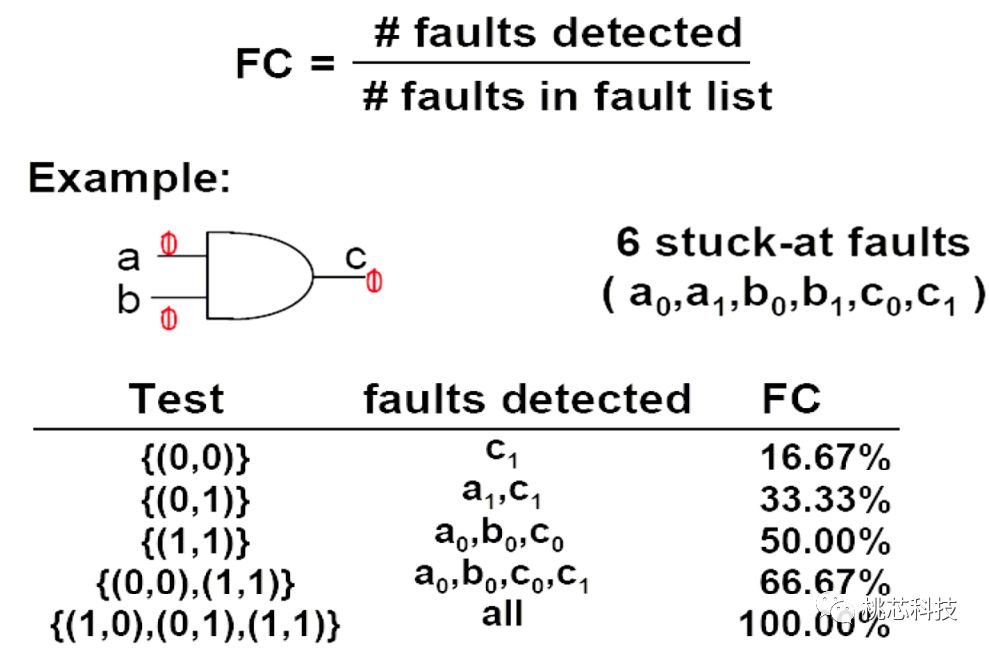

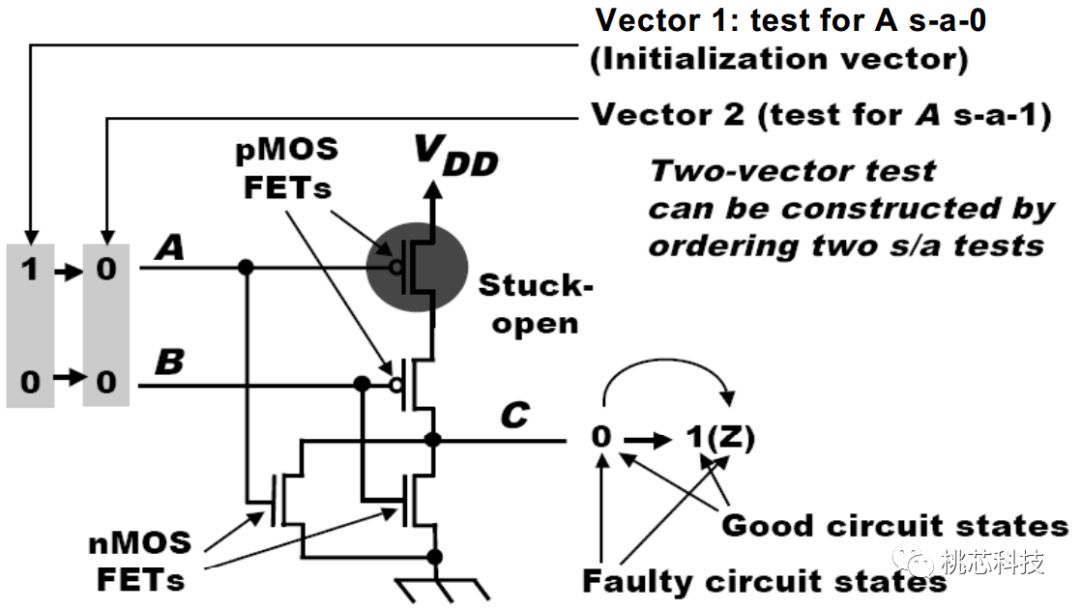

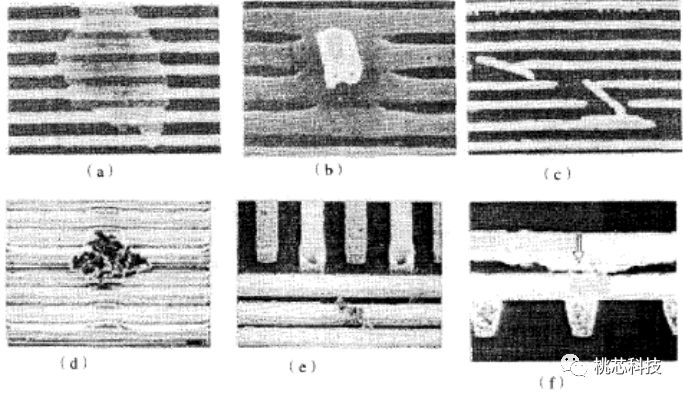

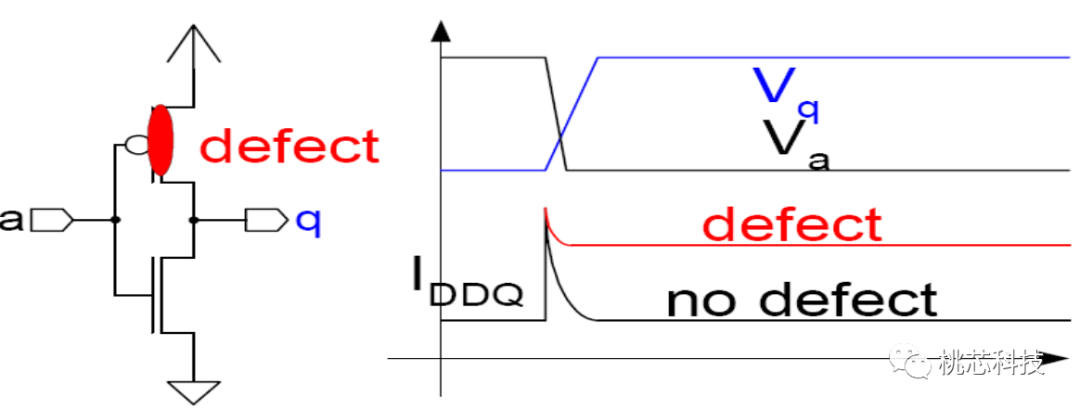

4、如何进行一个产品的测试开发 各种规格书:通常有三种规格书,设计规格书、测试规格书、产品规格书。 设计规格书,是一种包含新电路设计的预期功能和性能特性的定义的文档,这个需要在设计项目启动阶段就要完成,通常由市场和设计人员共同完成,最终设计出来的产品的实际功能和性能需要和设计规格书的规定进行比较,以确认本次设计项目的完成度。 测试规格书,其中包含详细的逐步测试程序、条件、方法,以充分测试电路,通常由设计人员和产品验证工程师在设计过程中完成。产品规格书,通常就是叫做datasheet,由设计公司对外发布的,包含了各种详细的规格、电压、电流、时序等信息。 测试计划书:就是test plan,需要仔细研究产品规格书,根据产品规格书来书写测试计划书,具体的需要包含下面这些信息: a)DUT的信息,具体的每个pad或者pin的信息,CP测试需要明确每个bond pads的坐标及类型信息,FT测试需要明确封装类型及每个pin的类型信息。b)测试机要求,测试机的资源需求,比如电源数量需求、程序的编写环境、各种信号资源数量、精度如何这些,还需要了解对应的测试工厂中这种测试机的数量及产能,测试机费用这些。 c)各种硬件信息,比如CP中的probe card, FT中的load board的设计要求,跟测试机的各种信号资源的接口。 d)芯片参数测试规范,具体的测试参数,每个测试项的测试条件及参数规格,这个主要根据datasheet中的规范来确认。类型与下面图(8)这样  图(8) 图(8)e)测试项目开发计划,规定了具体的细节以及预期完成日期,做到整个项目的可控制性和效率。 测试项目流程:桃芯科技目前量产的是BLE的SOC产品,里面包含了eflash、AD/DA、 LDO/BUCK、RF等很多模块,为了提供给客户高品质的产品,我们针对每个模块都有详细的测试,下面图(9)是我们的大概的项目测试流程:  图(9) 图(9)Open/Short Test: 检查芯片引脚中是否有开路或短路。 DC TEST: 验证器件直流电流和电压参数 Eflash TEST: 测试内嵌flash的功能及性能,包含读写擦除动作及功耗和速度等各种参数。 Function TEST: 测试芯片的逻辑功能。 AC Test: 验证交流规格,包括交流输出信号的质量和信号时序参数。 Mixed Signal Test: 验证DUT数模混合电路的功能及性能参数。 RF Test: 测试芯片里面RF模块的功能及性能参数。 上面我们给大家介绍了芯片的测试目的,原理,以及方法和流程,接下来我们将比较详细的给大家介绍芯片的错误类型,对应的测试策略,以及跟芯片整体质量相关的一些具体测试方法。 1、半导体芯片的defects、Faults 芯片在制造过程中,会出现很多种不同类型的defects,比如栅氧层针孔、扩散工艺造成的各种桥接、各种预期外的高阻态、寄生电容电阻造成的延迟等等,如下面图(1)所示,大概展示了各种基本的defects。  图(1) 图(1)这些defects单独、或者组合一起,造成了电路的表现不符预期,这就是造成了Faults.而且各种Faults的表现也是不一样的: 永久的Faults,就是彻底的坏品,各种不同的条件下都会表现出来,易于测试发现。 间或的Faults,时有发生的不符合预期,不是总能发现,需要一定的外部条件刺激。 偶然的Faults,只是偶然的,在特定的外部硬件或者工作模式条件下才表现出来。 可靠性问题的Faults,这种一般不会表现出来,只会在一些极端条件才会表现出来,比如高低温或者偏压情况下。 为了更有效地检测出各种faults、避免浪费更多芯片的资源、节省费用,业界定义了很多种Faults Model,并提供了各种测试方法论。 Stuck At Faults 工艺制造过程中造成的硬件defects,使得某个节点Stuck At 0或者Stuck At 1, 如下面图(2)所示的一个或非门:输入节点x1发生了Stuck At 0的defect; x1和x2输入了00时候,Q1和Q2断开,Q3和Q4导通, z输出为H,正确;x1和x2输入了01时候,Q1和Q3断开,Q2和Q4导通, z输出为L,正确;x1和x2输入了10时候,此时x1被Stuck At 0了,等同于输入00,结果还是Q1和Q2断开,Q3和Q4导通,z输出为H,错误;至此,通过输入00,01,10就发现了这个defect。这种顺序输入00,01,10,而比较z输出的结果与预期的值进行判断的方法,就是所谓的Function测试。  图(2) 图(2)那对于一个电路,需要生成多少pattern,能达到多少的测试覆盖率呢?下面图(3)就以一个与门为例,说一下生产测试向量及计算测试覆盖率的基本理念。  图(3) 图(3)如上面图示,一个与门,有三个节点a、b、c, 每个节点都有两种fault的情况(Stuck At 0或者1),那么一共就有6种stuck-at faults情况:a0,a1,b0,b1,c0,c1. 那么如上面图中列出的,需要输入(1,0),(0,1),(1,1)可以完全测试出所有的6种可能的Stuck-at Faults的情况,测试覆盖率为:可以发现的faults/所有可能的Faults,上面的输入的测试覆盖率为100%。 Stuck Open(off)/Short(on) Faults 制造过程种造成的晶体管的defects,使得某个晶体管常开或者常闭了,如下面图(4)所示的时一个晶体管发生了Stuck Open(off)的错误了。  图(4) 图(4)如上图,这种Stuck open可以用两组Stuck At的向量进行测试,AB输入从10变换到00,可以检测出这种Stuck Open的fault,也就是说大部分的Stuck Open/Short的faults都是可以通过Stuck At model的测试向量覆盖的。 这种通过向量(function)的方式来测试Stuck Open/short,可能需要非常多的测试图形,需要的测试时间和成本都很多。还有一种测量电流的方式,也可以有效的测试一些这种Stuck open/short的faults,但是会节省很多测试时间和测试成本。 如下面图(5)上半部分所示,右边的那个P沟道MOS管发生了Stuck short(on)的faults,图的下半部分展示了输入AB的四种不同的情况,当AB输入为00时,看起来这个晶体管表现的正常;但是当AB输入为11时,地和电源间存在一个直接导通的电路,输出端Z的状态是异常的。  图(5) 图(5)此时VDD上的漏电比较大,也可以通过测量VDD上面的电流来判断正误,即IDDQ的测试方法,后面会详细的介绍这种方法。 桥接(Bridge Faults) 桥接缺陷是由于电路中两个或多个电节点之间短路造成的,而设计中并未设计这种短接。这些短接的节点可能是某一个晶体管的,也可能是几个晶体管之间的,可能处于芯片上同一层,也可能处于不同层。下面图(6)是桥接缺陷的几种图例。  图(6) 图(6)上图中,(a)是因曝光不足导致7条金属线桥接子在一起的情形;(b)是外来颗粒的介入导致4条金属线桥接在一起的情形;(c)是因掩模划伤导致桥接的情形;(d)是1um大小的缺陷造成短路的情形;(e)是金属化缺陷导致2条金属线桥接的情形;(f)则是层间短路情形。上述情形中虽然导致缺陷的原因各有不同,但结果都是桥接。 同样的,桥接测试也可以通过电压的方法完成,即run pattern方式,也就是stuck at的模式进行检测,但是电流测试是发现电压测试无法检查的故障的有效方法。 下面图(7)表示的是mos管的source和drain桥接了。  图(7) 图(7)上面图中,因为上面的P沟通的MOS管的source和drain桥接了,电源VDD上会有很大的漏电,用电流测试方法,可以很快发现问题。 |