|

dft是什么 可测试性设计(Design for Testability)是一种集成电路设计技术。它是一种将特殊结构在设计阶段植入电路的方法,以便生产完成后进行测试,确保检测过后的电子组件没有功能或制造上的缺陷。 电路测试有时并不容易,电路的许多内部节点信号在外部难以控制和观测。通过在半导体工艺中添加可测试性设计结构,如扫描链等,并利用自动测试设备执行测试程序,可以在生产完成后立即进行质量检测。有些特定的设备会在其最终产品的组件上加上测试功能,在消费者的使用环境下执行时一并测试。测试程序除了会指出错误信息外,还会一并将测试的日志保留下来,可供设计人员找出缺陷的来源。 更简单的说,测试程序会对所有的被测设备输入测试信号,并期待它们给出预期的正确回应。如果被测设备的回应与预期回应一致,则可得知电路正常,否则 即为测试错误。 为了方便使用测试程序检测错误,电路设计阶段不可忽视可测试性设计。在可测试性设计的规则确认完善下,可以利用自动测试图样发生器进行更复杂的测试。 function test 与dft的异同

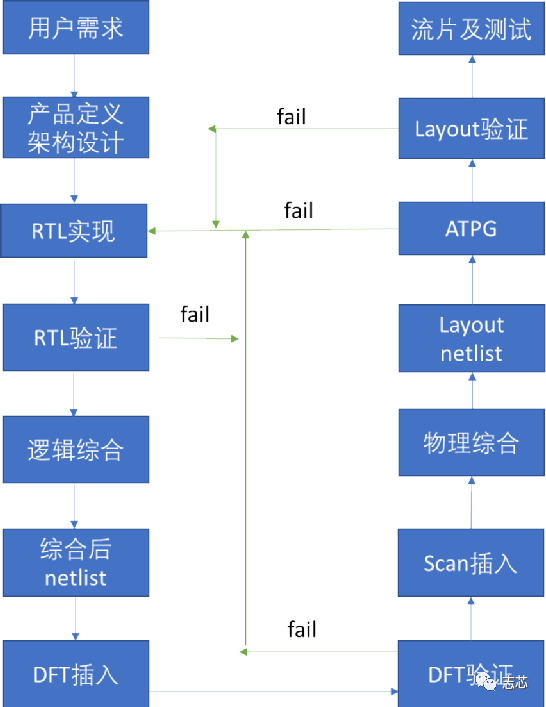

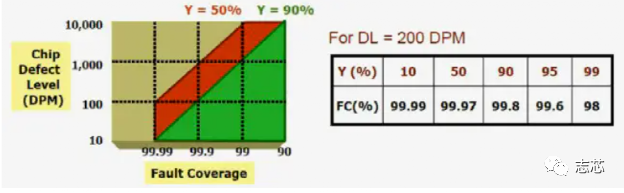

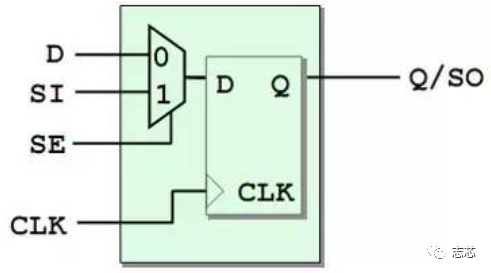

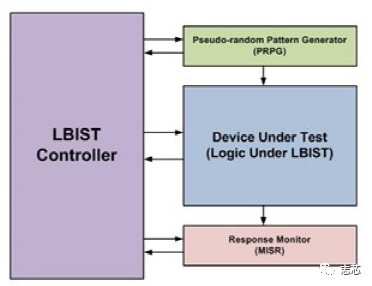

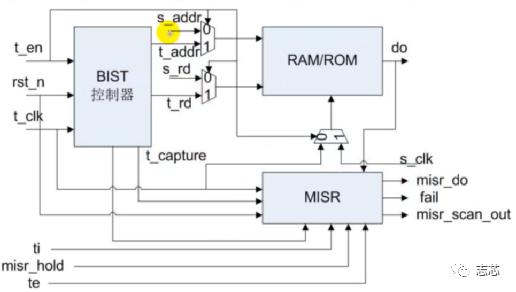

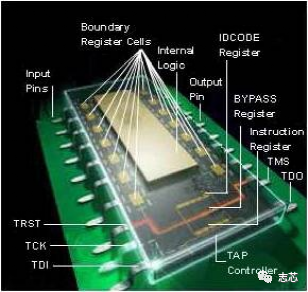

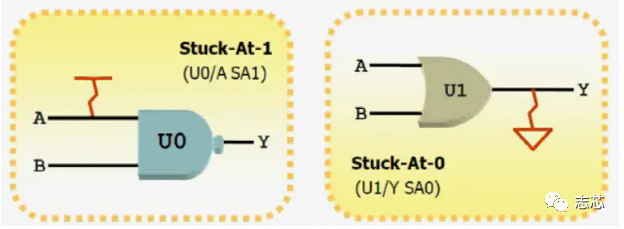

dft设计流程 DFT可以从架构阶段开始引入,在RTL阶段开始DFT设计和验证;也可以在netlist阶段开始插入DFT相关设计。  dft设计的原则 最小化冗余逻辑,最小化异步逻辑,从逻辑电路中隔离时钟,增加内部的控制点和观察点,结构性测试。 dft质量评价 测试后的缺陷率:Defective parts per million(DPM),测试后的缺陷率。 测试覆盖率:Fault coverge(FC)。 缺陷率:Defect level(DL)。对于确定的工艺,DL应是确定的。   图1 由良率可以反推测试覆盖率 图1也可以将上文所述的function test和dft 联系起来。 SOC中不同part的dft method 一般是这样的:标准单元用基于SCAN的测试;储存器与模拟模用BIST测试;硬核软核IP用BIST和SCAN测试;封装与IO用Boundary Scan(JTAG)测试。 scan 通过用一个可扫描的等效物替换设计中所有的存储器元件,然后把这些扫描单元连接为扫描链,利用多个时钟脉冲将特定的输入值一拍一拍打入到扫描链上所有的时序触发器,同时在扫描输出端通过多个时钟脉冲得到这些触发器的测试响应。将得到测测试响应值与工具给定的期望响应值对比可以帮助快速找到发生缺陷的位置,实现对量产芯片的筛选。这一方法通过控制和观察设计中所有存储元件的值,从而使得时序电路的测试向量生成和仿真变得和组合逻辑一样简单。 四位移位寄存器的原理图如图2所示。FF0、FF1、FF2、FF3是四个边沿触发的D触发器,每个触发器的输出端Q接到右边一个触发器的输入端D。因为从时钟信号CP的上升沿加到触发器上开始到输出端新状态稳定地建立起来有一段延迟时间,所以当时钟信号同时加到四个触发器上时,每个触发器接收的都是左边一个触发器中原来的数据(FF0接收的输入数据D1)。寄存器中的数据依次右移一位。  图2 D触发器组成的四位移位寄存器 Scan Chain将芯片中的所应用的普通寄存器替换成带有扫描功能的扫描寄存器,首尾相连成串,从而可以实现附加的测试功能。  图3 扫描寄存器 从图中可以看出,比普通存储器多了SI,SE,SO3个端口。其中SI,SO也就是scan_in与scan_out端,定义了一条scan chain的input和output端。通常情况下,每一个input会驱动一条scan chain,一个ouput也是用来观察一条scan chain的。SE是scan enable信号,它控制着scan cell的工作模式。从图中可以看出,SE,SI,D端通过一个Mux实现工作模式的切换。当SE输入为0时,scan cell工作在普通模式下,相当于是普通的flop;当SE输入为1时,scan cell就进入scan模式,相当于一个移位寄存器。scan cell通常定义在lib库中直接导入。 lbist 设备在现场运行过程中可能会出现一些缺陷。现场故障主要是由于潜在故障,这些潜在故障在制造测试时可能不明显或不易检测,但由于环境条件,可能会在一段时间内或在现场应用中实时演变,并形成真实的defect。 尤其是在汽车和军事应用中使用的 SOC 受到的影响最为严重,因为这些应用中的现场故障可能会危及生命。像老化这样的压力测试虽然提供了一个长期的预测压力模拟环境,但由于涉及高昂的测试成本,这些也仅限于开头几年。为了满足安全要求,应将 SOC 设计为可在现场测试中执行。 Lbist即logic built-in self-test, LBIST是一种BIST)形式,其中硬件和/或软件内置在集成电路中,允许它们测试自己的操作,而不是依赖外部自动化测试设备。LBIST有助于将测试复杂性降低一个数量级。Logic-BIST 是嵌入在芯片中的电路,用于对设计进行基于scan链的结构测试。这种技术可以用最小向量测量故障覆盖率,并帮助我们克服前面讨论的技术的缺点。如图 4 所示,它由测试模式发生器和用于分析功能电路输出响应的电路组成。  图4 SOC 中的 LBIST 电路示意图 mbist MBIST 方法是目前大容量存储器测试的主流技术,该技术利用芯片内部专门设计的BIST 电路进行自动化测试,能够对嵌入式存储器这种具有复杂电路结构的嵌入式模块进行全面的测试。MBIST 电路将产生测试向量的电路模块以及检测测试结果的比较模块都置于芯片的内部,在测试完成后,将测试的结果通过芯片的测试引脚送出到芯片的外部。 MBIST 的核心思想是在芯片内部,存储器外部建立测试电路结构,实现对存储器的读写控制:写入测试向量,读出响应数据。MBIST 电路的基本结构一般包括测试向量产生电路、BIST 控制电路、响应分析电路三部分,结构如图5所示。  图5 mbist示意图 Boundary Scan Boundary Scan是一种用于测试集成电路内部sub chip上的互连(导线)的方法。边界扫描也被广泛用作一种调试方法,用于观察集成电路引脚状态、测量电压或分析集成电路内部的sub chip的状态。 Boundary Scan是一种测试技术,其涉及的器件在每个器件引脚和内部逻辑之间放置了移位寄存器,如图 6 所示。每个移位寄存器称为边界扫描单元。这些边界扫描单元允许我们控制和观察每个输入和输出引脚上发生的情况。当这些单元连接在一起时,它们形成了一个data register chain,称为边界寄存器。  图6 boundary scan示意图 dft中的失效模型 为了检测到芯片电路中的故障,1959年Eldred提出了故障模型的概念,即一个试着捕获物理缺陷对电路行为的逻辑功能的影响的结构模型。从那之后,固定型故障模型被用来生成高效的测试向量集,常用的故障模型分为以下几类:Stuck-At fault model、At-Speed (transition)fault model、Path Delay fault model、IDDQ fault model、Toggle fault model 、N-Detect and Embedded Multiple Detect (EMD) fault model、Deterministic Bridging fault model、Small-Delay Defects fault model等。 其中Stuck-At、At-Speed、Path Delay、IDDQ是常用和常见的几种。 Stuck-At 最基本和最常见的是“Stuck-At”故障模型,它检查设计中每个节点位置的“Stuck-At 1 ”或“Stuck-At 0”的逻辑行为。例如,如果设计中的 NAND 门有一个输入引脚因缺陷而对地短路(逻辑值 0),则该节点的stuck-at-0 test将捕获它。Stuck at模型还可以检测其他缺陷类型,例如两个网络或节点之间的桥接。Stuck at0归类为静态模型,因为它是一种慢速测试,并且不依赖于 时序(上升和下降时间以及传播延迟)。  图7 stuck at模型示意图 At-Speed(transition) 第二种常见的故障模型称为“at-speed”或“transition”故障模型,它是一种动态故障模型,即它检测时序问题。它与固定模型相似,因为设计中的每个节点位置都有两种故障,分类为slow-to-rise 和 slow-to-fall faults故障。transition fault model使用创建transition stimulus 的测试模式来将逻辑值从 0 更改为 1 或从 1 更改为 0。指定了转换允许的时间,因此如果转换没有发生,或者发生在分配的时间之外,则假定存在时序缺陷。 path delay “path delay”模型也是动态的,并在目标时序关键路径上执行全速测试。虽然stuch at和transition故障模型通常解决设计中的所有节点,但路径延迟模型仅测试工程师指定的确切路径,工程师运行静态时序分析以确定哪些是最关键的路径。这些路径指定给 ATPG 工具,用于创建路径延迟测试pattern。该理论是,如果最关键的时序路径能够通过测试,那么具有较大的timing margin的所有其他路径应该没有时序问题。在某种程度上,“path delay测试是一种过程检查形式(例如,如果过程变量偏离太远,则显示时序错误),此外还可以测试单个设备的制造缺陷。 IDDQ IDDQ 测试依赖于测量静态状态下的电源电流 (Idd)(当电路未切换且输入保持在静态值时)。测试模式用于将 DUT 置于各种选定状态。通过在每个静态状态下执行电流测量,可以检测到是否存在消耗过电流的缺陷。Iddq 测试的价值在于可以用很少的pattern测到许多类型的故障。缺点是执行电流测量需要额外的测试时间。 ATPG ATPG(auto test pattern generate)是一种用于查找输入或测试序列的 EDA 方法/技术。当应用于数字电路时,ATPG 使自动测试设备能够区分正确的电路行为和由缺陷引起的错误电路行为。生成的图案用于在制造后测试半导体器件,或帮助确定故障原因。ATPG 的有效性通过可检测的建模缺陷或故障模型的数量以及生成模式的数量来衡量。这些指标通常表明测试质量(更高的故障检测)和测试应用时间(更高的模式)。ATPG 效率是另一个重要的考虑因素,它受所考虑的故障模型、被测电路的类型(全扫描、同步顺序或异步顺序)、用于表示被测电路的抽象级别(门、寄存器-传输、切换)和所需的测试质量。  图8 atpg说明示意图 如图8所示,如果输入A stuck-at 1。 设正常状态下,Y的输出值为h(t)=(A.B)’=(A’)+(B’); 当A stuck-at 1时,此时假设Y的输出值为hu(t)=(1.B)’=0+(B’); 如果有一对输入A和B使得h(t)和hu(t)为不同值,那么就能观测得到输入pin A stuck-at 1的缺陷。 所以ATPG的本质是解这么一个逻辑方程: h(t)’.hu(t)+h(t).hu(t)’=1(即h(t) 和hu(t)异或为1). |