|

这篇文章主要讲一下基于扫描路径的可测性设计。

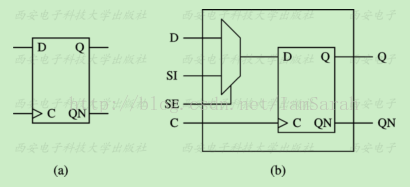

对于一个组合逻辑的电路,电路中的故障可以通过输入端口施加向量进行激励。而对于一个复杂、端口有限的时序电路,只能采用基于扫描路径的可测性设计方法来实现对电路的可控制性和可观测性。在该方法中首先需要将非扫描单元如寄存器用扫描单元取代,如下图所示:

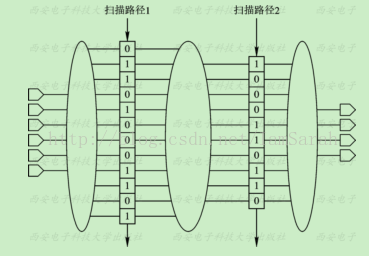

这种结构非常简单,但却非常巧妙。当电路中的寄存器用扫描寄存器取代以后,在扫描模式下,电路中的时序路径可以变成下图的结构。这样组合逻辑的输入激励可以通过输入端口及扫描寄存器来输入,组合逻辑的输出可以通过扫描寄存器移出到输出端口,从而实现激励的施加和响应的捕获。

下面对这一过程进行详细说明:

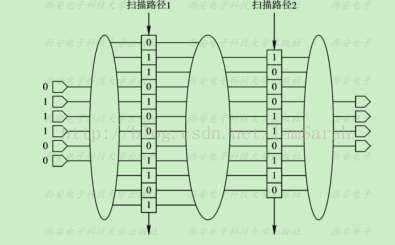

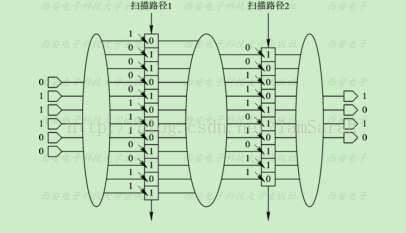

1)通过扫描链将激励输入,即扫描移进,如图所示:

2)通过输入端口施加激励

3)测试输出端口响应

4)将组合逻辑的输入捕获进扫描链寄存器

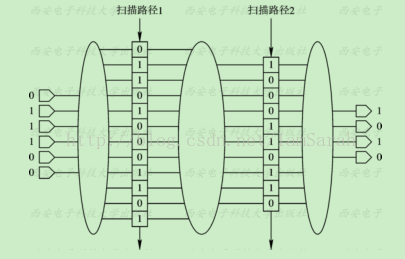

5)通过扫描链将捕获的响应输出,即扫描移出。测试仪要探测扫描端口的输出。在扫描移出的时候可以进行下一次的扫描移进。

下面对扫描路径测试的原理进行一下总结:

1)将1和0组成的向量移到扫描链中。这些移入的向量将设计中的寄存器初始化为已知的值。

2)将组合逻辑的输出捕获进扫描寄存器。

3)将捕获结果移出,并进行检查。若期望结果与实测结果有差,则电路中有一个固定故障。

这个过程会持续进行,直到所有的可能激励被测试。

面向扫描测试RTL设计:

在进行扫描测试时,测试模式信号要外部pin提供,例如复位信号,使能信号,时钟信号。则RTL设计要符合可测性设计的要求,如果设计不当,会导致测试无法进行,或者覆盖率较低。现在的可测性综合工具如DFT Compiler可以自动对不满足扫描设计要求的逻辑进行修正,但设计者仍要次问题有清楚的了解。下面对可测性设计常见的一些问题进行说明。

可测性设计中常见问题有:

1)设计中用到了时钟的两个边沿:设计中的寄存器最好使用一个时钟沿。如果设计中必须用到两个时钟沿,则最好将不同时钟沿触发的寄存器放入不同的扫描链中。

2)设计中存在多时域:在扫描链上跨时钟域的地方接入锁存器。该锁存器用前一个时钟下降沿进行锁存。

3)有门控时钟:在许多设计中,例如在低功耗设计中, 存在着门控时钟逻辑。而在扫描时,时钟不能被阻断。这时候,需要加入控制逻辑,以避免时钟门控逻辑的影响。

4)由内部生成的时钟信号:在IC系统中,经常会用到内部生成的时钟,例如分频电路。如果内部时钟驱动的寄存器直接接入扫描链中,则寄存器中的时钟信号会是另一些寄存器的数据输出,会在扫描移位的时候出现问题。因此利用MUX,在测试时使用外部引脚输入的时钟。

5)有内部生成的异步复位置位信号:在有些设计中,存在内部生成的异复位、置位信号。如果不对这些信号进行控制,则在扫描过程中,有可能会改变寄存器的状态,从而改变寄存器状态。为避免这种情况应该加入相应的控制逻辑。

6)在扫描模式下,在三态总线上有冲突:全扫描只检查0和1,无法检查高阻。则在扫描的时候可以禁止所有的三态缓冲使能信号,然后通过上、下拉电阻给总线固定的值。但这种方法功耗过大,更常见的方法是在扫描时允许一个三态缓冲器使能。

7)设计中存在锁存器:在扫描时使其保持使能状态,这样锁存器就是透明的。

8)存在存储器这样无法进行扫描测试的电路:扫描中绕开存储器,将其看做一个黑盒子。

9)存在反馈环:设计中避免出现。

|