|

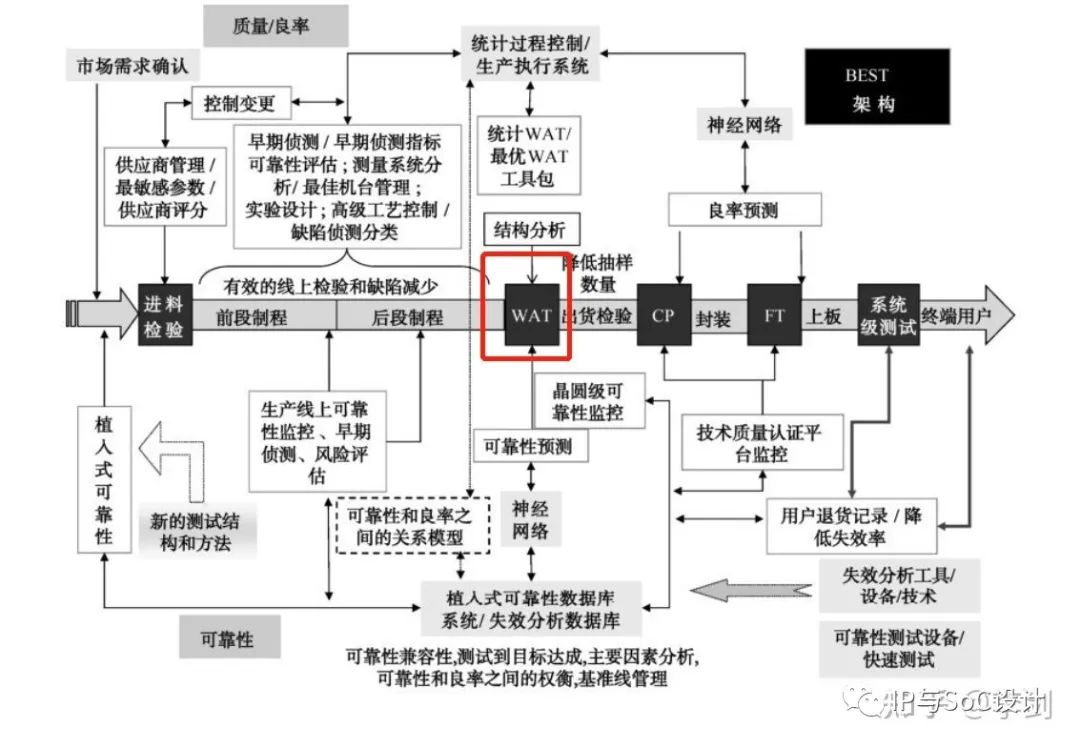

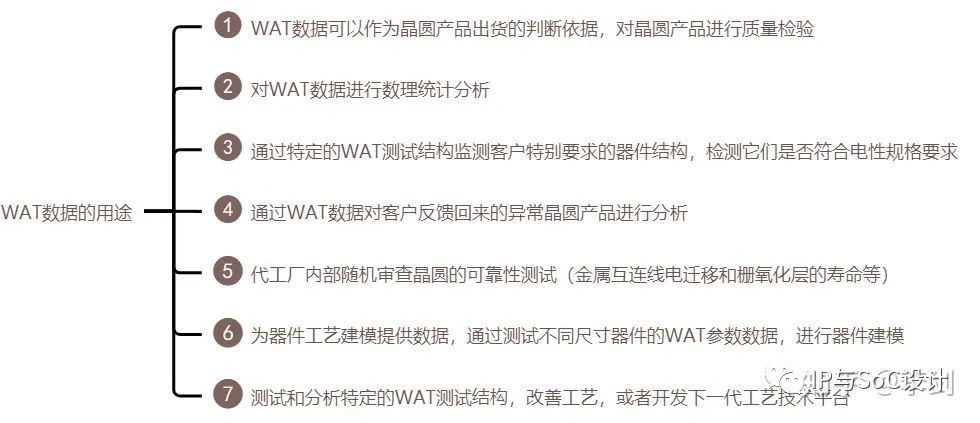

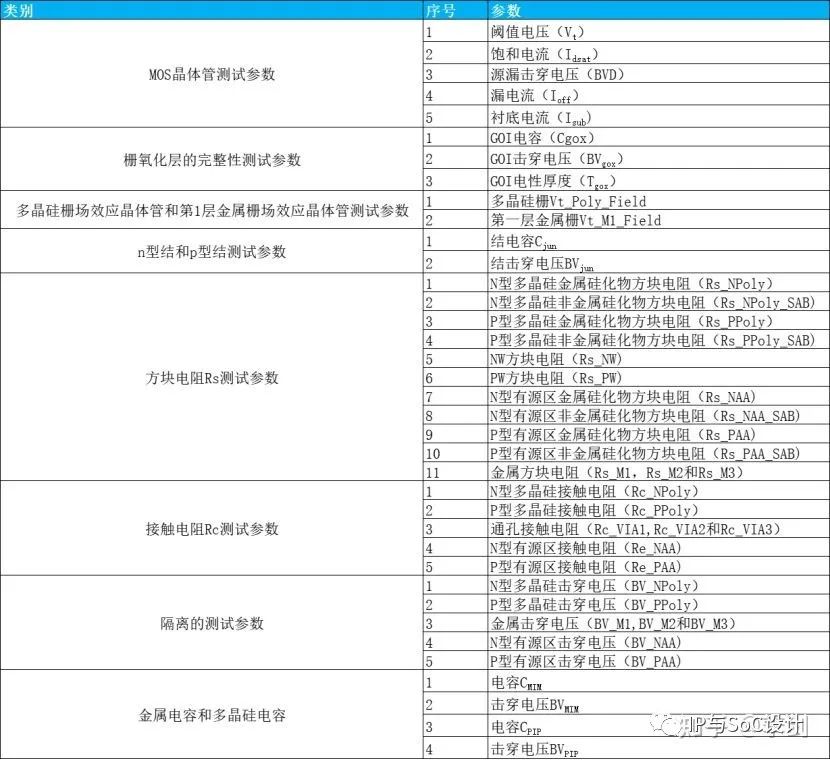

以前做业务的时候,经常问同事,集成电路的工程师到底关注晶圆或者器件的什么性质,哪些性质是通过实验设备测得的,哪些可以是通过模拟仿真获得的。同事就说去看WAT或者集成电路参数手册。后来,一听还要动脑子去找相关资料,就不愿意去干了,不知道如何以及从何处搜索资料。正好最近在研究集成电路制造工艺相关的资料,就看到了让人心中一动的资料。 什么是WAT呢?WAT的英文全称是Wafer Acceptance Test,WAT。中文有人翻译为晶圆接受测试,有人翻译为晶圆可接受测试等等翻译。这里让人想起一个事情,就是以前去新能源行业交流的时候,客户总是问我们,为什么你们拿出来展示的资料都是英文版的。我们说我们做的几个行业分别是半导体和锂离子电池,很多半导体行业缩略语翻译成中文的话,不太好翻译,另外,就是我自己比较懒,也不太愿意去翻译和折腾。这里我们接下来就不纠结于中文的翻译了,咱们还是以WAT直接来说吧。 WAT定义 WAT是英文Wafer Acceptance Test的缩写,意思是晶圆接受测试,业界也称WAT为工艺控制监测(Process Control Monitor,PCM)[1]。WAT是在晶圆产品流片结束之后和品质检验之前,测量特定测试结构的电性参数。WAT的目的是通过测试晶圆上特定测试结构的电性参数,检测每片晶圆产品的工艺情况,评估半导体制造过程的质量和稳定性,判断晶圆产品是否符合该工艺技术平台的电性规格要求。WAT数据可以作为晶圆产品交货的质量凭证,另外WAT数据还可以反映生产线的实际生产情况,通过收集和分析WAT数据可以监测生产线的情况,也可以判断生产线变化的趋势,对可能发生的情况进行预警。 WHY?为什么要用WAT?  摩尔定律 集成电路的设计十分复杂,动辄使用数百万到数十亿个逻辑门数量(gate count),每一个逻辑门和其他器件的电性参数必须同时达到标准,否则芯片可能无法正常运作。一片晶圆通常有数十到数万个芯片,保持制程的均一性相当重要。不但要监控关键的电性和物性,使其在整个晶圆的范围内达到一定标准(SPEC);还得让每一片生产的晶圆都达到这一标准。因此必须引入统计制程管制来完善质量监控[2]。 目前主流的生产系统是8英寸和12英寸[3]的工厂,12英寸晶圆较8英寸大了2.25倍,制程的控制难度也更大;然而工厂把大的晶圆使用在高阶的制程,对控制的要求反而更高。由于工序相当繁复,从投片到产出可能包含近千个步骤,耗时一到三个月,必需使用制造流程(process flow)控制各阶段制程的质量。  中国大尺寸硅片布局盘点 芯片在出厂前要进行各项检测,以确认整个生产流程能达到上述要求。出厂检测包含器件电性参数的量测(Wafer Acceptance Test,WAT),WAT量测包含大多数使用器件的参数,如电阻器的阻值、MOS的栅极氧化层电容值、MOSFET的特性等。这些电性参数可以反应制程工艺是否正常,而掌握工艺对电性的影响更是制程研发的关键。 WAT处于一个芯片制造的什么位置 首先,咱们得知道芯片的制造流程。关于芯片的制造工艺,大家都知道随着先进技术节点的发展,目前芯片的制造工序已经达到上千道工序。而集成电路本身又是技术密集型和资金密集型的行业。所以,对于集成电路芯片制造的良率以及可靠性等内容,是集成电路制造厂以及相关产业链角色极为关注的内容。 参考简维廷等人编著的《半导体制造中的质量可靠性与创新》一书,咱们从可靠性以及良率的角度来看看WAT到底处于芯片制造流程中的哪一个环节。下图即为从质量与可靠性管理的角度来绘制的芯片制造主要流程。  图片根据《半导体制造中的质量可靠性与创新》一书插图进行修改,红色框线代表WAT所在位置 上图中红色框线所代表的内容即为WAT。根据上述内容即可以发现,芯片制造流程的主要干线为:原物料检验(Incoming Quality Assurance,IQA)、晶圆前段工艺(FEOL)监控、晶圆后段工艺(BEOL)监控、晶圆验收测试(Wafer Acceptance Test,WAT)、晶圆出货检验(Outgoing Quality Asurance,OQA)、晶圆良率测试(Chip Probing或Circuit Probing,CP)、芯片封装工艺监控、芯片最终测试(Final Test,FT)、芯片上板工艺监控(On-board Test)、系统级测试(System Level Test,SLT)和终端用户使用[4]。 主干线以上部分,是质量与良率(Yield)管理中需要用到的主要系统和方法;主干线以下部分,则是可靠性管理工作中所要用到的主要手法及管理要点。 上图中的主干线就是将芯片的制造分割为这些主要的过程,并且每个过程都有输出的参数,用于监控。主干线上下所列举的,是在每一阶段,质量与可靠性管理所需要用到的重要系统和方法。实际上,监控并不是越多越好、覆盖越广越好,一味地追求数据的完整性。因为任何生产都是需要考虑成本的,而监控的数据越多,系统越庞杂,所需要投入的初始成本和运营成本也将越高。质量与可靠性需要的是更合适、更先进的技术方法,能够帮助企业提升产品质量与可靠性的同时,达到提高成本利润率的目的。 WAT是晶圆制造的一个重要站点,它是用来检测(也称检验)已经制造完成的晶圆上,各种器件的各方面电学性能(Electrical Performance)是否满足规格要求。如果某些重要参数没有符合要求,晶圆将会被报废,不会进入下一阶段。 WAT简介 WAT testkey 晶圆上用于收集WAT数据的测试结构称为WAT测试结构(WAT testkey)[1]。WAT测试结构并不是设计在实际产品芯片内部的,因为设计在芯片内部要占用额外的芯片面积,而额外的芯片面积会增加芯片的成本,芯片代工厂仅仅把WAT测试结构设计在晶圆上芯片(die)之间的划片槽(Scribe Line)。划片槽的宽度可以从最小的60μm做到150μm,芯片代工厂依据芯片切割机器(Die Saw)的精度要求制定划片槽的宽度设计要求,力求做到最小宽度及最小面积。  图 划片槽中的WAT测试结构 上图所示为划片槽中的WAT测试结构,图a是整块晶圆产品上的芯片,每一个小格子代表一颗芯片;图b是放大后的图形,可以看到芯片间的划片槽;图c是显微镜下的芯片划片槽,白色的方块区域是顶层金属窗口,通常称为封装金属窗口(Bonding PAD),WAT测试结构在PAD与PAD之间,很多不同的测试结构组成一组测试模组,芯片代工厂会给每组测试模组定义一个名称,每一片晶圆会包含很多这样的不同的WAT测试模组。 WAT测试在大多数情况下,都是利用晶圆切割道(Scribe Lane)上专门设计的测试结构(Test Pattern或Test Structure)完成的。通过这些测试结构的组合和测试结果的分析,我们基本上可以监控到晶圆制造的每一道工序。但是某些特殊的产品,如功率器件(Power IC),为了充分利用晶圆的面积,增加每片晶圆上晶粒的数目,会尽量压缩切割道的面积,从而导致切割道太小,无法放置测试结构。当然,这类产品的制造工艺和电路设计一般都比较简单,所以不需要浪费面积设计测试结构,而是可以通过直接测试晶粒来完成WAT。对它们来说,WAT测试项目和良率测试项目是相同的,所谓的WAT只是预先抽样进行良率测试而已。有的时候甚至会选择不做WAT,直接进行良率测试。在切割道上不放置WAT测试结构的另外一个好处,是可以降低晶圆封装时的切割难度。对于采用90nm 以下先进工艺制造的产品,切割道上测试结构的设计会影响晶圆切割质量的现象,已经成为众所周知的事情。在芯片与封装交互作用的研究中,这也成为了一个重要的课题。液晶显示器驱动芯片(Liquid Crystal Display Driver,LCD Driver)是另一类不会在切割道上放置测试结构的产品。因其形状又长又窄,而又不能预先减薄晶圆,所以在整体考虑质量控制的策略之后,通常会选择不在切割道上放置测试结构。其实,很多的案例也表明,复杂的切割道测试结构设计,不仅会给封装切割带来困难,同时也会给晶圆的制造带来很多额外的风险。比如,因为负载效应(Loading Effect),切割道上大块的铜金属结构会导致附近晶粒边缘的铜线磨不均匀,而容易出现短路(Short)或者断路(Open)。所以在设计WAT测试结构的时候,要遵循一定的规则,同时也需要非常细心、谨慎[4]。 WAT测试结构通常包含该工艺技术平台所有的有源器件、无源器件和特定的隔离结构。例如,有源器件包括MOS晶体管、寄生MOS晶体管、二极管和双极型晶体管等,但是在标准的CMOS工艺技术中,仅仅把MOS晶体管和寄生MOS晶体管作为必要的WAT测试结构,而二极管和双极型晶体管是非必要的WAT测试结构。无源器件包括方块电阻、通孔接触电阻、金属导线电阻和电容等。隔离结构包括有源区(AA)之间的隔离,多晶硅之间的隔离和金属之间的隔离。WAT参数是指有源器件、无源器件和隔离结构的电学特性参数[1]。 WAT测试是非常重要的,因为这是晶圆产品出货前第一次经过一套完整的电学特性测试流程,通过WAT数据来检验晶圆产品是否符合该工艺技术平台的电性规格要求,以及工艺制造过程是否存在异常。 WAT数据有很多方面的用途,把它归纳为以下七大类:  WAT测试类型 WAT的测试类型按照温德通编著的《集成电路制造工艺与工程应用》可以分为如下8类。  WAT测试类型,根据温德通编著《集成电路制造工艺与工程应用》一书文本类容绘制的思维导图 上图主要是以CMOS工艺技术平台为例。具体测试项的部分内容如下表所示。  在参考资料中,作者不仅对要测试的内容作了综述,同时还对影响相关测试的内容作了补充,比如影响MOS器件某一性能的影响因素都有什么,主要的工艺影响因素是什么,均作了相应的介绍。有兴趣的朋友可以去看看。 参考资料: 1.温德通编著.《集成电路制造工艺与工程应用》 2.张汝京等编著.《纳米集成电路制造技术》 3.https://www.sohu.com/a/329973217_132567 4.简维廷等著.《半导体制造中的质量可靠性与创新》 本文来源:https://zhuanlan.zhihu.com/p/430376276 |