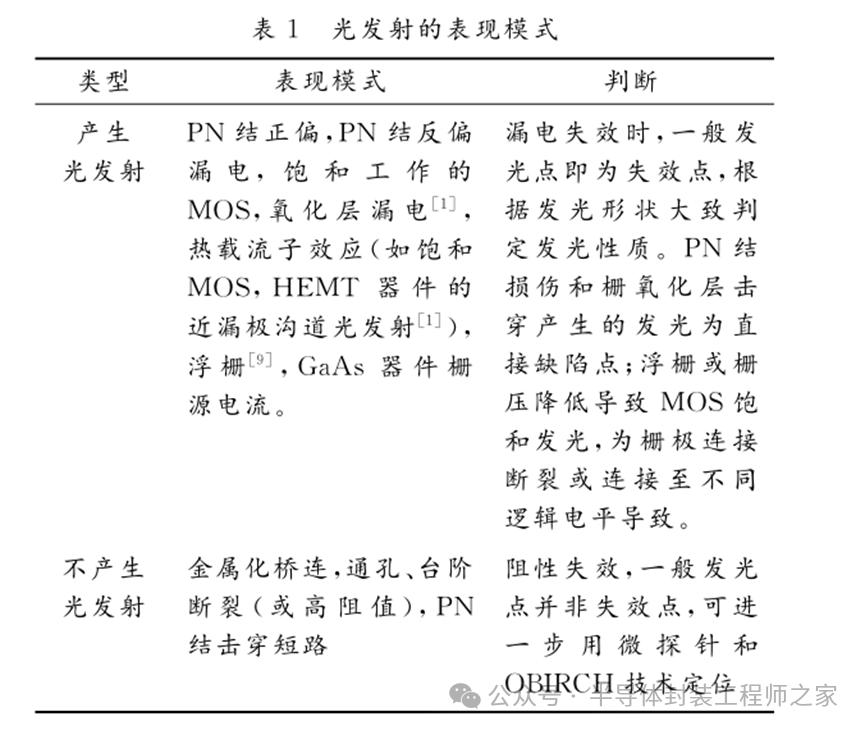

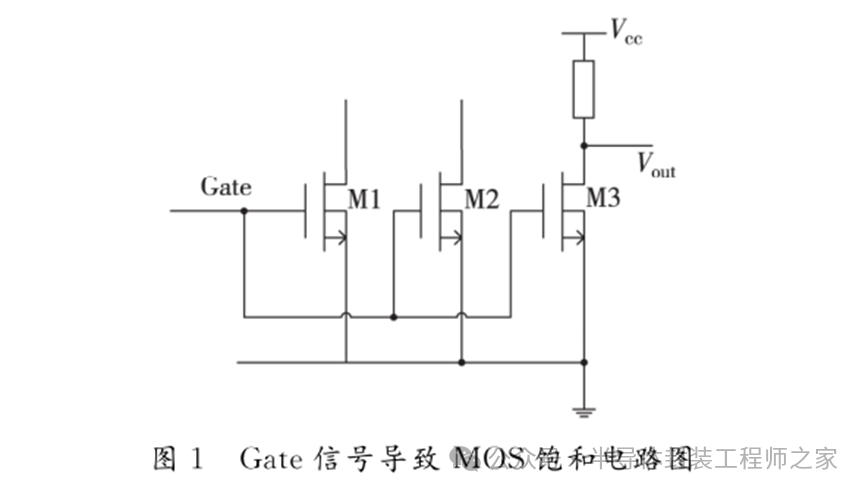

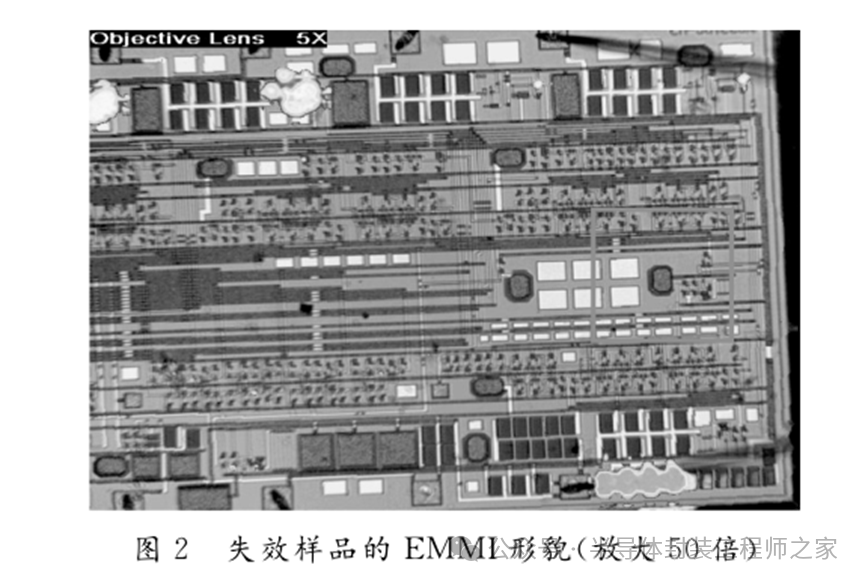

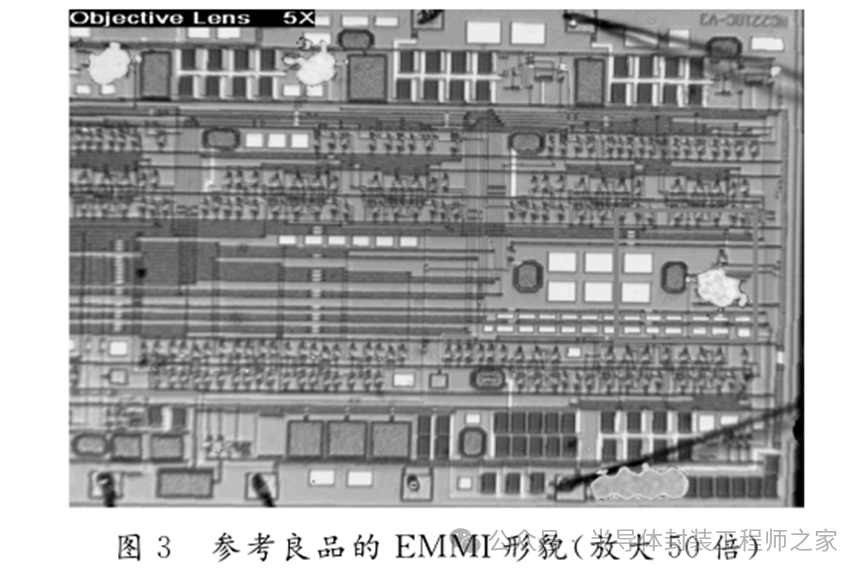

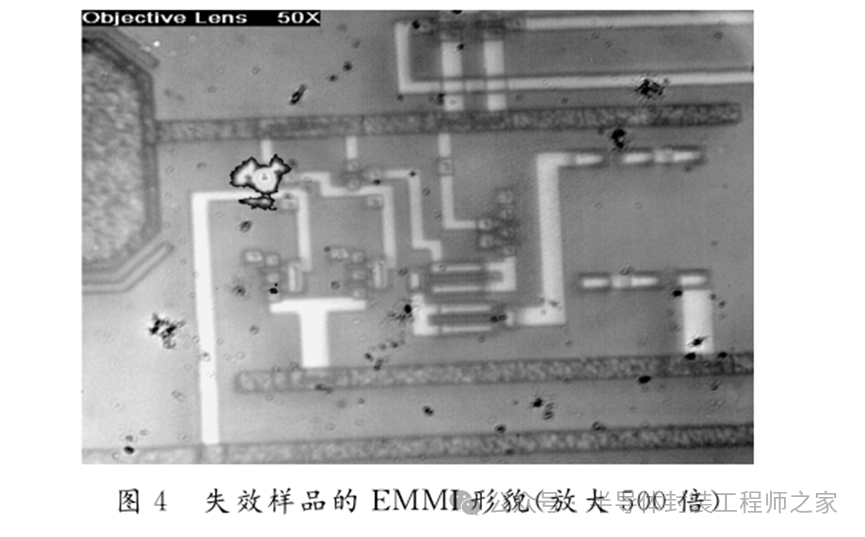

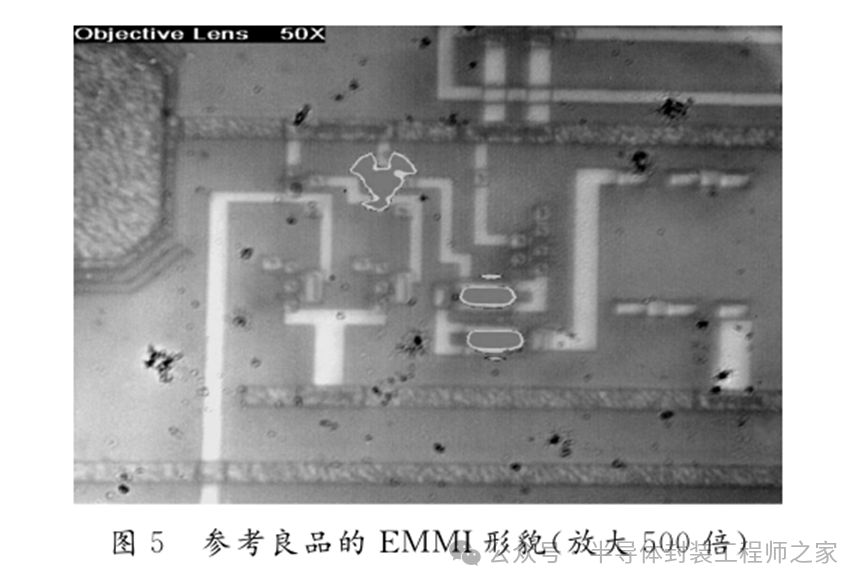

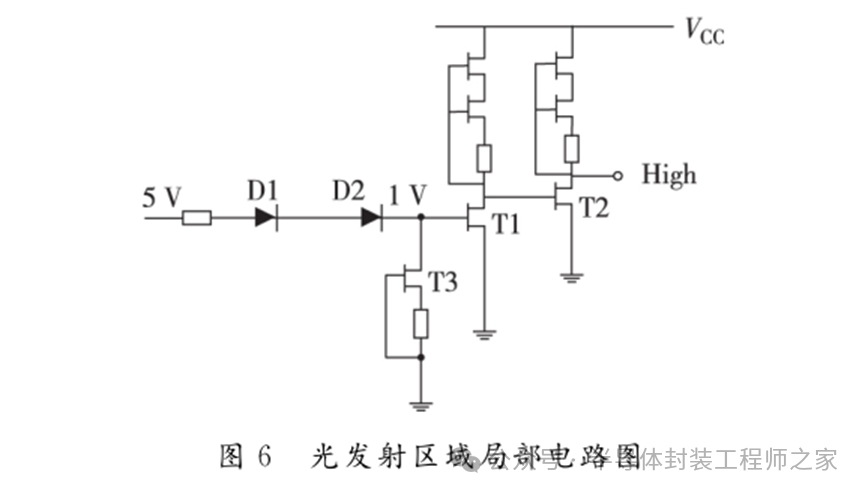

摘要:EMMI被广泛应用于集成电路的失效分析和机理判定。针对端口I-V特性曲线的异常现象,采用静态电流的发光效应对漏电点进行光发射定位。静态电流法无法全面测试集成电路内部逻辑单元,需要使用动态信号驱动集成电路,使内部失效部位能够产生光发射。对样品在动态失效工作状态进行光发射捕捉,再结合良品对比、电路原理图和版图分析等辅助手段进行故障假设,以定位失效点,最后利用FIB系统对电路进行剖面切割制样,找出物理损伤点。对砷化镓数字集成电路的不稳定软失效案例进行分析,动态EMMI法与FIB系统联用可成功应用于芯片内部金属化互连异常的失效分析,解决传统静态光发射法无法定位的技术难题。0引言 集成电路包含多种失效机理,例如过电应力、静电放电、固有缺陷、栅氧化层击穿、金属桥连、通孔开路、PN结损伤等[1-3]。有些失效可以直接通过静态直流检测得到,比如,端口I-V特性曲线表征异常时,采用静态光发射显微镜法(EMissionMIcroscopy,EMMI)或者光致电阻变化法(OpticalBeamInducedCurrentChange,OBIRCH)可以进行定位[4-6]。有些功能性失效则必须在全电路工作时才能被观察到,甚至可能出现与温度、时间等因素有关的不稳定失效,如软错误等[7]。对于这种功能性失效,I-V特性曲线无法侦测出静态电流(直流电流)异常,采用静态光发射法进行失效定位变得十分困难。 根据半导体光发射原理,EMMI能够探测多种形式的发光,因此可用于探测电路处于动态状态时晶体管的工作状态[8]。但是,电路动态工作时,晶体管可产生正常光发射,也可产生异常光发射,甚至不发生光发射。对EMMI结果的界定就需要进行故障假设,即通过良品对比、集成电路的原理图和版图分析等方法来验证EMMI的发光点是直接缺陷还是其他电路缺陷导致的发光[8]。对于垂直结构的失效,如金属断裂、通孔断裂失效等,去层处理后无法正面观察到,应结合剖面分析,这就需要采用聚焦离子束(FocusIonBeam,FIB)系统进行制样。 本文介绍了动态EMMI的原理、思路,通过对一个局部功能异常的集成电路进行失效分析,利用动态EMMI法进行失效定位,并采用FIB系统观察金属台阶剖面形貌,找到失效点,证明了联用方法对金属断裂引起功能故障的失效分析是有效的。 1动态EMMI原理与FIB系统介绍 1.1动态EMMI原理 为了检测内部逻辑电路的失效点,集成电路晶体管必须处于完全打开/关闭的状态。对于模拟集成电路而言,动态状态指的是直流偏置状态,而不仅仅是添加小信号时的状态,这是因为模拟电路的失效往往是由偏置异常引起的。对于数字电路而言,晶体管工作时处于0/1状态,此功能由反相器实现。晶体管处于线性导通或截止状态时,EMMI均探测不到明显的光发射[8]。对于MOS电流镜而言,器件工作于饱和区时,EMMI可以探测到饱和导通MOS管近漏极的发光现象。 对集成电路动态工作时晶体管、二极管光发射的表现模式进行归类,有助于理解观测到的光发射现象,作出判断。失效点的主要表现模式列于表1。 动态EMMI法要求器件工作在失效状态下。测试时,首先确认电路的失效模式,动态测试过程中遇到失效向量时可以保持住,这就是锁存失效状态,通过EMMI捕捉此时异常的光发射,进行定位。锁存的意义有两点,一是保证光发射是在失效时采集的,二是EMMI可能需要足够时间进行曝光。对于一些稳定失效,也可以通过反复运行功能测试板或自动测试程序来捕捉光发射。当芯片出现发光点时,判断发光是否正常主要依靠两个方面:一是对相同加电条件下良品芯片进行对比,确定不同发光位置、形状;二是确定异常发光位置后,通过电路原理图或版图解释发光原因、假设失效可能并确定失效位置,以便进一步作物理或化学分析,即确定发光点是失效点还是偏置电路异常所导致,以缩小失效定位范围。  1.2失效模式对EMMI结果影响 内部逻辑电路出现开路或短路(阻性)失效模式时,均可能导致发光异常:要么缺陷自身产生光发射;要么缺陷本身不发光,但可能造成2次效应,导致其他电路发光。 根据光发射的形貌特点,大致判断失效模式:当二极管发生正偏,GaAs栅源通电流时,结区或沟道位置均匀发光;二极管反偏漏电或者氧化层漏电时,发光处一般呈点状(圆斑状);MOS管进入饱和区时,在靠近漏极区域的MOS管夹断区会产生光发射,形状为方形或线形,与沟道宽度相等。MOS晶体管进入饱和区往往是因为栅极电压被拉低(处于中间状态)、驱动不足造成的,可以通过探针测试来测量饱和发光MOS管的栅极电压,确定其电位是否处于中间状态。若电位为中间状态,需要根据电路原理查找栅极漏电区域,或进行OBIRCH分析。 以图1所示电路为例,分析当M3管的栅源击穿呈阻性时,引起M1和M2管饱和的情况。假设正常情况下Gate接5V电压,MOS管线性导通,当M3管栅源击穿呈阻性时,M3管的电压可能被拉低至2V(即处于中间态电平),那么M1和M2管均处于饱和导通状态。其他常见失效情况有:当结区击穿、金属化桥连呈现阻性时,失效点不发生光发射现象,缩小范围后可通过OBIRCH进行失效定位;当内部金属化或通孔断裂呈高阻或开路特性时,局部电路偏置异常,不产生光发射或连接支路异常光发射,应结合电路和版图分析,进行聚焦离子束系统制样观察。  1.3FIB系统制样 FIB系统利用聚焦的镓离子束轰击进行定点切割及局部放大成像,主要用于观察两种情况:一是金属化台阶断裂、相邻金属化桥连,二是金属通孔断裂。这两种情况均需要进行垂直剖面分析。 采用DCGSystems装载有InGaAsCCD图像传感器的Trivision型号光发射显微镜进行光信号采集。该图像传感器可采集的光谱范围为近红外光,波长约为900~1600nm,涵盖了大部分发射光的光谱范围[10],比硅CCD具有更高的采集效率。样品功能测试偏置电路和采集回路由直流稳压电源、信号源和示波器构成。 2失效分析案例研究 2.1动态EMMI法 失效样品为双模+/-计数器,采用0.25μmGaAsE/D模式pHEMT集成电路工艺制造。电路端口up置高时进行加计数,down置高时进行减计数。器件经过高温试验后,在一次常温测试时失效。对样品进行自动功能测试时发现,up置高时进行减计数或者先减计数后恢复加计数功能,器件局部功能异常并呈现不稳定失效特征,表明该失效可能与软缺陷有关。将失效器件与良品分别在反复的动态加电状态下测试并捕捉发光图像,结果表明,失效电路局部输入控制单元不发光,如图2所示,参考良品在相同位置发强光,如图3所示。   为进一步观察发光特点,放大至500倍进行对比,如图4和图5所示。结合图6所示局部电路进行分析,失效样品发光点为T2管,这表明T2管已导通。良品D1,D2,T1管产生光发射,表明栅源之间有明显电流流过。   2.2电路分析与失效模式影响 光发射区域局部电路如图6所示,该电路输出High信号对up,down信号进行锁存控制。D1,D2,T3管构成降压电路,将5V电压降至1V,用来控制T1管的栅极。T1管为第1级反相器,T2管为第2级反相器,电路正常工作时应输出High信号。因此,良品D1,D2,T1管均为导通状态,T2管处于截止状态;失效样品D1,D2,T1管均未导通,而T2管处于导通状态。  结合失效电路进行2种故障假设:1)D1,D2管击穿,那么T1管应发光,并且由于T1管存在体电阻,T1管的输出电压会上升,造成T2管也发光,此情况可排除;2)D1,D2,T3管均未工作。该失效模式与光发射结果相符,结合样品测试过程表现为不稳定失效,判断D1,D2,T3管之间金属化互连断开。 2.3FIB制样及物理失效分析 D1,D2管之间开路的可能性较大。利用FIB系统对氧化层台阶位置进行切割,可观察到台阶处金属膜断裂,如图7所示。钝化层及氧化层均未出现微裂纹,但氧化层台阶较陡。 氧化层台阶处的金属膜断裂主要与蒸发工艺自掩蔽效应、台阶形状以及磷硅玻璃厚度有关。台阶越陡,金属膜淀积时越容易出现微裂纹。此工艺中,导线为纯金金属化,通过蒸发工艺形成。蒸发工艺中,由于芯片在腔体的放置位置不同,偏离蒸发源较远的芯片所受蒸压和蒸发角度会不太理想。偏离蒸发角度较大的芯片,入射原子达不到台阶阴面,产生死角,从而形成空隙。同时,平面上蒸发的金属薄膜沉积速率较快,而侧壁上的金属沉积速率较慢,在台阶处形成低密度原子区域,甚至产生空气缝隙或空洞,导致金属厚度降低,薄膜的电学和机械性能降低,在使用中应力-应变效应可诱发失效,这是造成开路的根本原因。因此,要改善器件性能,应适当降低台阶高度、减缓坡度,并控制好金属蒸发工艺。  3结论 本文介绍了动态EMMI的原理和失效定位思路,列出电路可能的失效模式及其动态EMMI效应;通过失效样品与良品不同发光点的对比,逐步缩小电路故障定位的范围;通过电路分析、故障假设得出异常发光的可能原因,再结合FIB系统制样观察,找出物理损伤点。分析结果表明,动态EMMI法联用FIB系统可用于集成电路金属化断裂引起局部功能异常的失效分析,突破静态电流法无法进行内部逻辑电路失效定位的瓶颈。 |