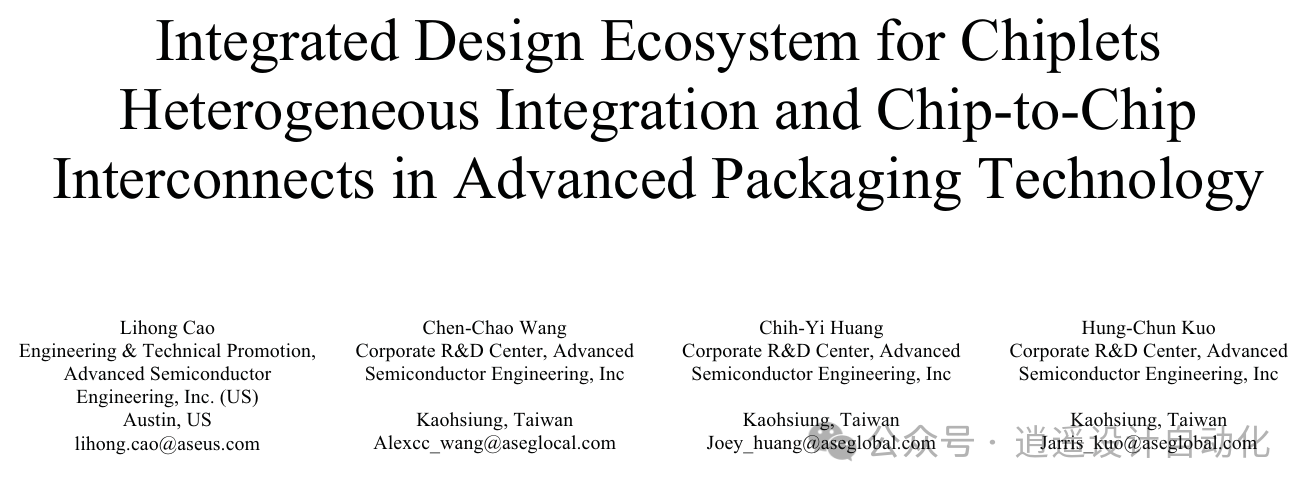

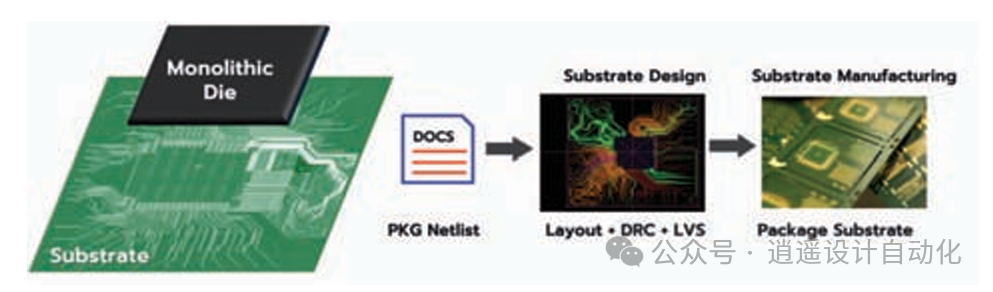

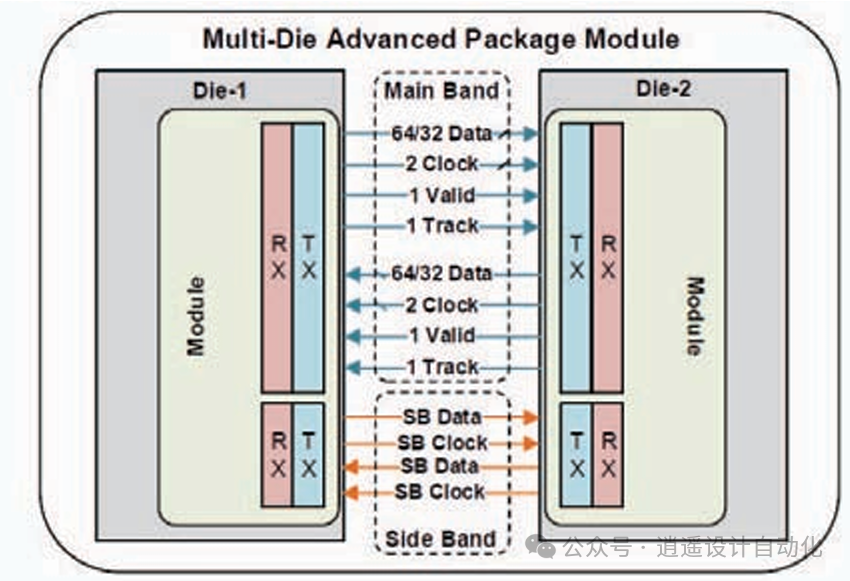

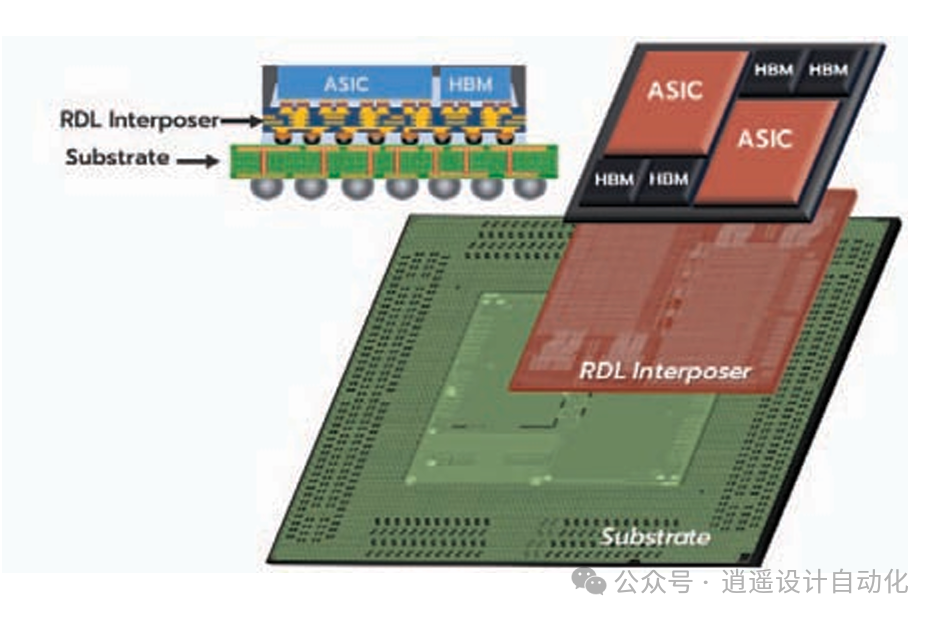

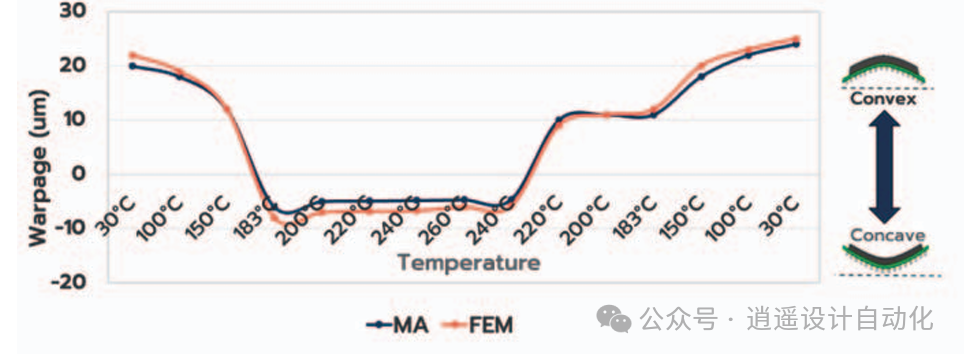

Chiplet集成技术已成为先进封装技术中的重要发展方向,为克服传统单片芯片设计的局限性提供了解决方案。此技术实现了在同一封装内集成多个裸片,在半导体制造中提供了更高的灵活性、性能和成本效益[1]。 设计平台与工具 Chiplet设计平台整合了全面的工具和方法,用于解决各种设计挑战。该平台集成了来自不同供应商的设计和验证工具,以简化工作流程。  图1展示了Chiplet集成的芯片到封装I/O平台,显示了不同设计层之间的互连关系。 先进封装集成 现代Chiplet集成主要依赖先进封装技术,包括多种裸片间互连方法。业界已通过UCIe(通用Chiplet互连标准)开发了标准化方法,涵盖了从事务层到封装的完整协议栈。  图2说明了Chiplet集成的芯片到封装I/O平台,展示了完整的布局和互连设计。 机械分析与模拟 Chiplet集成的机械分析和模拟是一个关键环节,包括以下内容: 使用阴影摩尔法评估芯片到封装的翘曲 通过有限元方法建模进行机械行为模拟 评估Chiplet集成设计的长期可靠性  图3展示了Chiplet集成的先进机械分析工作流程,显示了分析和模拟的各个阶段。 裸片间接口标准 裸片间接口的标准化是Chiplet集成发展中的重要进展。UCIe规范定义了以下关键属性: 物理层规范 事务层协议 封装要求  图4显示了用于先进封装模块的UCIe物理层(PHY)框图,详细说明了接口架构。 性能与验证 Chiplet集成的性能验证涉及广泛的测试和验证过程,包括: 在各种I/O条件下的电气性能分析 热管理评估 信号完整性验证 功率分配分析  图5展示了在2.5D封装中含两个Chiplet集成时,测量翘曲与机械模拟结果的对比。 结论 Chiplet集成技术的发展持续推动半导体封装创新。全面的设计方法,结合标准化接口和先进分析工具,使异构集成解决方案更加高效可靠。业界通过UCIe实现裸片间互连标准化,促进了Chiplet技术在各供应商和应用领域的广泛应用。 |