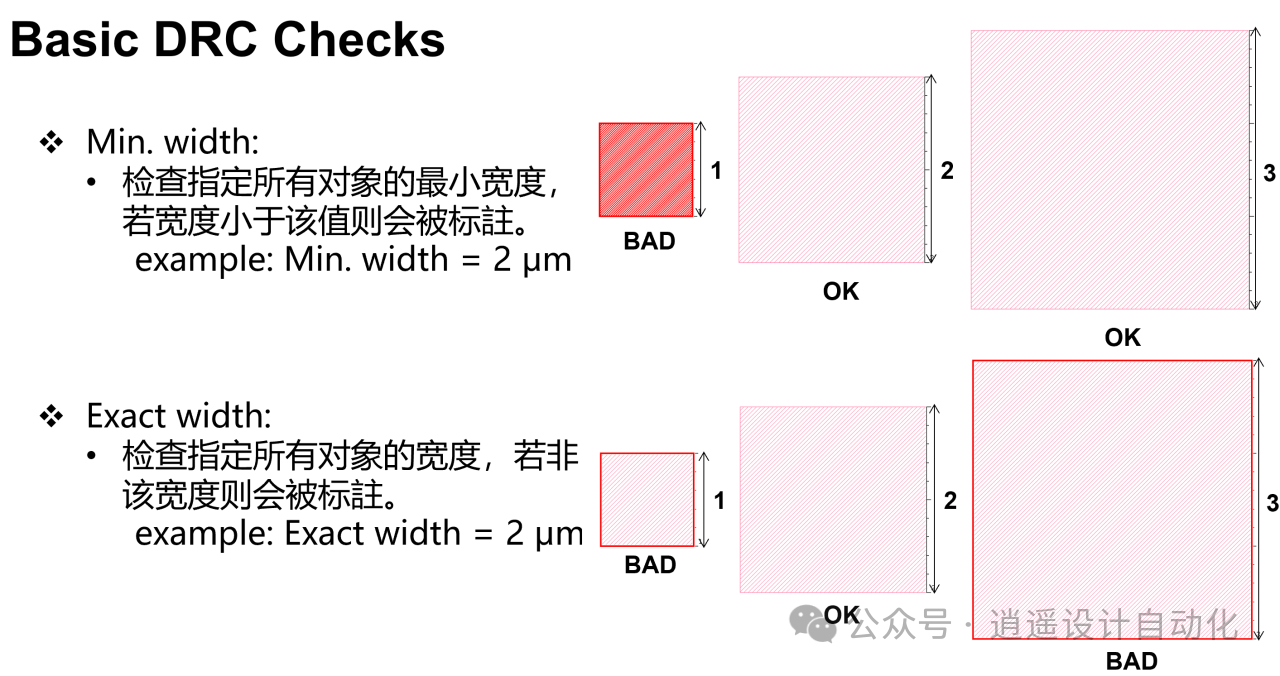

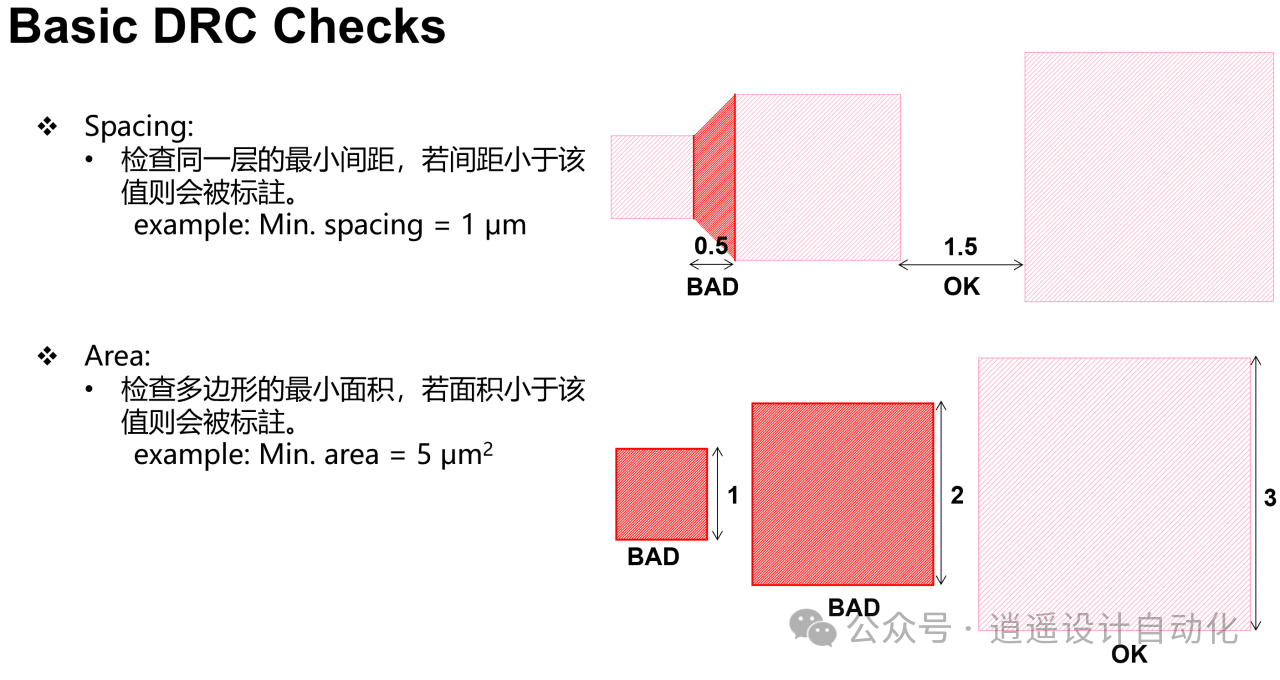

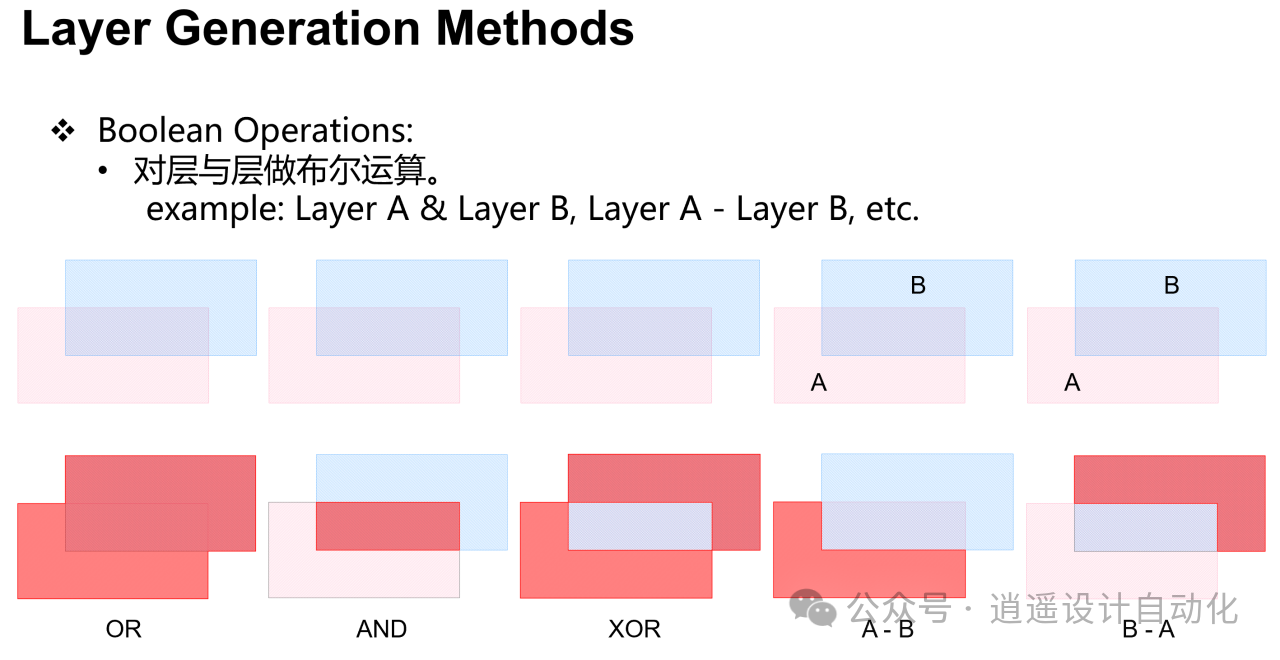

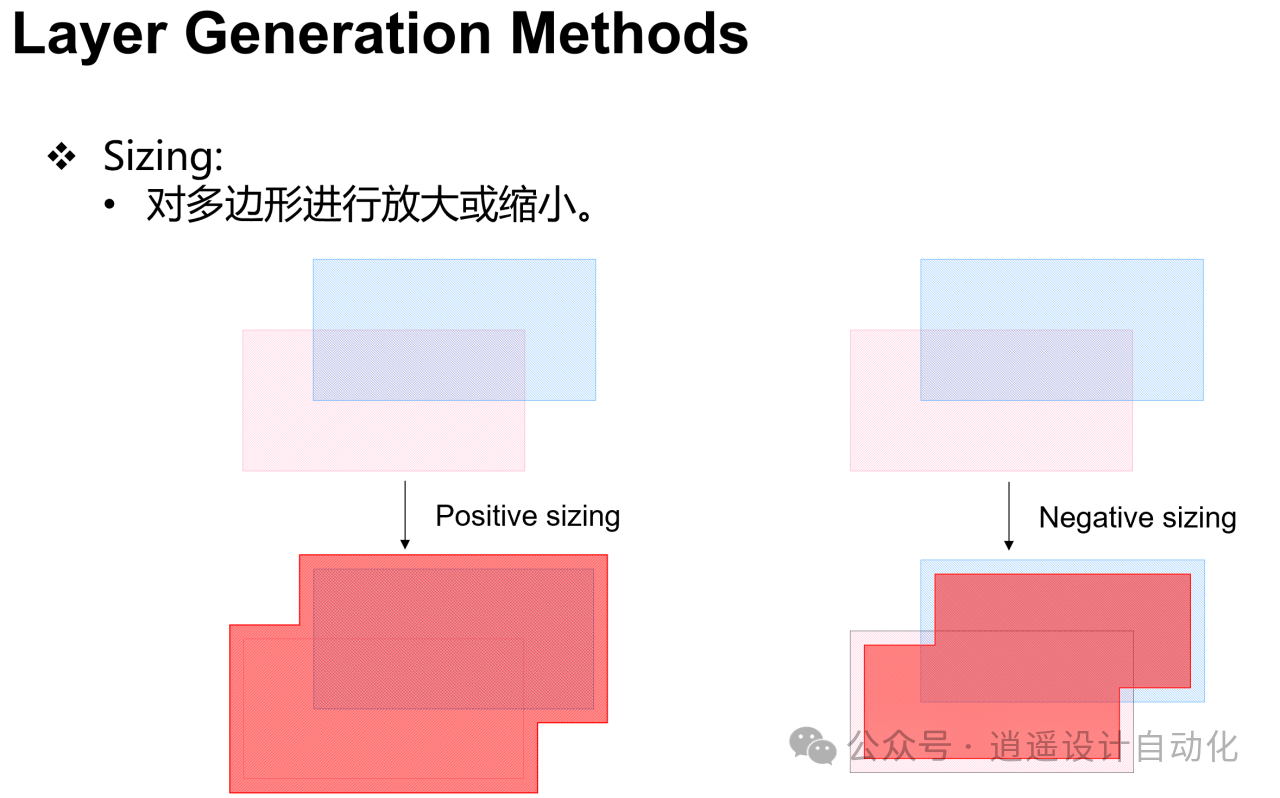

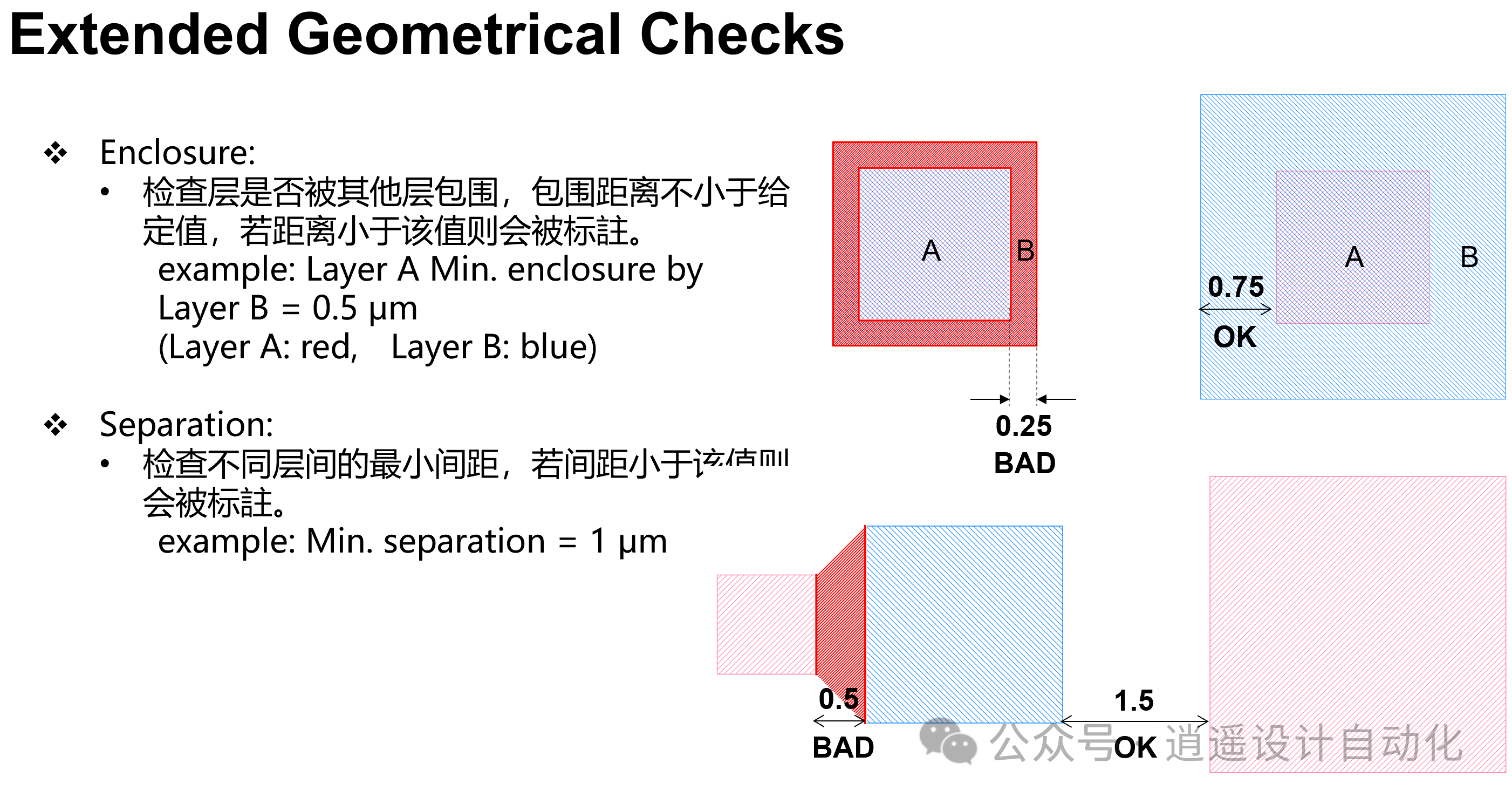

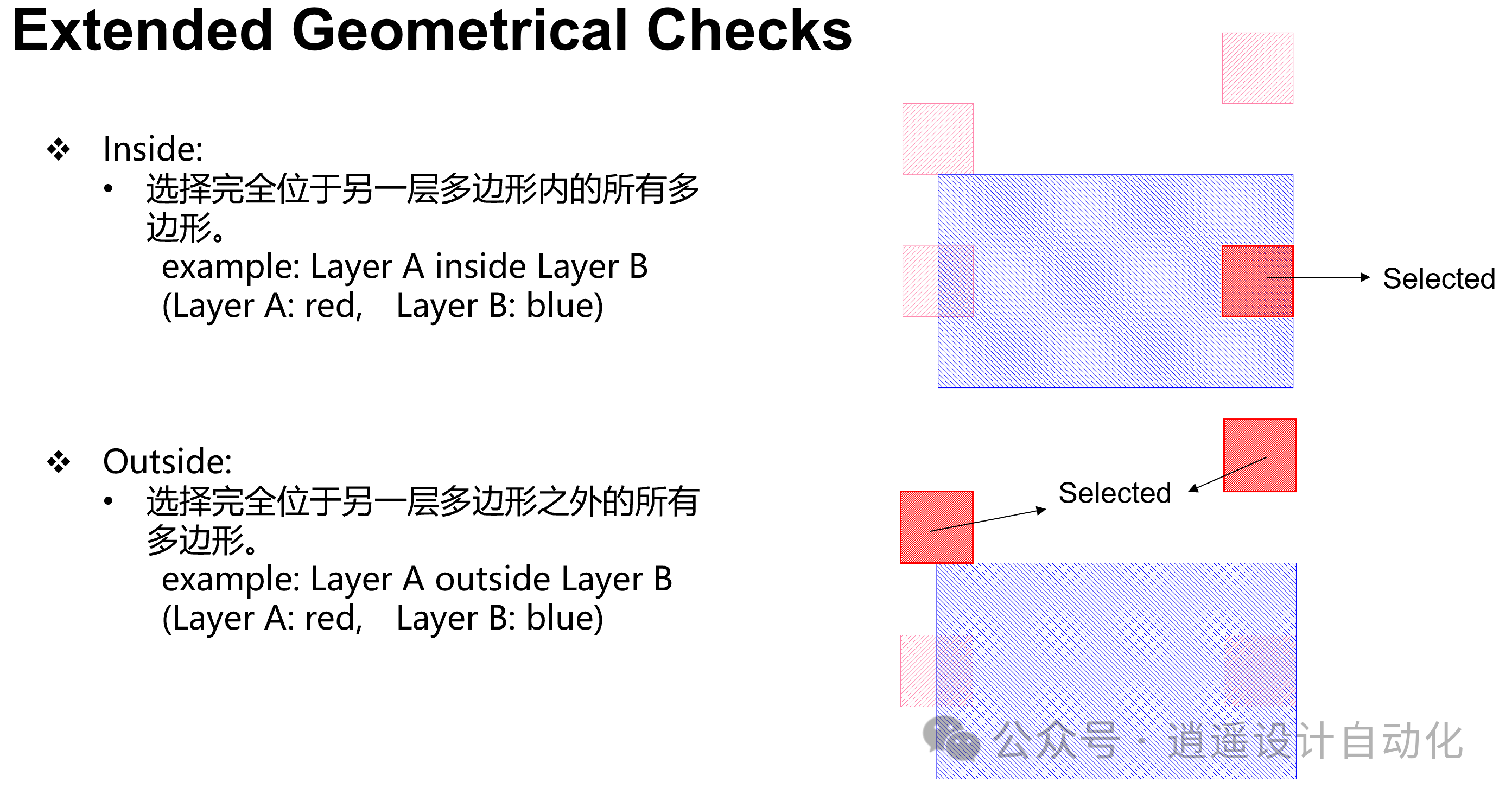

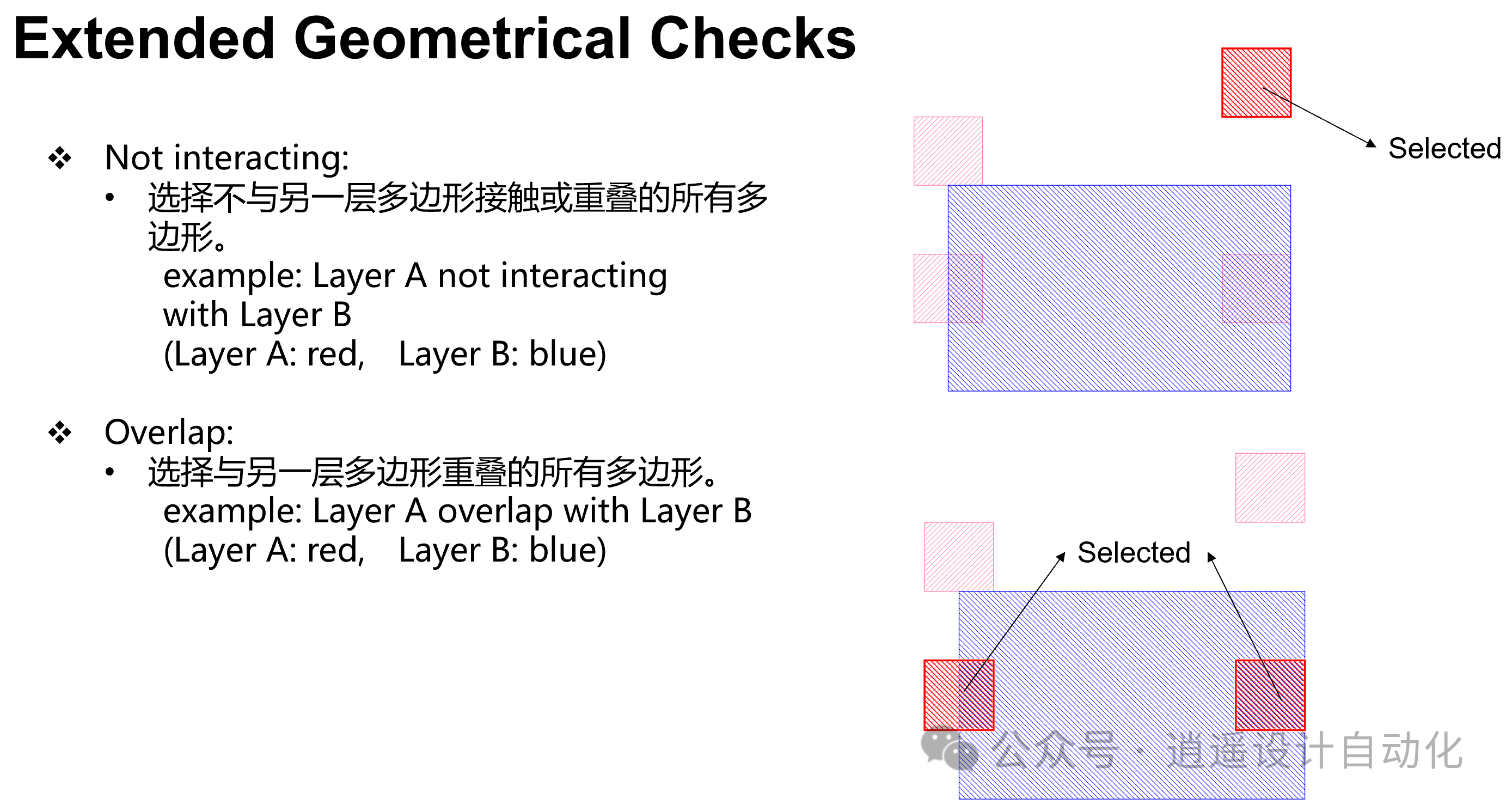

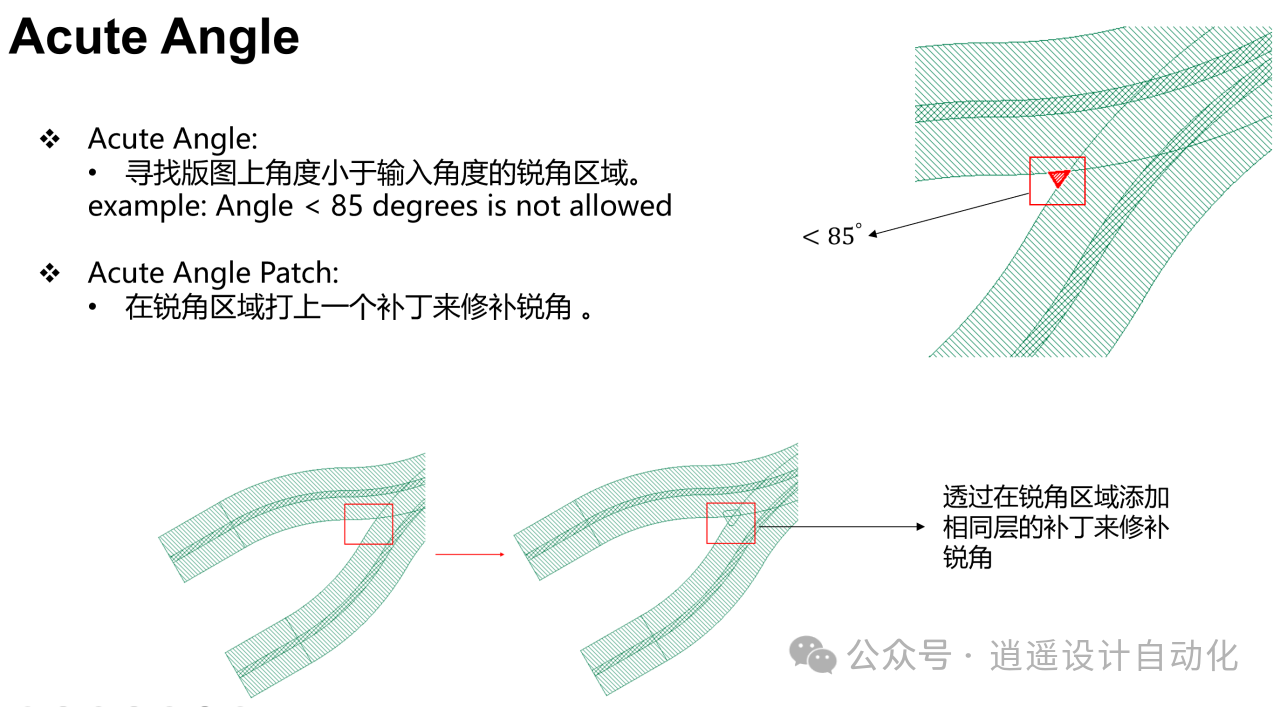

设计规则检查(DRC)简介设计规则检查是集成线路设计中的关键验证步骤,通过验证物理版图是否符合预定义的设计规则来确保制造可行性。在光电子集成芯片中,由于光波导和器件的特殊要求,设计规则检查变得更加重要。PIC Studio当中的pVerify DRC工具提供全面的设计规则检查功能,使设计人员能够高效地验证版图。 基本设计规则检查 PIC Studio实现了构成版图验证基础的设计规则检查,确保各个几何元素满足制造约束。该平台提供多种基本检查机制。  图1:基本设计规则检查的图示,包括最小宽度和精确宽度要求,展示了尺寸超出指定参数时如何识别违规情况。 最小宽度检查确保没有特征比工艺定义的最小尺寸更窄。这对波导尤为重要,因为宽度变化会显著影响光学性能。精确宽度检查验证特定特征是否保持精确尺寸,这对定向耦合器等器件极为重要,因为耦合比依赖于精确的几何参数。  图2:设计规则检查验证中的间距和面积检查演示,展示了如何验证特征之间的最小间距和最小面积要求。 间距检查验证相邻特征之间是否存在足够的分隔,以防止制造问题和不需要的耦合效应。面积检查确保特征足够大,可以可靠制造,这对接触焊盘和其他金属结构特别重要。 层生成方法 PIC Studio提供了支持复杂设计规则检查操作的复杂层生成功能。  图3:用于设计规则检查验证的各种布尔运算(或、与、异或、A-B、B-A)的图示。  图4:用于修改几何特征的正向和负向尺寸操作演示。 扩展几何检查 除基本检查外,PIC Studio还实现了复杂光子结构所需的高级几何验证功能。  图5:扩展几何检查的示例,包括不同层之间的包围和分隔要求。   图6:各种几何关系检查的演示,包括不同层之间的内部、外部、不相交和重叠条件。 锐角和密度检查 PIC Studio为制造关键特征提供专门的检查,锐角可由用户自行决定是否执行自动修复,或是用户自行手动修复。  图7:锐角检测和修正方法的图示,展示了如何识别和修补关键角度。  图8:密度检查演示,展示了如何根据指定限制验证局部图形密度。 与设计流程的集成 PIC Studio的设计规则检查功能完全集成到设计流程中,支持各种输入点和验证方法。  图9:全面的图表,展示了设计规则检查验证如何与不同设计流程集成,包括原理图驱动、版图驱动和GDS驱动方法。 pVerify设计规则检查解决方案的优势  图10:pVerify作为设计规则检查解决方案的主要优势概述,突出其效率和成本效益。 PIC Studio的pVerify提供多个主要优势: · 全面的设计规则检查套件确保设计准确性 · 包括布尔运算和密度检查在内的高级功能 · 早期阶段的设计规则检查验证实现快速问题解决 · 与基于Windows的设计流程无缝集成 · 所有设计人员都能使用,促进持续的设计验证 · 与业界标准签核工具(如Calibre)兼容 PIC Studio平台支持主要光电子芯片代工厂和工艺,确保在行业内广泛适用。高效的验证引擎在保持设计规则检查高准确性的同时实现快速周转。通过这种全面的设计规则检查实现,使设计人员能够创建可制造的光电子集成芯片,同时保持高生产力和设计质量。 |