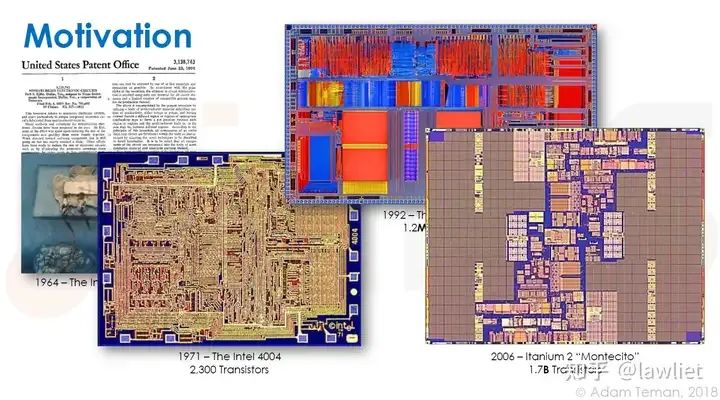

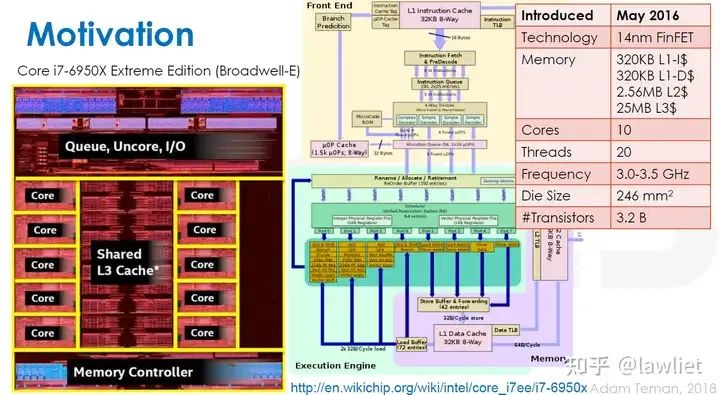

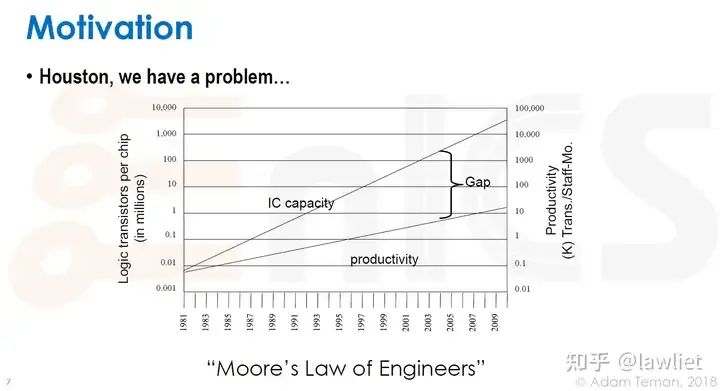

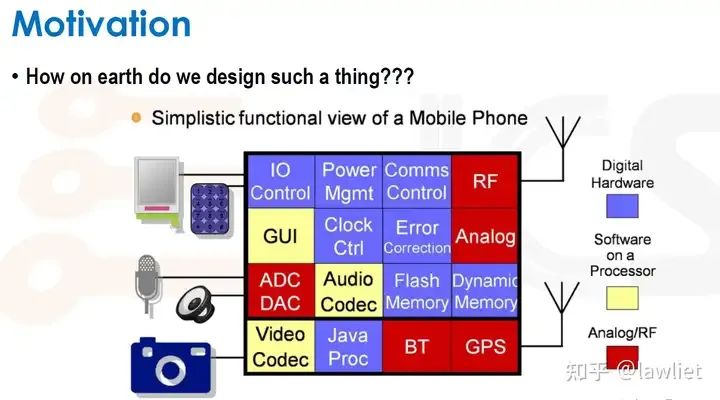

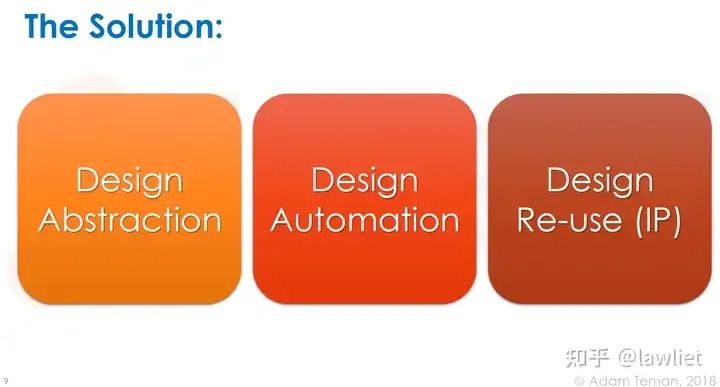

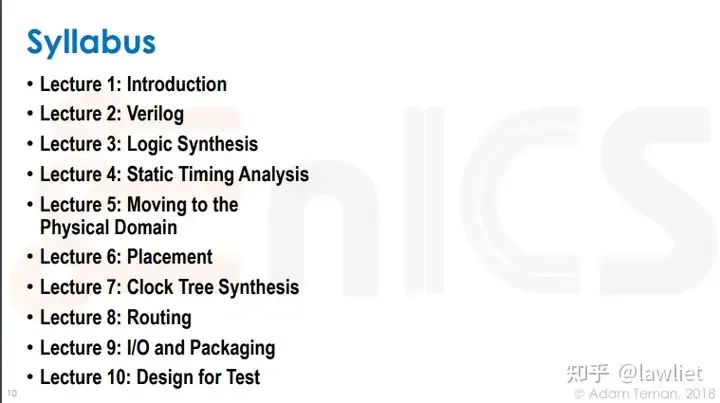

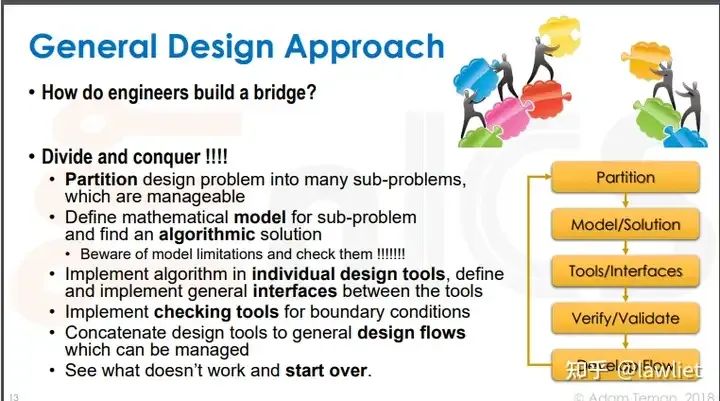

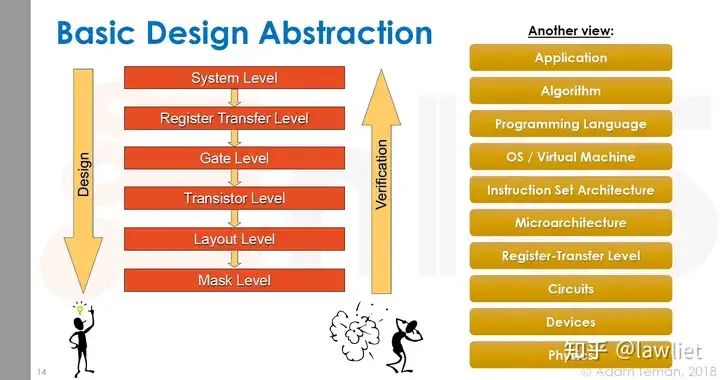

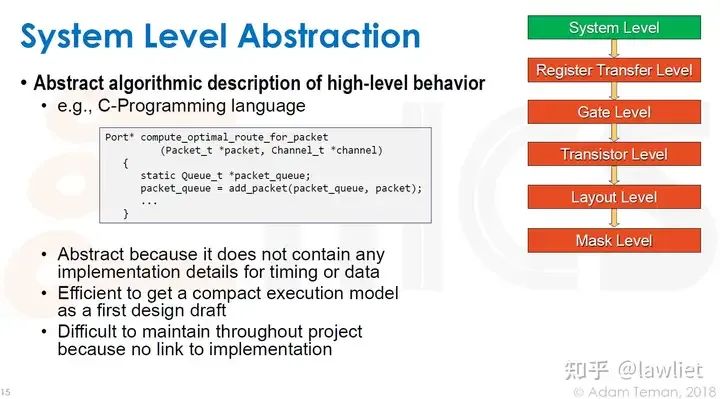

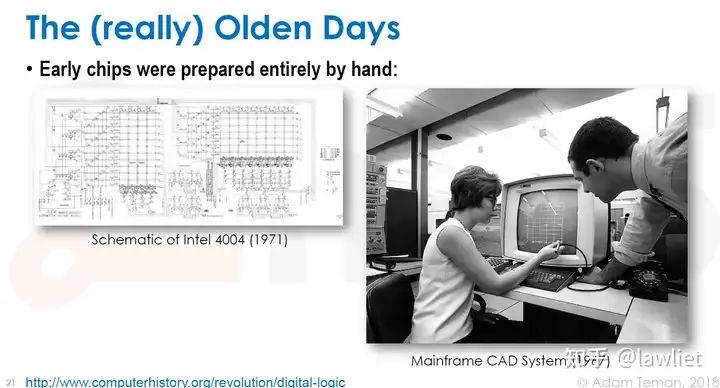

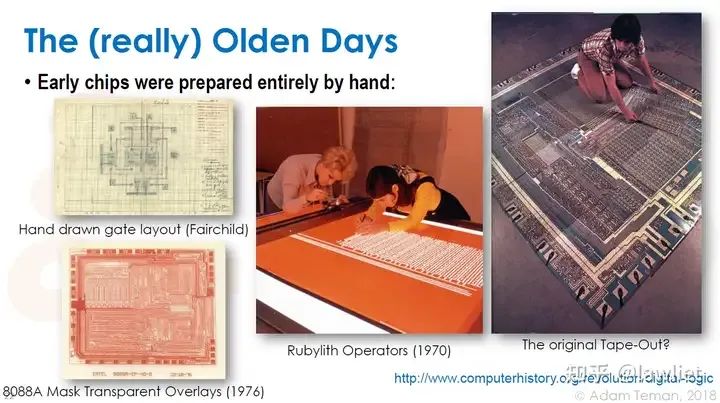

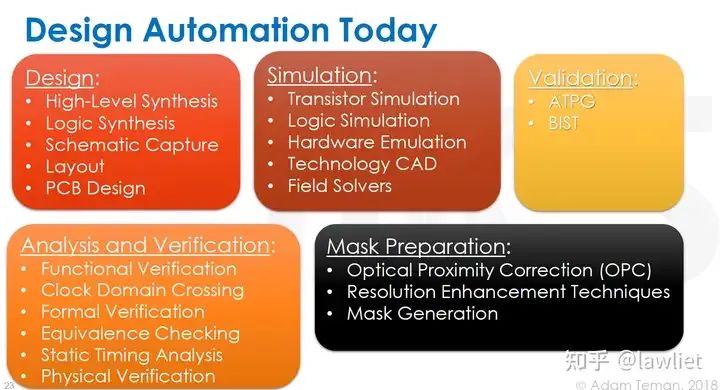

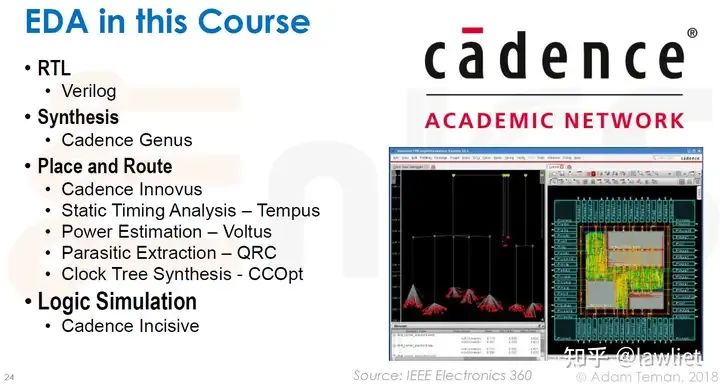

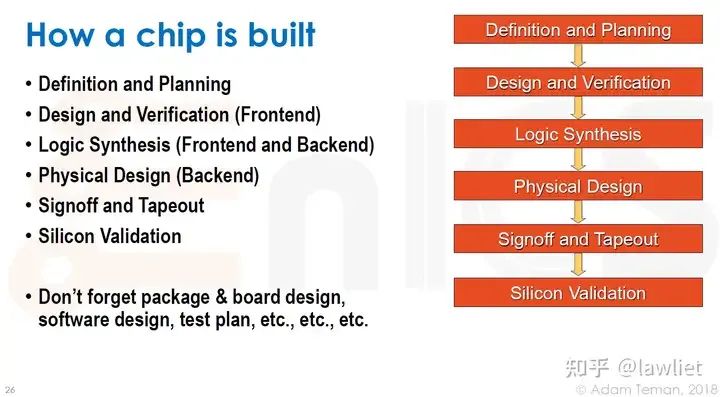

从今天开始,我将和大家一起学习Adam Teman老师的Digital VLSI Design这门课程。这门课程大概就是在讲从RTL到GDS经历了哪些步骤,每个步骤大概做了什么。对于刚接触芯片行业的工程师或者学生而言,我认为这是应该了解的。这可以让你和上下游的同事沟通更Easy,并且这一部分内容面试也非常喜欢考。 第一节课的大纲如下所示:  1、Motivation and Introduction为什么我们要学这门课?我们先看下面这张图,由这张图可以看到,一颗芯片上的晶体管数量是在持续增加的,这也就是所谓的摩尔定律。尽管摩尔定律在放缓,但芯片的复杂度仍然呈现一个上升趋势。这就引出了一个问题,既然芯片越来越复杂,设计芯片的人也没有明显的变多,至少没有像芯片规模那样呈现指数增加。那大家是如何完成设计任务的呢?难道是大家越来越聪明了?   大家的水平提高,这可能是一方面。但最主要的是随着时间的变化,设计模式、方法学等等也有了明显的改善,否则是无法逾越芯片大小和设计能力如此大的GAP。(早期的电路可以手绘电路图,现在的GPU和CPU动不动上百亿的晶体管,还能手绘?)  下面是一个普普通通的中控系统芯片,包含了数字部分,模拟部分,射频部分,还需要有运行在CPU上的软件。这绝不是简简单单就能完成的工作,我们必须改进原始的设计方法。  以下是最常见的思路,设计抽象化、设计自动化、IP复用。这到底是什么意思呢?我们接下来详细介绍。  我们来看一下这门课的教学大纲,现在的你可能对这些名词没有完全掌握,但是没关系。我们来一起学习这些概念。

|

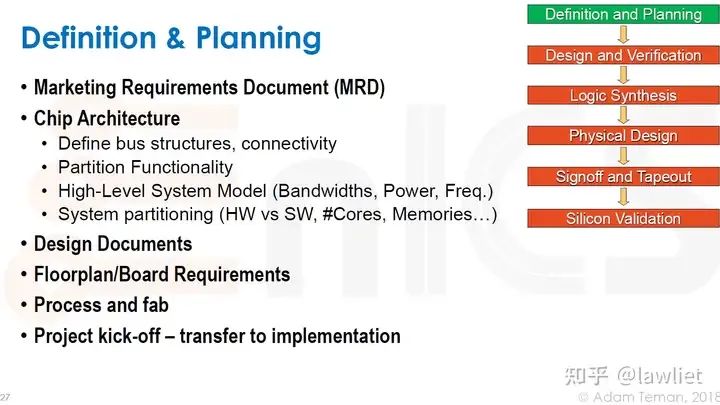

首先是定义和规划阶段。不

首先是定义和规划阶段。不