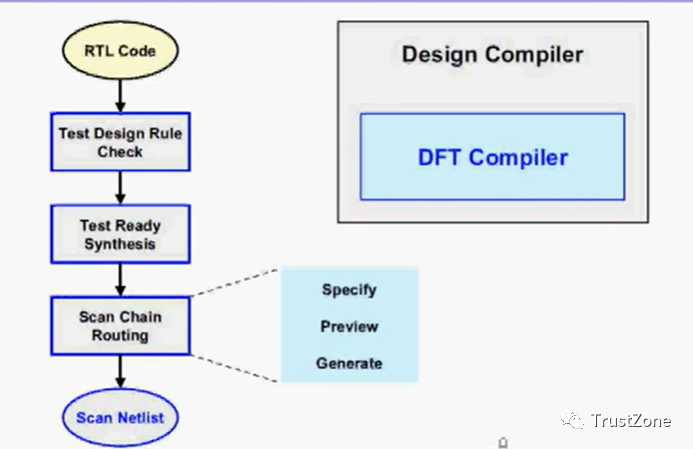

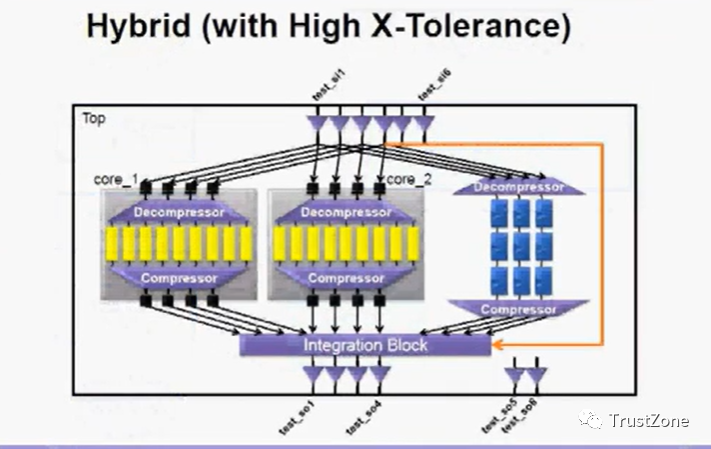

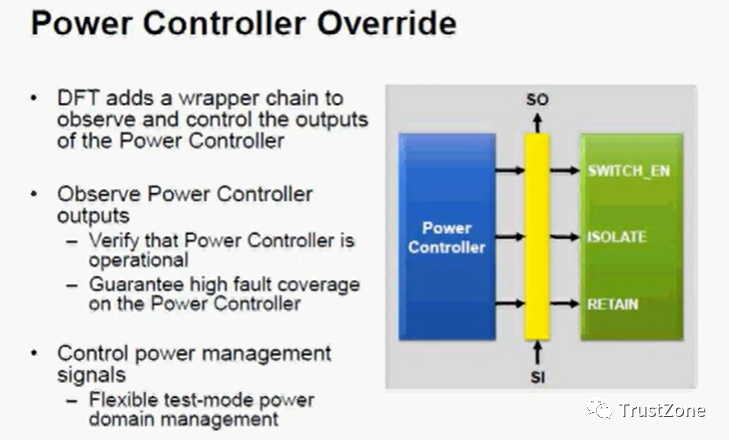

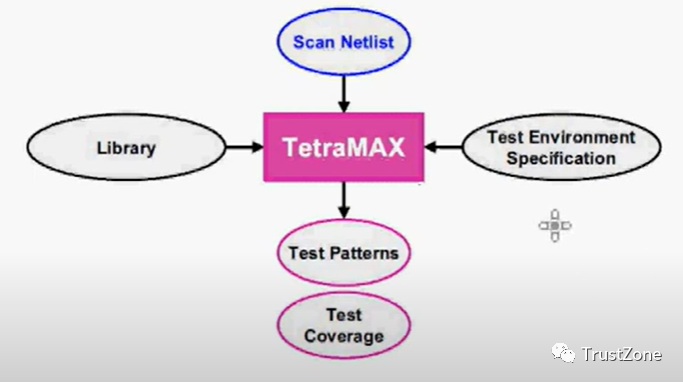

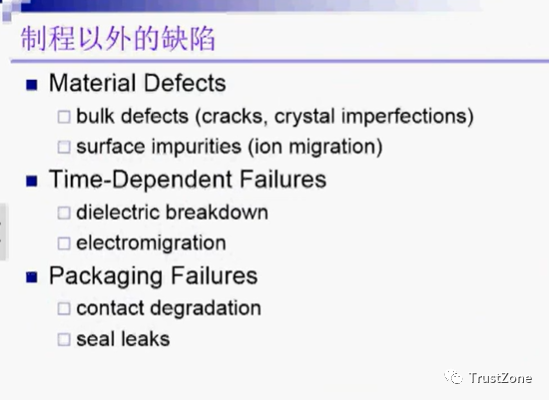

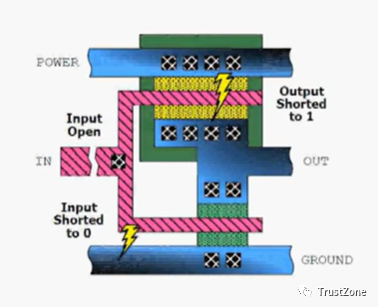

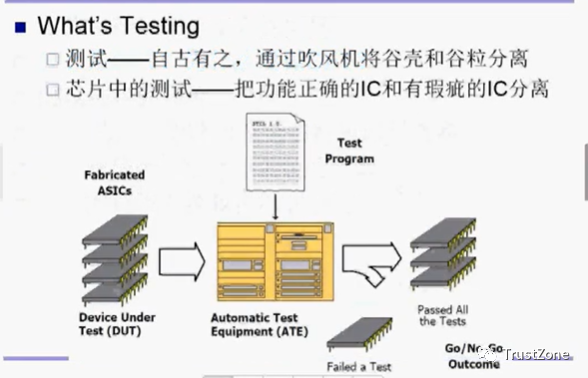

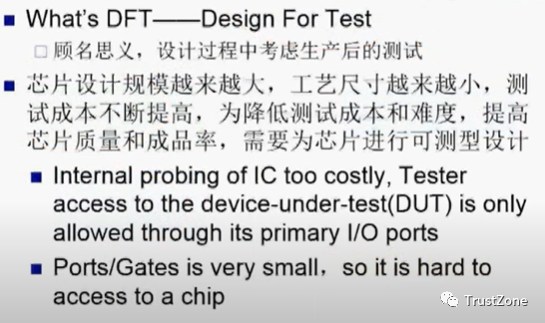

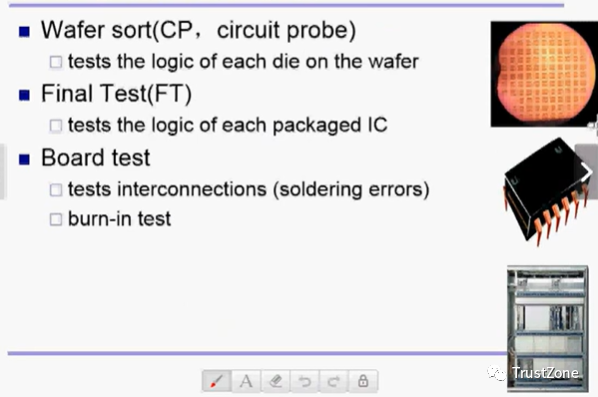

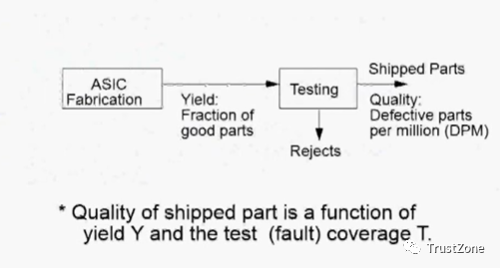

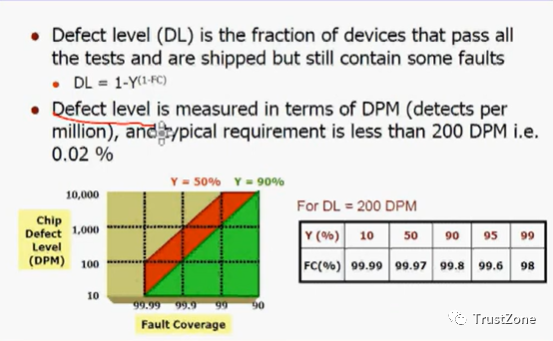

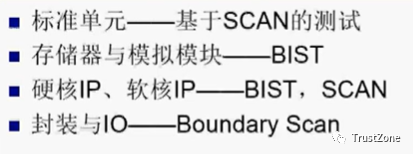

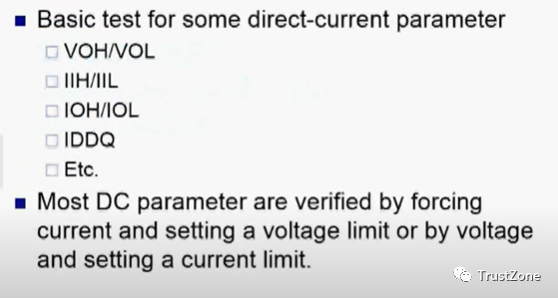

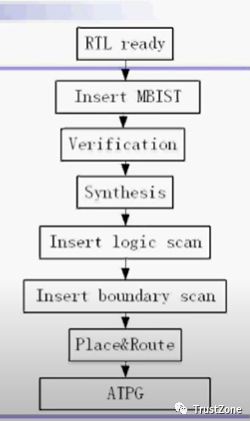

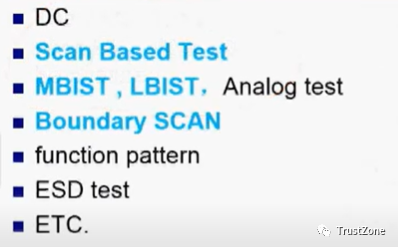

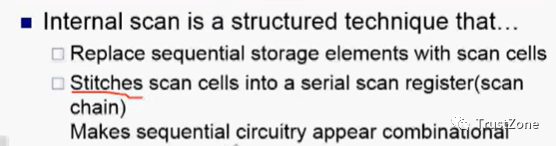

PerfaceHi!这是一篇关于DFT普适性的文章,尝试去站在理论的角度,去看一下DFT技术是如何测试一颗芯片。 ❝ 学习内容的图片来自于油管上的一个视频,是一个做培训的,访问评论区的网站已经失效了,在这里感激视频作者分享的视频。 ❞算是一篇简单的学习笔记,内容东西讲述不甚清晰,极其粗泛。 但是我想呈现给你的是学习DFT:「一个完整的,成体系的学习路线,学习框架。」 你需要的是能自主查询资料,潜心学习,搞懂文章的每个知识点,那么根据这篇文章,你就能延伸出几十篇笔记。 ❝自主找资料去解决的疑惑真的会比别人直接告诉你结果来的更加有映像。 ❝IC行业,务必不要排斥英语!!! 概览篇大纲o 芯片生产过程所引入的问题 o 什么是DFT?为什么要做DFT? o 测试结果的评价 o SOC的DFT策略以及全芯片测试的内容 o DFT在整个IC设计中的位置 o DFT的流程以及每步做的事情

|

7

7