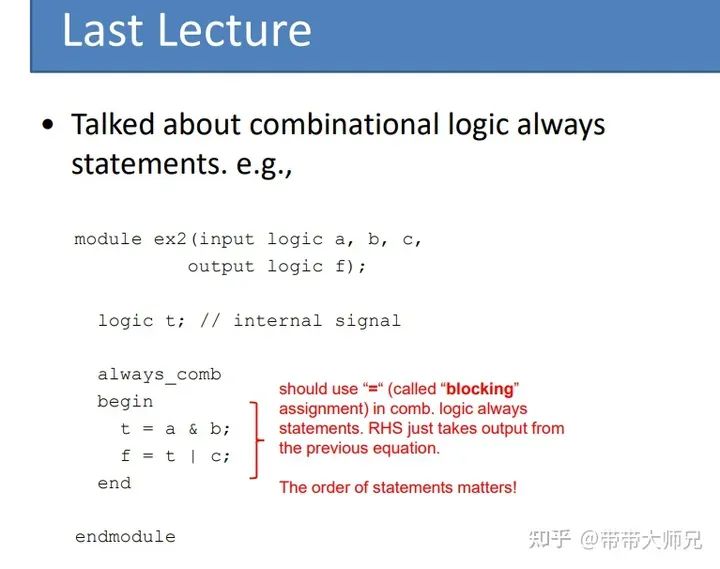

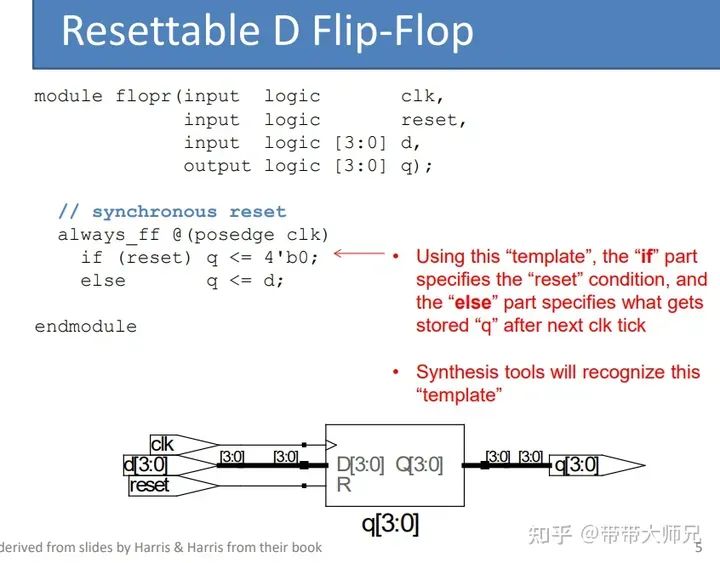

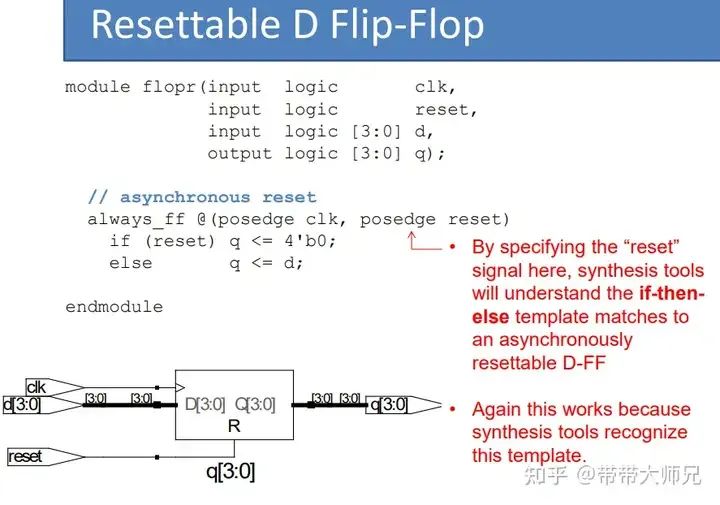

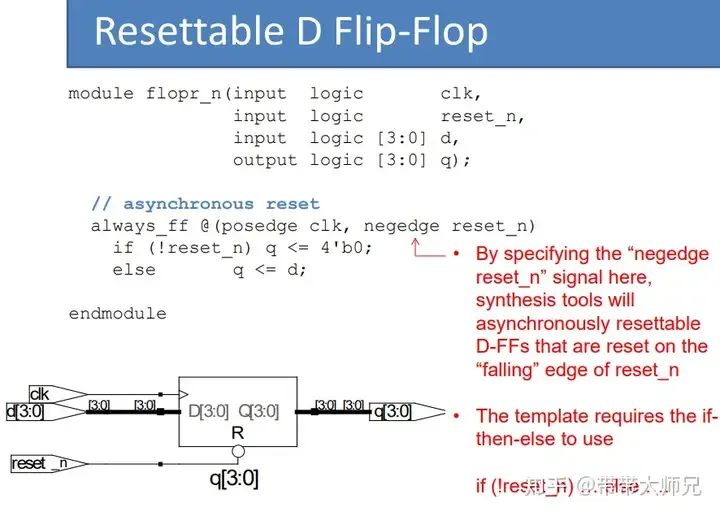

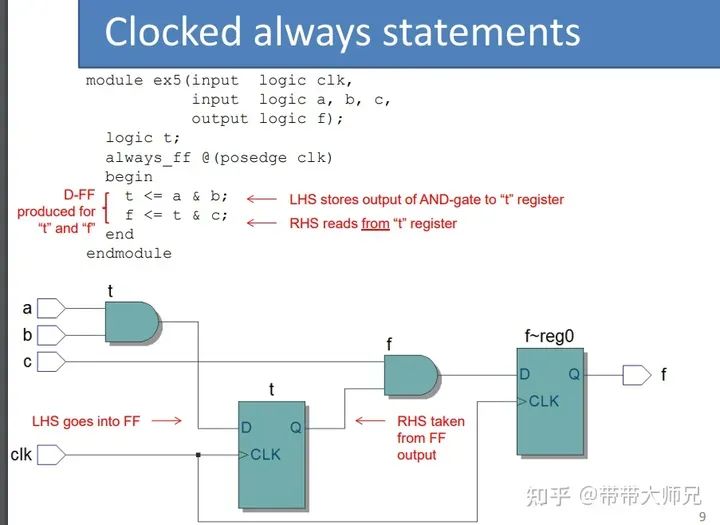

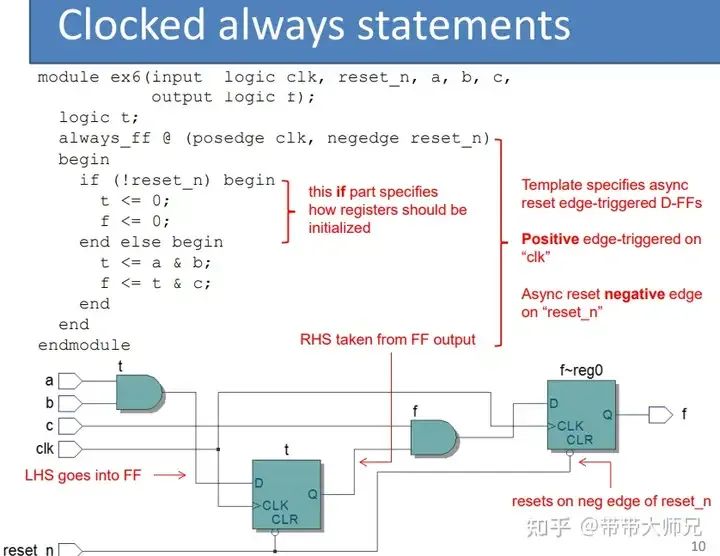

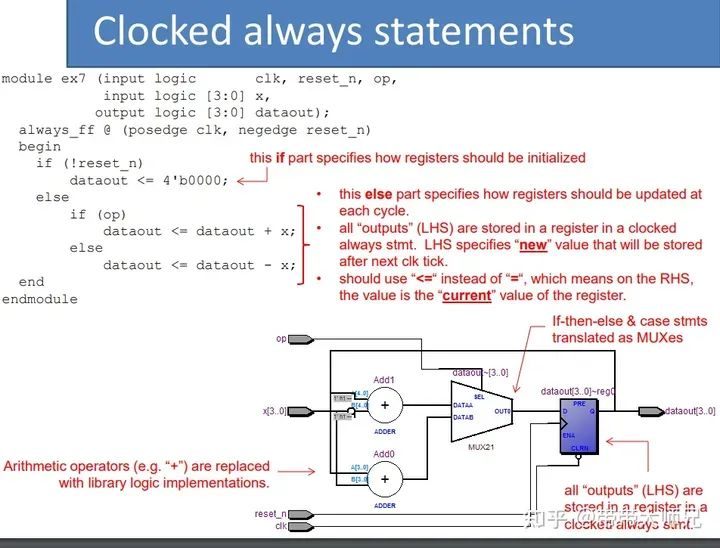

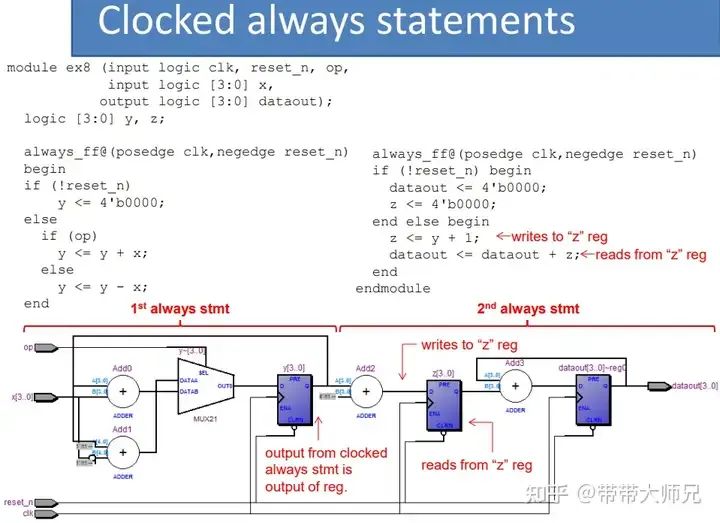

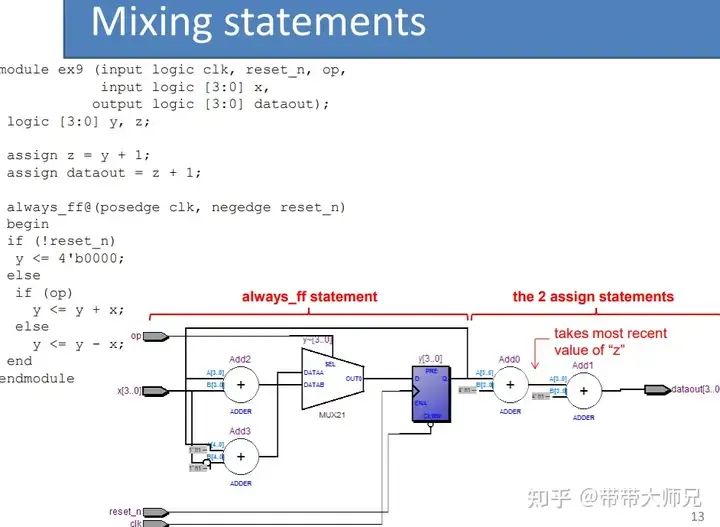

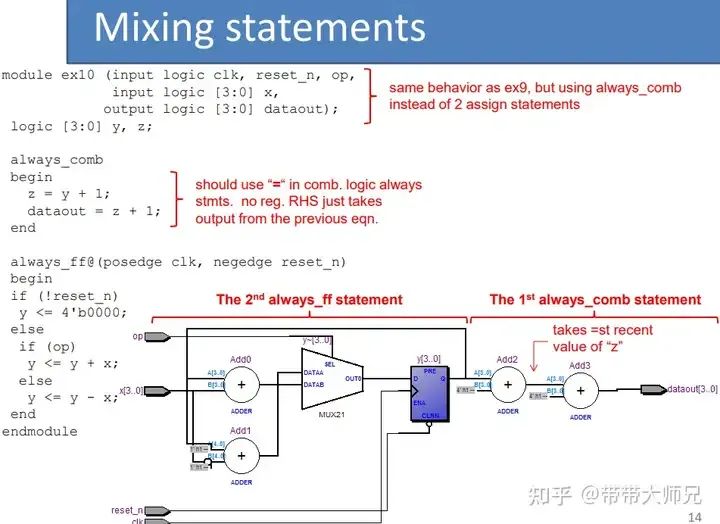

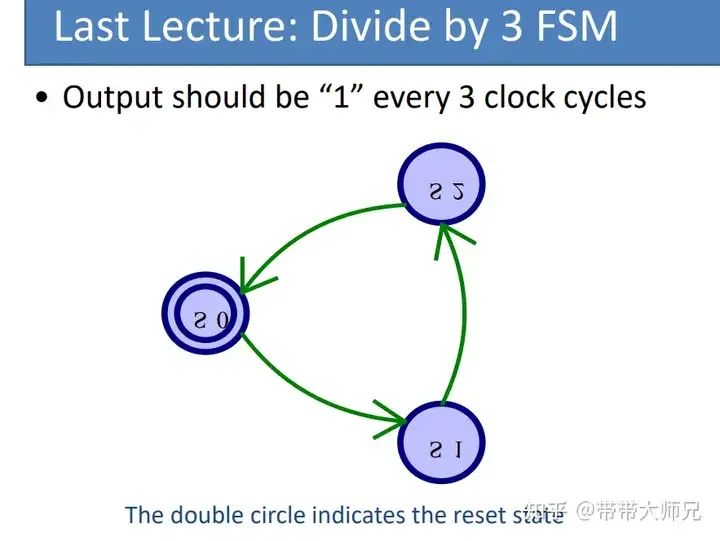

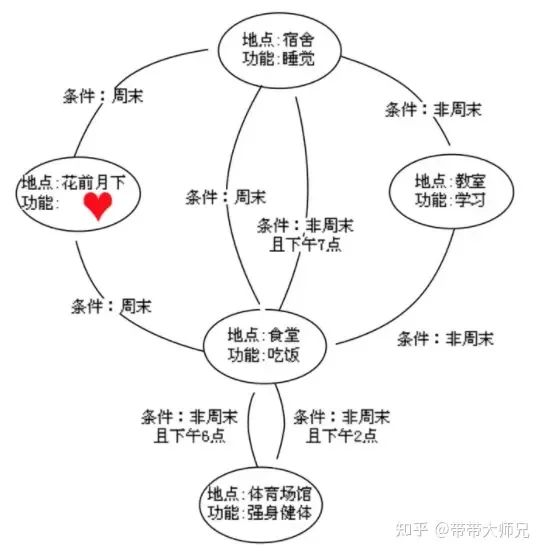

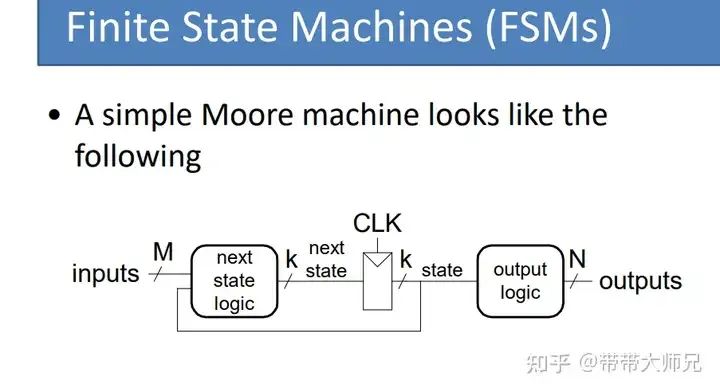

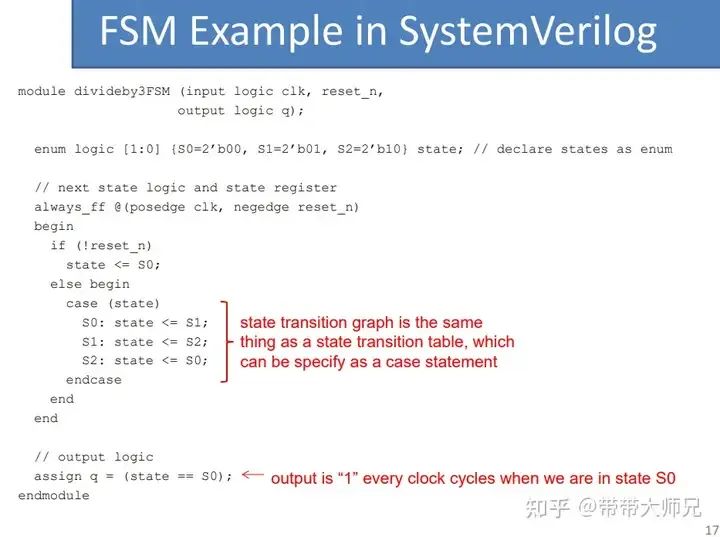

这篇文章带来ECE111第三节课的Slides以及自己的一些补充。 首先回顾了一下上节课所介绍的always_comb语法,该语法用于组合逻辑赋值。需要重点关注的就是阻塞赋值,有关阻塞赋值,可以看我在上一讲中的说明,这里不重复介绍。  然后是这节课的总览。重点讨论”有关时钟的always赋值语句“,该语句会产生”组合逻辑+触发器“。不幸的是,SV没有定义良好的语义来描述触发器和有限状态机,关于这句话,我认为老师可能是要表达SV没有专门的语法去描述状态机,但是这实际上影响不大。关于状态机有专门的写法(idioms,编程模板),综合器可以很好的综合。大家只需要按照模板去写即可,并不复杂。  然后介绍了一下D触发器的代码实现,可以看到时序逻辑一定有时钟信号,并且赋值语句一定要采取"<=",也就是非阻塞赋值。这意味着在下一时钟边沿进行采样。always_ff表明这是一段时序逻辑。@里面表示敏感列表,所谓的敏感列表就是当敏感列表发生变化的时候,会进入该复制逻辑。这里的敏感列表是时钟上升沿。综上可以知道这段代码的含义是,在时钟的上升沿,将d的值送给q(这里其实隐含了个逻辑,就是非时钟上升沿,q的值会保持不变)。显示这就是D触发器的逻辑,因此这段代码会综合成D触发器。D触发器在硬件设计中是非常重要的,目前任何时序逻辑都离不开它。  接下来介绍了一下带复位的D触发器。所谓复位,就是让存储的值回到某一初始状态,典型的是全部置为0。上图中为同步复位,同步复位指的是复位信号只有在时钟的边沿才会触发生效,这段代码的逻辑是。当时钟上升沿到来的时候,如果reset信号为1,则将q的输出置为全0。否则将d的输出送给q。同步复位在现代数字系统中尤其是ASIC用的比较少了,一般是采用”异步复位,同步释放“的方式,我将在后面的文章介绍该方式。但是对Xilinx的多数FPGA,其DSP和BRAM只有同步复位,如果使用者非要用异步复位,则会消耗更多的逻辑资源。这种情况下应该使用同步复位,可以节省资源开销。  接下来介绍了一下异步复位。仔细观察一下代码,和同步复位的区别在于,敏感列表中加入了posedge reset信号。既然如此,大家应该容易理解,当reset拉高的时候,敏感列表发生了变化,因此会进入赋值逻辑,并不需要时钟边沿才可以变化。这种复位与时钟不同步的情况,就称为异步复位。这样生成的D触发器为带异步复位的触发器。  开始介绍的异步复位是高电平有效,既然有高电平有效的,肯定也有低电平有效。我们把posedge改为negedge,并且在reset前面加上!(表示取反)即可,这样便可以在reset的下降沿进行复位。此外,由于工程设计习惯,低电平有效的复位一般在reset最后加上n,表示negative。  有了D触发器这个工具,让我们开始设计时序电路吧。上述的语法很简单,其表达的含义为,将t和c相与,结果送给f。和组合逻辑不同的地方在于,f的值只有在时钟上升沿才会发生变化,并且所采样的值,为上一个周期t和c相与的结果。(那如果t和c一个时钟周期都没有算完怎么办?关于这点大家可以去搜一下建立时间和保持时间的概念,相信看完以后对时序逻辑赋值会有更充分地理解)。除此之外,大家如果按照下面的代码这样写 assign d=t&c; always_ff @(posedge clk) begin f<=d; end 与上面的逻辑是一模一样的。大家观察综合出来的电路图就可以理解了。对于很复杂的逻辑运算,我更推荐第二种写法,这样将触发器的D,Q显式的表示成了两个信号,可控性更高。  然后是一个更加复杂点的逻辑,这里由于采用的是非阻塞赋值,所谓的非阻塞,就是不会阻塞啊!所以前后两句话是并行执行的,没有先后关系的!因此我们观察综合生成的电路。f的输入t为D触发器的输出,而不是a和b直接相与的结果。这一点非常重要,大家多看几遍这段代码和电路图。好好理解一下。也完全可以按照我上面的第二种写法,展开一下,便很容易懂了。  然后介绍了一下带复位的逻辑,这就是非常典型的always_ff写法了,大家可以记住这个模板。  然后介绍了一下嵌套逻辑。同样,这个逻辑是从里面向外面展开。最里面是if/else语句,如果op为1,则xxx,否则xxx。因此会生成一个二选一的MUX。此外该dataout是用在时序逻辑的,因此会由D触发器进行输出。这里引出一个重要的概念,存储。dataout的值存储在D触发器里,每个时钟上升沿会进行更新。此外该逻辑输出的值进而会影响参与输入运算的值,也就是所谓的反馈。这实际上就是隐式状态机了,通过后面的介绍可以知道,状态机实际上就是带反馈的时序逻辑。大家结合代码和电路图仔细看看,应该能够理解。  然后介绍了一下多个always块,仔细观察这两个always块,可以看到右边的z由y+1赋值得到,同时dataout由dataout+z得到,因此可以得到图所示的电路图。实际上只要明白,时序逻辑当中,这些赋值语句,都是由D触发器的右端引过来的输入,这样就很容易得到电路图了。比如z<=y+1。其中的y对应D触发器的Q端,和1相加进入另一个D触发器的D端,通过这样的分析相信大家也可以画出该电路图。(画出电路图以后,对应的信号变化,各个信号关系之间是怎么样的呢?留给大家一个作业,大家下去动手画一下)  然后介绍了一下assign与always_ff混合的情况(其实不能叫混合,仍然是分开的)。这就很简单了,assign只是一根线连接,因此该图应该更好理解。(大家多去思考电路和代码的对应关系,把上面这几幅图都搞懂。always_comb,always_ff以及assign便都可以理解了。实际上这三种语法,占据了我们设计代码的绝大部分)。  然后介绍了一下always_comb和always_ff混合使用的情况,有没有发现和上面的电路图一样?实际上就是一样的。assign和always_comb没有本质区别。  最后说明了一下状态机,状态机全称有限状态机。就是系统有多个状态,满足特定情况,则从其中一个状态到另一个状态,不同的状态做不同的事情!如下图所示,就是一个状态机,是不是很好理解。   状态机电路如图所示,可以分为三部分。一部分用于计算输出逻辑,一部分用于D触发器更新状态,一部分用于计算下一状态。可以看到state会反馈到计算下一状态,这种带反馈的时序逻辑,实际上就是状态机!很多时候代码没有显式的按照状态机代码模板写,实际上也会综合成这样,原因就是如此。包括写一堆if/else,很有可能也综合成了状态机,具体在于有没有反馈!  然后介绍了一下状态机代码写法,图里是两段式状态机写法,我个人更喜欢三段式写法。有关两段式三段式详细区别,下节课再做介绍  |