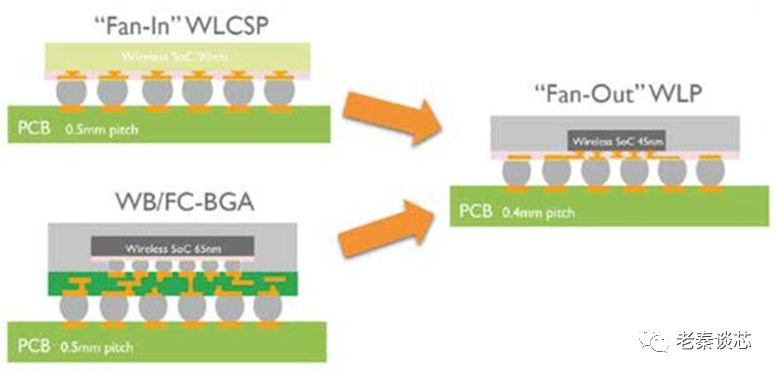

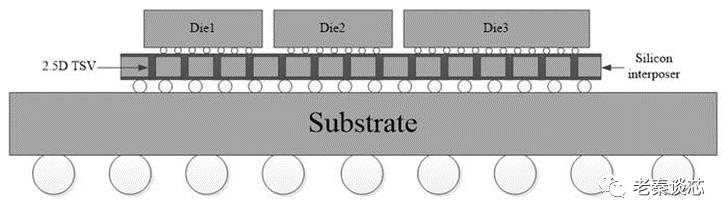

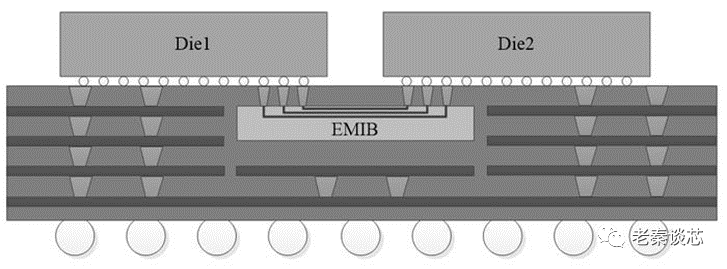

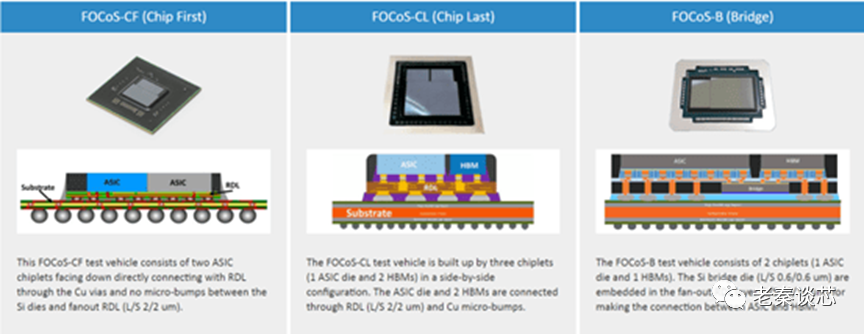

芯片产业是一个分工很细的产业。设计公司做完逻辑和物理设计,将最终设计结果交给芯片生产厂。芯片生产厂通过很多复杂的工序,在一块大的晶圆上做出了许许多多的小芯片。然后,这些小芯片(die)被从晶圆上切割下来,为什么叫die,众说纷纭,有一种说法是因为当初的生产工艺比较差,切割出的芯片经常会作废,die了。实际上die就像一块小玻璃,非常的脆弱,不能直接使用,需要在外面加一层保护壳,也就是我们常听到的“封装”。简单点说,封装技术需要将die固定在基板(substrate)上,然后将die上的引脚连接到芯片外壳的引脚上。 传统封装中最常见的“引线键合(wire-bonding)”封装,即芯片正面朝上固定在基板上,然后通过很细的金属线(通常是金线)把die的引脚连接到基板焊盘上,最后把die/基板/金属线全部密封起来,密封用的材料有塑料,陶瓷等。这种封装技术的优点是生产工艺相对简单,成本较低;缺点是封装完的芯片尺寸比die的尺寸大许多,且芯片管脚数受限。  随着技术进步,发展出“倒装(flip-chip)”技术,晶圆切割前就在die上做好焊点(bump),封装时将die翻转过来,把有bump的那面正对着载板,通过加热加压的方法使bump与载板上的焊点连接好。相比wire-bonding,flip-chip可以有更多管脚数量,封装尺寸接近die的尺寸,并且电气性能,结构特性等更好。但是随着芯片功能越来越复杂,I/O数量急剧增加,在有限的die尺寸下长好所有bump且满足严格的bump间距约束已经越来越难。  后来衍生出Fan-Out WLP(Wafer Level Packages),也叫FOWLP,先将die从晶圆上切割下来,倒置粘在载板上形成了一重组晶圆(Reconstituted Wafer)。在重组晶圆中,生成重新布线层(redistribution layer,RDL)。利用FOWLP技术,bump可以长到die外面,封装后IC也比die面积大(也就是Fan-out)。  上面说的单颗die的封装,将多个die封装在一起,有很多种方式。通常分为2D,2.5D,3D封装。 最直接的方式,将多颗die正面朝下,焊接到基板上,die与die之间的互连就靠基板上的走线。这种办法的缺点是基板上的布线密度低,因此die与die之间的互连受限。 一种解决办法是在基板上加一层“硅中介层”。多颗die正面朝下连接到硅中介层上,die与die的互连布线在中介层完成。也就是说硅中介层充当了die-die互连和die-substrate互连角色。硅中介层可以直接由半导体工艺制造,所以其布线密度远高于基板,这样也就解决die-die互连的问题。说完优点,再来看看缺点,中介层需要承载多颗die,因此其面积大于所有die的面积之和。还有刚才也提到了,中介层也是半导体工艺制作,成本不低,且很难做很大面积。目前,这个技术的代表是台积电的CoWoS。  为了降低中介层的尺寸,英特尔发明了EMIB,将die-die的互连用“硅桥(Si Bridge)”实现,且硅桥嵌入在基板内部,die-substarte的连接通过传统方法实现。这种做法可以大大降低硅中介层的面积,减少成本,减轻多die封装的限制。  2.5D封装还有一种技术,叫FOCoS(Fan-Out Chip on Substrate),顾名思义,在基板上做芯片扇出。硅桥嵌入在扇出 RDL 层中。按照RDL层和芯片贴装两个环节的先后次序不同,FOCoS又可以分为chip-last和chip-first两种。  可以看出,在目前的2.5D封装技术中,所有的die处在一个平面上。所以,注定了一颗芯片中不能有太多die。聪明的技术大牛们想出了3D封装,把die堆叠起来,die间的连接通过TSV(Through Silicon Via)。这种技术好归好,但是难度太高,成本太大。试想一下,在又薄又脆弱的玻璃片上打很多通孔,再把这些玻璃片摞高高,是不是听着就头疼。其实早在NAND flash芯片中就采用了堆叠技术,但是die之间不需要TSV,所以严格说起来不能算3D封装。  具体的3D封装技术那就更多了,各大厂商纷纷推出自己的技术,比如SoIC,X-cube,Foveros等。 最后总结一下,2D封装就像一间大平房,每个房间是一个功能模块;2.5D封装就像一间四合院,在外面看是一个整体,在内部看有多间独立房屋,房屋排列在一个平面上,房屋之间的互连要通过院子,也就是芯片中的中介层;3D封装像是一栋楼房,房屋间的互连是通过垂直的楼梯或者电梯。 |