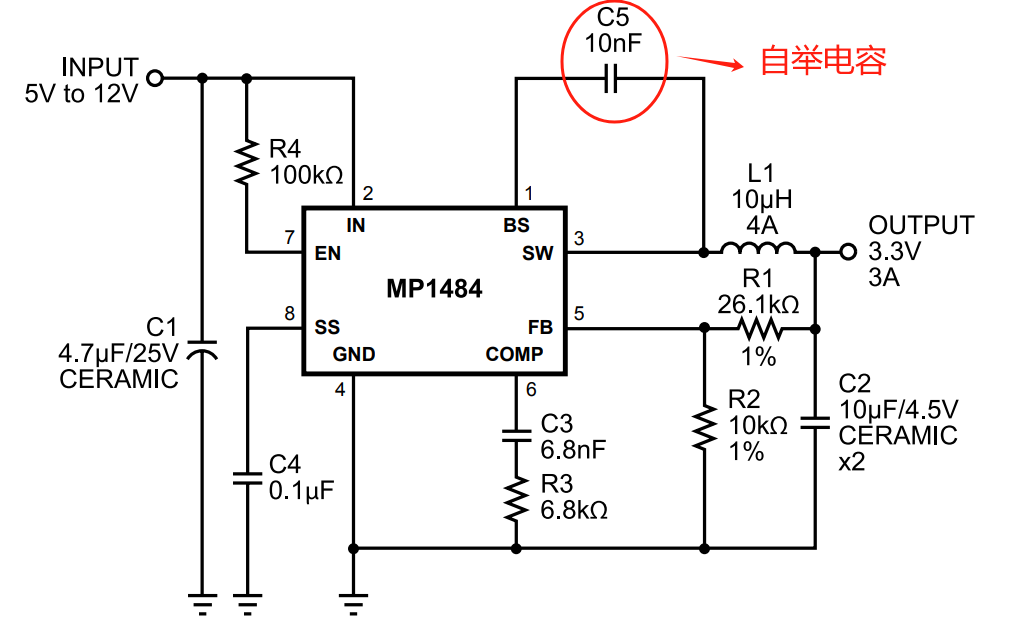

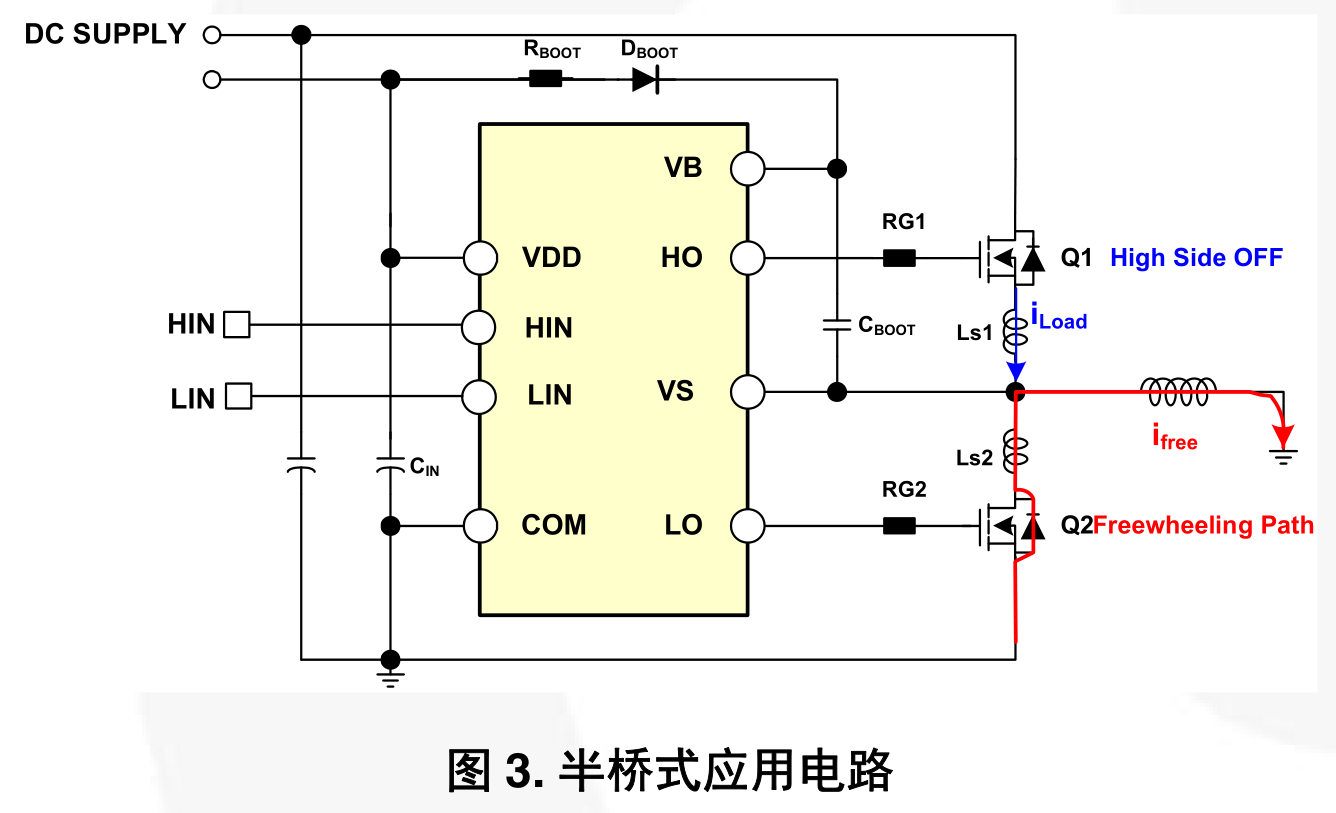

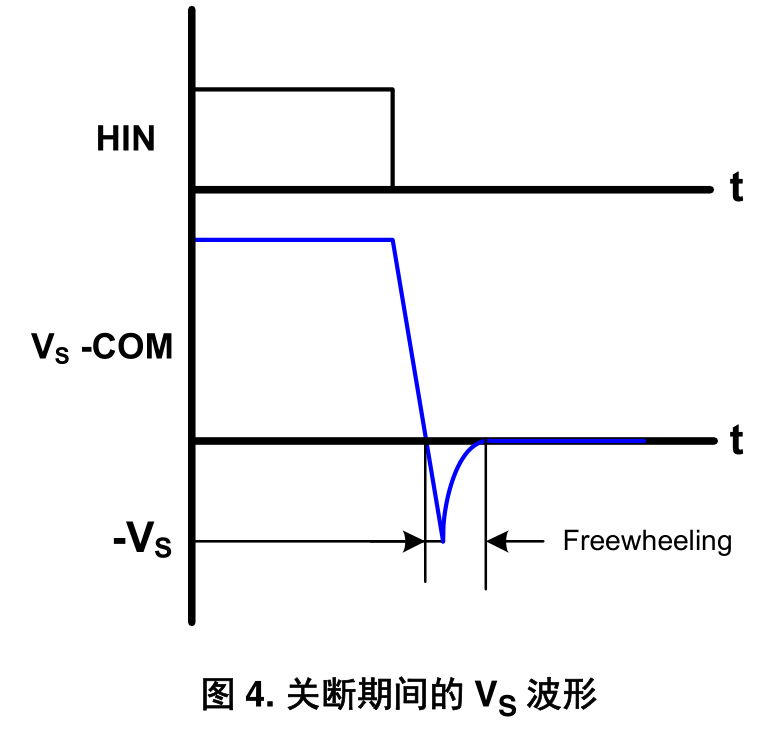

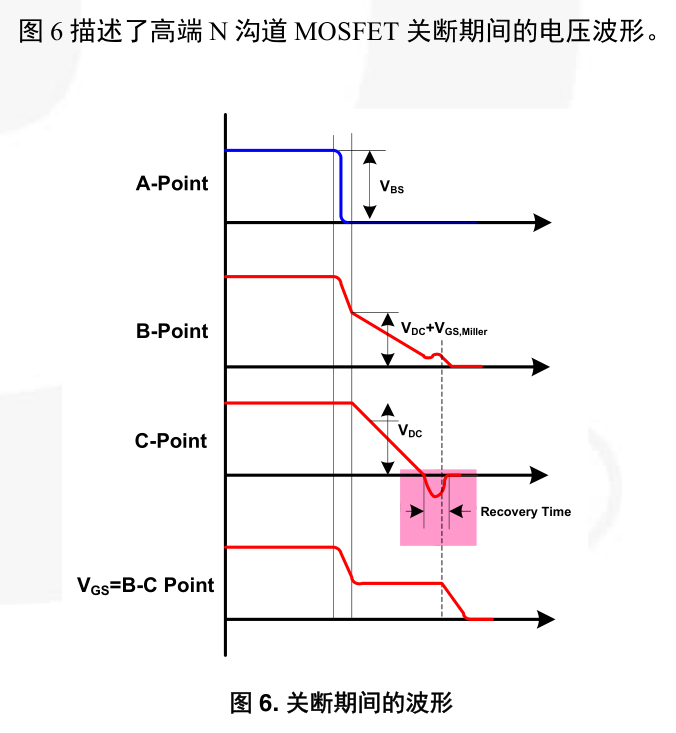

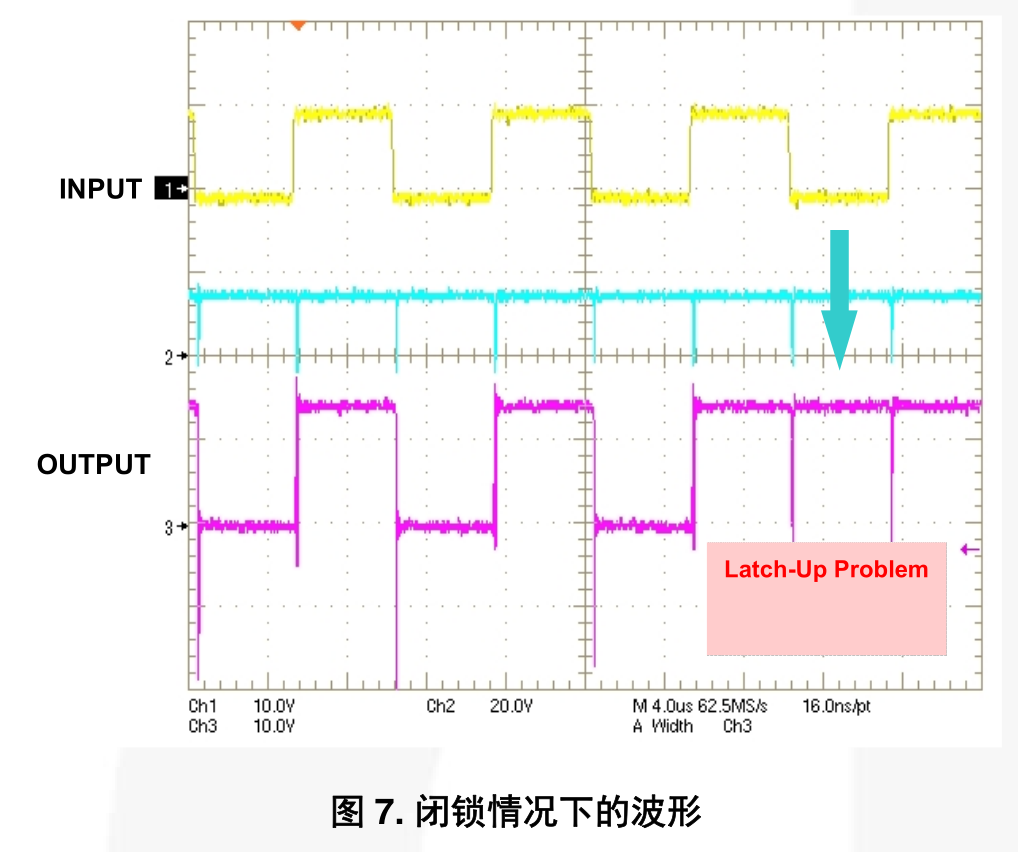

硬件工程师应该都用过buck,一些buck芯片会有类似下面的自举电容,有时还会串联一个电阻。 那么你是否对这个自举电路有深入的了解呢?比如,这个电容的容值大小该怎么选?大了或者小了会影响什么?耐压要求是怎么样的? 最近呢,正好看到ON Semiconductor的一个文档AN-6076,对于自举电路讲得相当的详细了,想深入了解的兄弟可以自己的仔细的读读,源文档可以自己去网上搜,也可以去我的网盘下载(文末会提供下载链接)。以下是文档正文。 1. 介绍 本文讲述了一种运用功率型MOSFET和IGBT设计高性能自举式栅极驱动电路的系统方法,适用于高频率,大功率及高效率的开关应用场合。不同经验的电力电子工程师们都能从中获益。在大多数开关应用中,开关功耗主要取决于开关速度。因此,对于绝大部分本文阐述的大功率开关应用,开关特性是非常重要的。自举式电源是一种使用最为广泛的,给高压栅极驱动集成电路 (IC) 的高端栅极驱动电路供电的方法。这种自举式电源技术具有简单,且低成本的优点。 但是,它也有缺点,一是占空比受到自举电容刷新电荷所需时间的限制,二是当开关器件的源极接负电压时,会发生严重的问题。本文分析了最流行的自举电路解决方案;包括寄生参数,自举电阻和电容对浮动电源充电的影响。 2. 高速栅极驱动电路 2.1 自举栅极驱动技术 本节重点讲在不同开关模式的功率转换应用中,功率型MOSFET 和 IGBT 对自举式栅极驱动电路的要求。当输入电平不允许高端 N 沟道功率型 MOSFET 或 IGBT 使用直接式栅极驱动电路时,我们就可以考虑自举式栅极驱动技术。这种方法被用作栅极驱动和伴发偏置电路,两者都以主开关器件的源极作为基准。驱动电路和以两个输入电压作为摆幅的偏置电路,都与器件的源极轨连。但是,驱动电路和它的浮动偏置可以通过低压电路实现,因为输入电压不会作用到这些电路上。驱动电路和接地控制信号通过一个电平转换电路相连。该电平转换电路必须允许浮动高端和接地低端电路之间存在高电压差和一定的电容性开关电流。高电压栅极驱动 IC 通过独特的电平转换设计差分开。为了保持高效率和可管理的功耗,电平转换电路在主开关导通期间,不能吸收任何电流。对于这种情况,我们经常使用脉冲式锁存电平转换器,如图 1所示。  2.2 自举式驱动电路工作原理 自举式电路在高电压栅极驱动电路中是很有用的,其工作原理如下。 当 VS 降低到 IC 电源电压 VDD 或下拉至地时 (低端开关导通,高端开关关断),电源 VDD 通过自举电阻, RBOOT,和自举二极管, DBOOT,对自举电容CBOOT,进行充电,如图 2 所示。 当 VS 被高端开关上拉到一个较高电压时,由 VBS 对该自举电容放电,此时,VBS 电源浮动,自举二极管处于反向偏置,轨电压 (低端开关关断,高端开关导通)和 IC 电源电压 VDD,被隔离开。  2.3 自举式电路的缺点 自举式电路具有简单和低成本的优点,但是,它也有一些局限。 占空比和导通时间受限于自举电容 CBOOT,刷新电荷所需时间的限制。 这个电路最大的难点在于:当开关器件关断时,其源极的负电压会使负载电流突然流过续流二极管,如图 3 所示。  该负电压会给栅极驱动电路的输出端造成麻烦,因为它直接影响驱动电路或 PWM 控制集成电路的源极 VS 引脚,可能会明显地将某些内部电路下拉到地以下,如图4 所示。另外一个问题是,该负电压的转换可能会使自举电容处于过压状态。  自举电容 CBOOT,通过自举二极管 DBOOT,被电源 VDD瞬间充电。 由于 VDD 电源以地作为基准,自举电容产生的最大电压等于 VDD 加上源极上的负电压振幅。 .4 VS 引脚产生负电压的原因 如图 5 所示,低端续流二极管的前向偏置是已知的将 VS下低到 COM( 地 ) 以下的原因之一。  主要问题出现在整流器换向期间,仅仅在续流二极管开始箝压之前。 在这种情况下,电感 LS1 和 LS2 会将 VS 压低到 COM 以下,甚至如上所述的位置或正常稳态。 该负电压的放大倍数正比于寄生电感和开关器件的关断速度,di/dt ;它由栅极驱动电阻,RGATE 和开关器件的输入电容, Ciss 决定。 Cgs 与 Cgd 的和,称为密勒电容。  2.5 VS 引脚电压下冲的影响 如果欠冲超过数据手册中规定的绝对最大额定值,则栅极驱动 IC 将损坏,或者高端输出暂时无法对输入转换做出响应,如图7和图8所示。 图7显示闭锁情况,即高端输出无法通过输入信号改变。这种情况下,半桥拓扑的外部、主电源、高端和低端开关中发生短路。  图 8 显示遗漏情况,即高端输出无法对输入转换做出响应。这种情况下,高端栅极驱动器的电平转换器将缺少工作电压余量。需要注意的是,大多数事实证明高端通常不需要在一个开关动作之后立即改变状态。  |