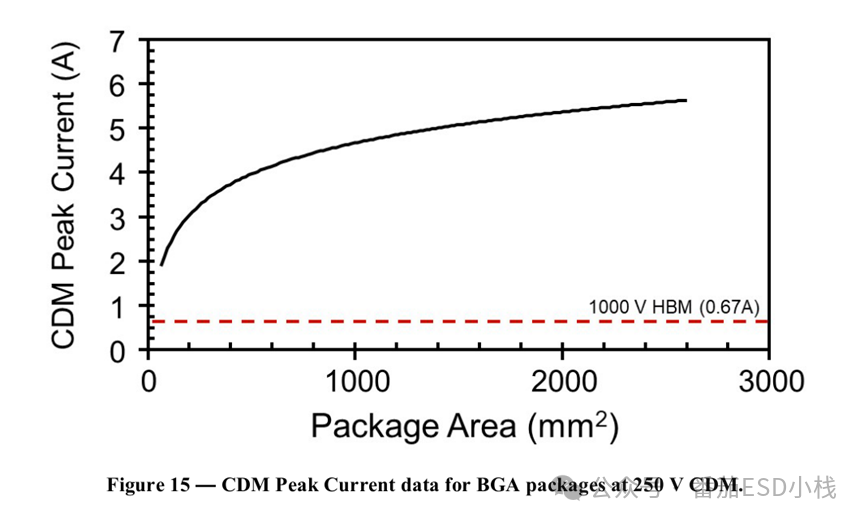

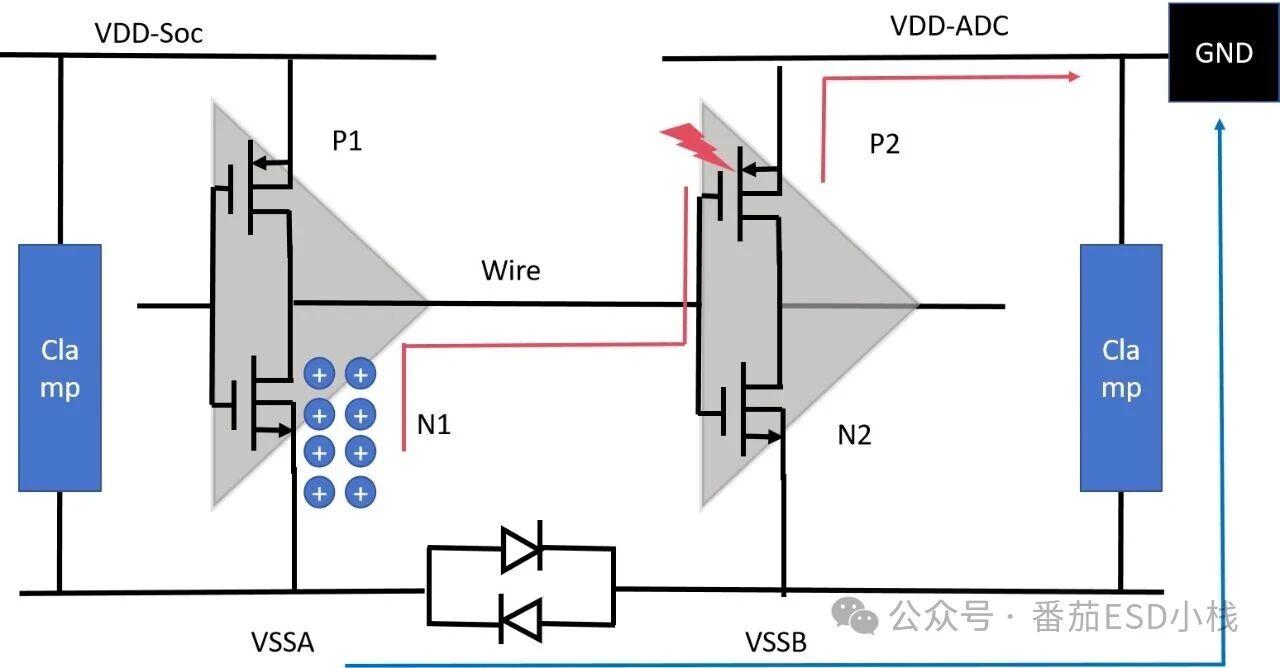

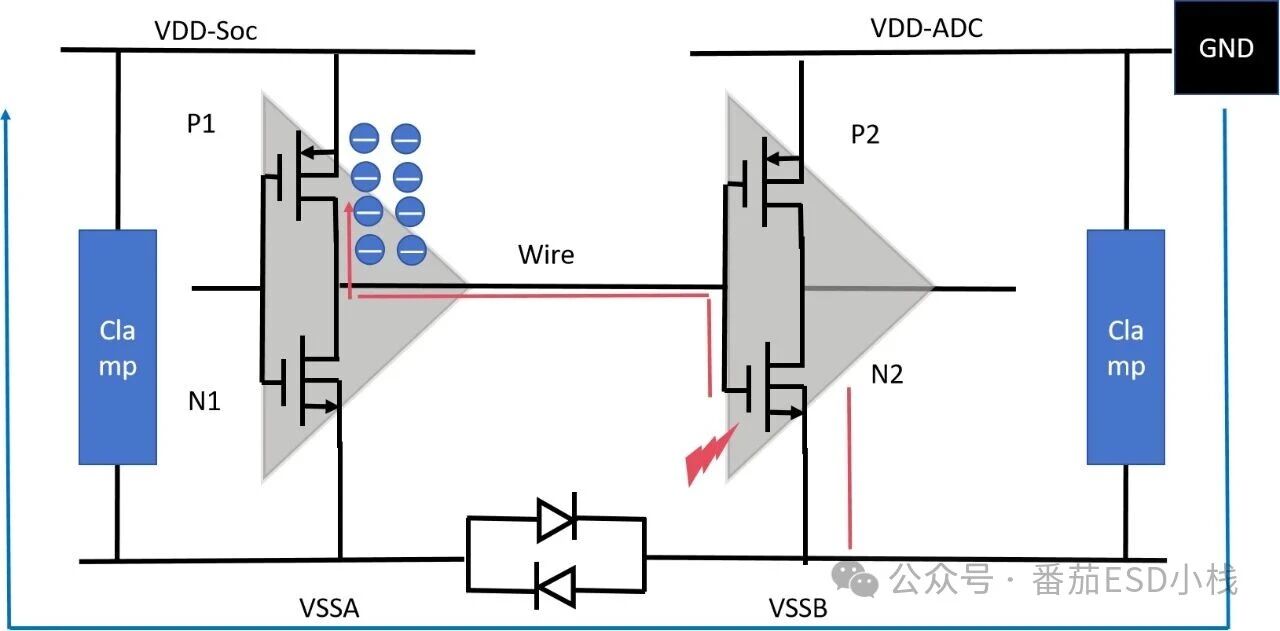

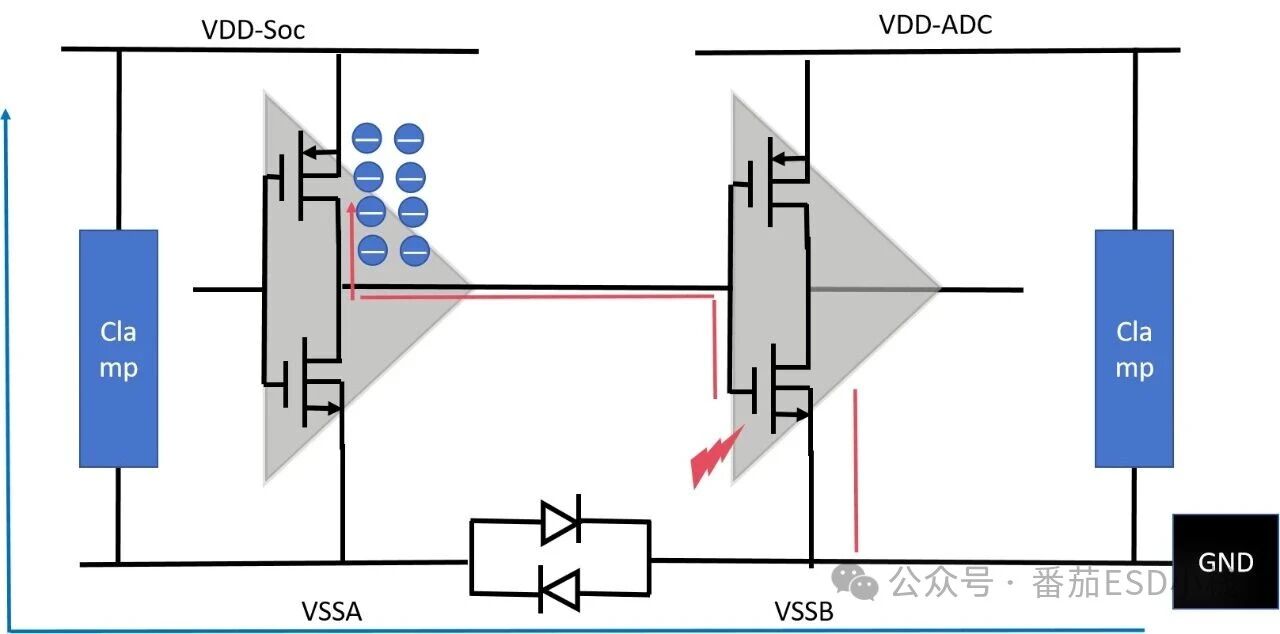

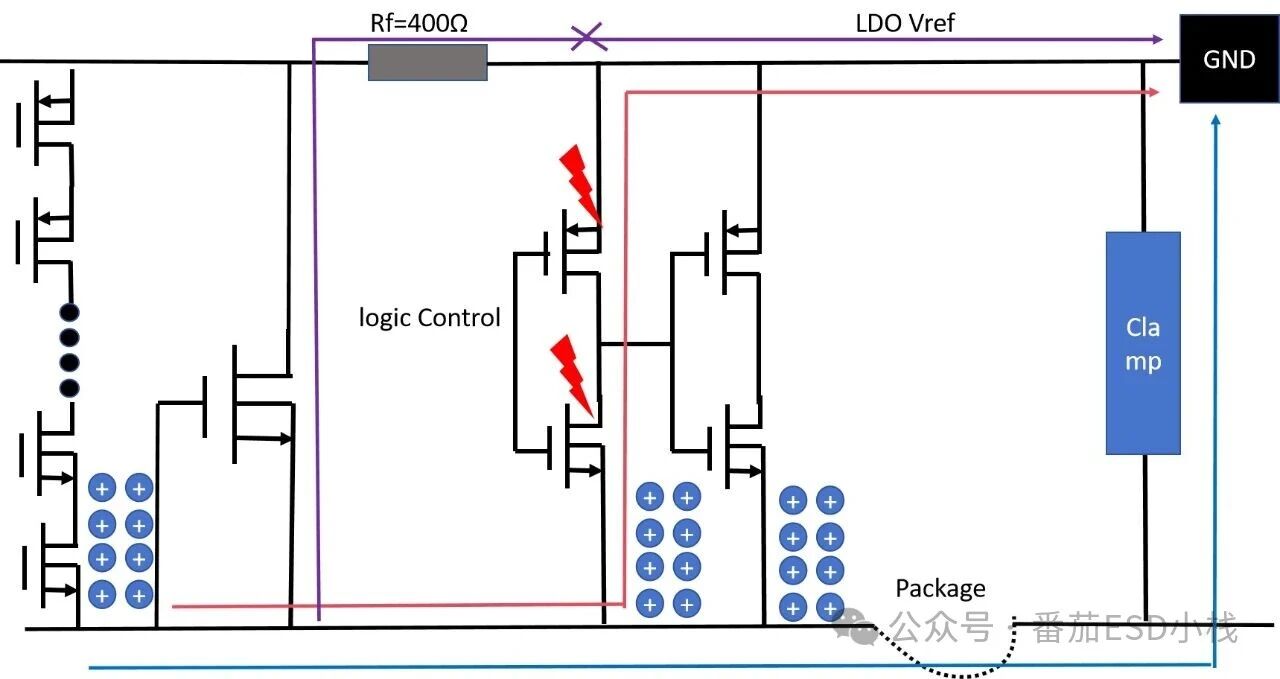

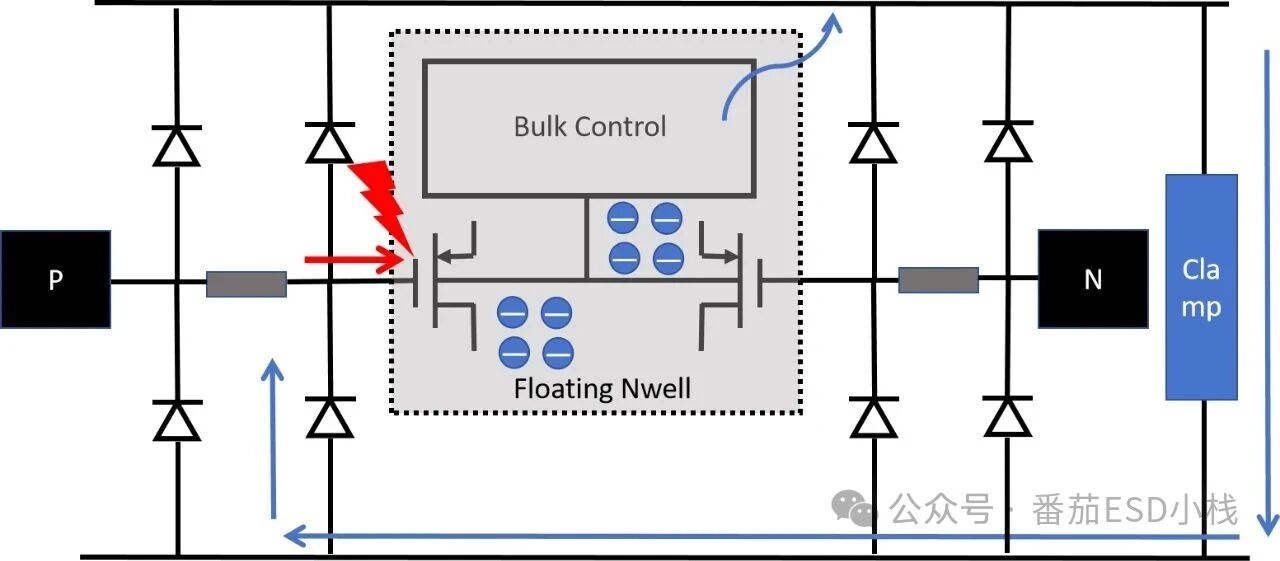

笔者将近大半年没有更新了,最近换了公司,同时要忙结婚的事情,所以也没有时间搞公众号了。以后会慢慢恢复更新的,但是频率肯定不像之前那么密集了。CDM防护一直是ESD防护中的难点,这一期就通过两个实际设计中的案例来讲解CDM产生的机理与CDM防护设计 浅谈ESD防护—CDM(一) 浅谈ESD防护—CDM(二) 浅谈ESD防护—CDM(三)防护设计篇 CDM的风险会随着工艺线宽的降低而骤然增加,很多大线宽工艺都会不考虑CDM防护,但是CDM却是FinFET的工艺的“头号大敌”,根据ESDA官方的统计,CDM在FinFET工艺中造成的良率损失远大于平面CMOS与BCD工艺。CDM中电压与电流的换算关系如图一所示,其换算要比HBM复杂,且不是线性关系。  图一.CDM电压与电流换算关系。 CDM电压与电流的换算与封装面积有关。CDM同一电压在不同封装面积下,对应不同的电流。比如2000mm2的芯片,要想实现CDM 250V的防护等级,芯片得承受将近5A的电流,而对于200mm2的芯片,这一数值会降为2.4A。所以面积也是CDM防护中的重要一环。 这一期就通过三个CDM Fail案例来讲解CDM产生的机理与应对措施。 案例一 案例一是款基于16nm FinFET的Soc芯片,其VDD-ADC/GND-ADC是ADC模块的独立电源地,GND-ADC与SOC的地是通过B2B Diode相连。测试发现VDD-ADC CDM 250V Fail,该案例是典型的跨电压域CDM失效。  图二.案例一跨电压域正电荷失效示意图。 浅谈ESD防护—CDM(二)中从微观层面提到过CDM产生的原因,简而言之便是能带在外电场作用下发生偏移,而费米能级不随电场变化,P型半导体产生正电荷,N型半导体产生负电荷,这部分电荷是下文三个CDM失效的主要因素,除此之外,金属平面,封装平面等都会积累电荷。通过案例一可以在宏观层面讲解CDM的失效机理,当芯片处于正向电场充电时,Psub中会聚集正电荷,当机台对Pin VDD-ADC进行测试时,Pin VDD-ADC接地,Soc域积聚的正电荷需要从VSSA泄放到VDD-ADC。聚集在VSSA上的正电荷正常的泄放路径如图中蓝色所示:Clamp→B2B Diode→Clamp,如果跨电压域没有处理好,阻抗过大,造成这条路径的电压降高于PMOS GOX BV Voltage+0.7V,正电荷就会选择图中红色所示路径:N1→Wire→P2(Gox BV)→VDD-ADC进行泄放,P2 Gate发生击穿,从而造成VDD-ADC端口发生 CDM Fail。  图三.案例一跨电压域负电荷失效示意图。 与之类似,芯片处于CDM负向电场充电时,Nwell中会聚集负电荷,当机台对Pin VDD-ADC进行测试时,Pin VDD-ADC接地,Soc域积聚的负电荷需要从VDD-Soc泄放到VDD-ADC,但是与正电荷不同的是,负电荷的泄放路径与ESD电流方向正好相反,ESD电流需要从VDD-ADC(零电位)到VDD-Soc(负电位)。图中蓝色为常规泄放路径:Clamp→B2B Diode→Clamp。如果跨电压域没有处理好,阻抗过大,ESD会通过图中红色路径:Clamp→N2(GOX BV)→Wire→P1→VDD-Soc,进行泄放,N2 Gate发生击穿,从而造成CDM失效。  图四.案例一跨电压域负电荷失效示意图(二)。 同理,芯片处于CDM负向电场充电时,Nwell中会聚集负电荷,当机台对Pin VSSB进行测试时,Pin VSSB接地,Soc域积聚的负电荷需要从VDD-Soc泄放到VSSB。常规路径如图中蓝色所示:B2B Diode→Clamp,进行泄放。如果跨电压域没有处理好,阻抗过大,ESD会通过图中红色路径:N2(GOX BV)→Wire→P1→VDD-Soc,进行泄放,N2Gate发生击穿,从而造成CDM失效。理解失效机理后续就可以进行针对性的补强。 案例二 如图所示:  图五.案例二失效示意图。 案例二为 14nm FinFET工艺,其失效端口为LDO Verf端口,该端口即为电源端口,又为信号输入端口,所以添加了电阻+GGNMOS的二级防护单元,同时该电路的GND是通过封装与IO GND相连,从而造成GND的回路阻抗过高,虽然都是同一电位,但是因为阻抗过高,造成了类跨电压域的效应。该案例失效模型如下:当内部电路中积聚正电荷后对LDO Vref端口进行测试,常规泄放路径应该如图中紫色路径:通过二级GGNMOS直接到达LDO Vref端口。但是存在一个Rf电阻,造成电荷不会通过这条路径。而另一条路径如蓝色所示,是通过IO Clamp 到达LDO Vref端口, 但是因为封装上的回路阻抗过高,造成这条路径的压降过大,ESD电路会选择第三条红色路径:电荷通过逻辑buffer中的寄生二极管到达LDO Vref,但是逻辑电路不会考虑ESD通过的情况,所以一旦ESD通过buffer进行泄放便会发生失效。因为该电路本身是能接受共地,后续只需要对GND进行补强即可。 案例三 案例三是平面CMOS工艺,失效端口是一对做了二级防护的差分输入端口。如图所示,该端口的PMOS采用了浮阱设计,Nwell不是固定电位。当进行CDM测试时,差分端口其中之一接地,浮阱内的负电荷常规上会按照图中蓝色路径进行泄放:Floating Nwell→ VDD→ Clamp→ GND→ Diode→ P端口。但是因为该泄放路径的回路电阻过高,静电荷选择图中红色路径:直接击穿PMOS Gate进行泄放,所以造成了差分端口CDM失效,如果端口没有设计二级防护,该案例结果可能会更糟。后续通过对Floating Nwell 建立额外的泄放通路将失效问题解决了。  图六.案例三失效示意图。 案例一是比较典型的cdm失效案例,跨电压域是cdm中的高风险设计,需要额外的设计进行补强。而案例二是GND Rail阻抗过高,造成CDM通过内部泄放,案例三是Floating WeLL需要进行CDM补强。 |