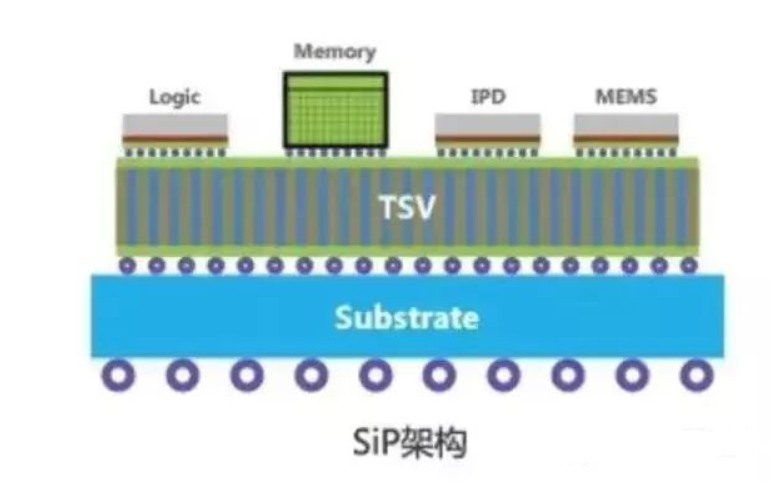

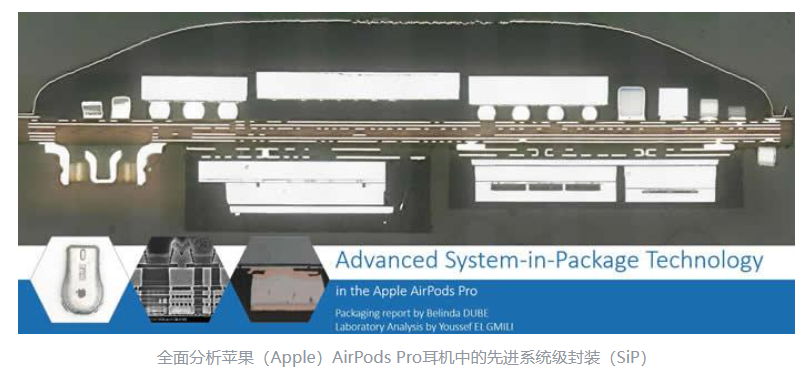

在智能手机、智能手表、物联网设备等电子产品不断追求小型化和高性能的今天,系统级封装(System in Package,SiP)技术正在悄然改变半导体行业的游戏规则。SiP技术定义与核心逻辑 1. 封装技术的范式革新 SiP是通过先进封装工艺将多个功能芯片(如处理器、存储器、传感器)与无源元件集成于单一封装体内的技术。与传统的单芯片封装(如QFP、BGA)不同,SiP突破了"单一芯片+外围电路"的局限,实现了真正意义上的异质集成——例如将7nm逻辑芯片与28nm射频芯片、MEMS传感器共同封装。这种技术路径不同于追求单一晶圆工艺升级的SoC(System on Chip),而是通过三维堆叠(3D IC)、嵌入式基板(Embedded Substrate)等创新手段实现系统级功能。  2.技术实现的三大支柱 异质集成能力:支持不同制程(如5nm逻辑芯片与130nm功率器件)、不同材料(硅、砷化镓、氮化镓)芯片的混合封装 先进互连技术:采用硅通孔(TSV)、微凸块(Microbump)实现垂直互连,线宽可控制在10μm以下 高密度封装基板:使用ABF(味之素积层膜)等材料实现20层以上布线,布线密度达传统PCB的10倍 SiP技术的突破性优势 1.体积与集成度的提升 以Apple Watch Series 6为例,其S6 SiP模块在11.7×9.8mm面积内集成了64个组件,相比分立元件方案节省80%空间。这种高密度特性直接推动了TWS耳机、AR眼镜等穿戴设备的普及。在通信基站领域,Qorvo的5G射频前端模块通过SiP技术将32个射频元件集成到5×5mm封装内,功率密度提升至传统方案的3倍。  2.设计灵活性与迭代速度 SiP技术允许采用"搭积木"式设计: ·开发者可复用已验证的IP芯片模块(如蓝牙/Wi-Fi通信模组) ·支持硬件功能的后期升级(如通过更换存储芯片提升容量) ·缩短产品开发周期约40%(联发科数据显示,智能音箱主控方案开发周期从18个月缩短至11个月) .成本与可靠性的平衡 虽然单个SiP封装成本高于传统方案(约高15-30%),但系统级成本反而降低: ·PCB层数从12层减少至4层,板材成本下降60% ·SMT贴装工序由20道缩减至5道,良率提升至99.3%(日月光统计) ·整体系统故障率降低45%(JEDEC可靠性测试数据) SiP技术的应用 1.消费电子领域 在智能手机中,射频前端模组(如高通ultraSAW)、电源管理单元(如TI BQ系列)已全面SiP化。苹果AirPods Pro的H1 SiP封装尺寸仅4.5×4.5mm,却集成了10核处理器、音频编解码器和运动传感器。更前沿的应用包括: ·小米UWB一指连技术的5mm×5mm定位模组 ·OPPO马里亚纳X NPU与ISP的异构SiP封装  2.高端制造与特种领域 在卫星通信领域,SpaceX星链终端采用SiP技术将相控阵天线单元间距压缩至λ/2(12GHz频段下约12.5mm)。医疗电子方面,美敦力心脏起搏器通过生物兼容性SiP封装,将系统体积缩小至传统方案的1/3。工业自动化场景中,西门子PLC控制器采用耐高温SiP模组,工作温度范围扩展至-40℃~125℃。 技术挑战与未来演进 1.当前面临的技术瓶颈 热管理难题:3D堆叠结构的热流密度可达200W/cm²(相当于火箭发动机喷口水平),需要新型TIM(热界面材料)与微流道散热技术。 信号完整性挑战:在40GHz毫米波频段,封装内传输损耗可能超过3dB/cm,这推动着Low-Dk材料与电磁屏蔽技术的创新。 测试复杂度:传统ATE设备已无法满足1024个以上测试点的需求,催生了基于机器视觉的3D X射线检测技术。 2.下一代技术演进方向  台积电的InFO_SoW(集成扇出型晶圆级系统)技术可将整个12英寸晶圆作为单一封装基板,英特尔推出的Foveros Direct首次实现10μm间距的铜-铜混合键合。学术界的前沿探索包括: ·新加坡IME研究院的玻璃基板TSV技术(传输损耗降低40%) ·德国Fraunhofer研究所开发的有机光电混合SiP方案 ·中科院微电子所的硅基氮化镓异质集成技术 |