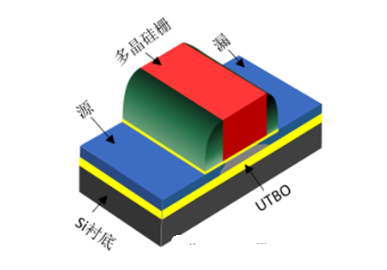

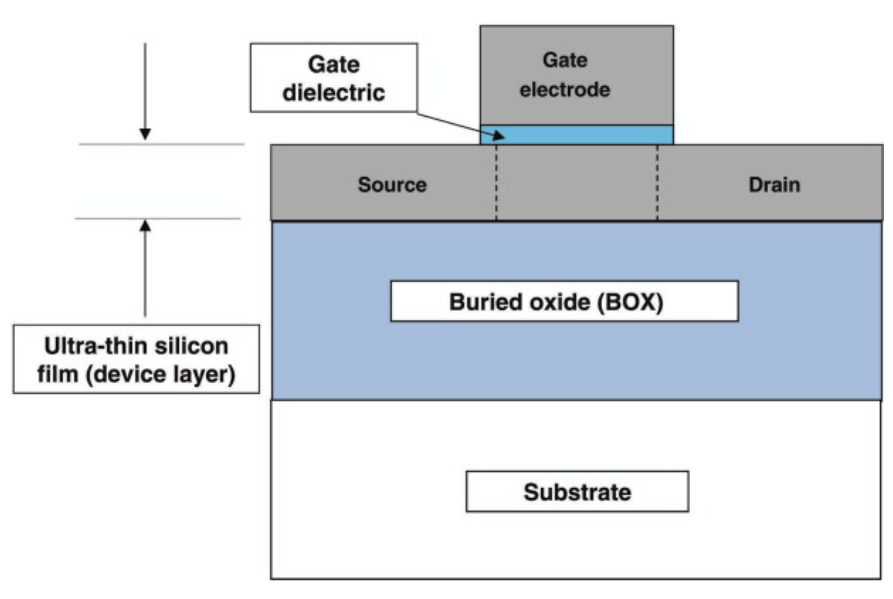

技术起源与核心设计在半导体行业追求更高性能与更低功耗的进程中,传统平面晶体管逐渐逼近物理极限。UTB-SOI(超薄体与埋氧层绝缘体上硅)技术的诞生,正是为了解决这一难题。该技术由华人科学家胡正明教授团队于2000年提出,通过两大核心创新重新定义了晶体管结构: 超薄硅层将沟道厚度压缩至几纳米(≤6nm),使整个沟道区处于全耗尽状态,彻底消除传统工艺中因掺杂不均导致的漏电流问题。与此同时,埋氧层(BOX)在硅衬底与器件层之间形成绝缘屏障,不仅阻断了衬底漏电流路径,还将寄生电容降低30%以上,显著提升高频电路的响应速度。  这种设计既继承了平面工艺的低复杂度优势,又通过结构革新突破了传统体硅器件的性能天花板,成为与FinFET并列的“后摩尔时代”关键技术。 性能突破的关键机制 UTB-SOI的独特结构带来了多维度的性能提升。 1.全耗尽沟道设计 全耗尽沟道设计免除了传统工艺中对沟道掺杂的依赖,避免了随机掺杂涨落引发的阈值电压波动,使晶体管在低至0.4V的电压下仍能稳定工作。这一特性不仅将动态功耗降低50%以上,还大幅提升了芯片在高温、高辐射等极端环境下的可靠性。  2.埋氧层的双重作用 埋氧层的双重作用进一步强化了技术优势:一方面,其绝缘特性彻底隔离了衬底噪声,使芯片抗干扰能力显著增强,特别适用于对稳定性要求严苛的汽车电子与航空航天领域;另一方面,降低的寄生电容使射频前端模组(如5G毫米波器件)的信号传输效率提升20%,为通信技术升级提供了硬件基础。 3.动态体偏置技术 更值得关注的是UTB-SOI独有的动态体偏置技术,通过调节硅膜背面的电压,可实时切换芯片的功耗模式——正向偏置(FBB)时运算速度提升15%,适用于高性能计算场景;反向偏置(RBB)时待机功耗降低至微瓦级,完美适配物联网设备的间歇性工作需求。这种“一芯多用”的灵活性,使其在智能穿戴、边缘计算等领域展现出不可替代的价值。 产业落地与生态构建 从实验室到量产,UTB-SOI技术已形成完整的产业链条。制造端,三星的28FDS工艺与格罗方德的22FDX平台率先实现商用,中芯国际等国内厂商通过技术引进加速布局;材料端,法国Soitec垄断全球90%的SOI晶圆供应,中国通过上海硅产业集团等企业逐步突破衬底制备瓶颈。  在应用层面,该技术正重塑多个行业格局:三星Galaxy智能手表采用28nm FD-SOI芯片,将GPS模块功耗压缩至1mW,续航时间延长10倍;自动驾驶领域,基于UTB-SOI的77GHz毫米波雷达芯片,探测精度较传统方案提升40%;5G基站中,采用该工艺的射频前端模组支持更高频段的同时,将信号损耗降低18%。 未来挑战与发展前景 当前UTB-SOI技术仍面临两大挑战:工艺极限方面,硅膜厚度向3nm推进时,量子隧穿效应导致的漏电问题亟待新材料(如二维半导体)突破;产业生态方面,需要更多设计公司参与IP库建设,以降低中小企业的应用门槛。 长远来看,该技术将与FinFET形成互补格局——FinFET主导高性能计算芯片,UTB-SOI聚焦低功耗、高集成场景。随着12FDX(12nm节点)工艺的成熟,其能效比有望再提升25%,为智慧城市、脑机接口等新兴领域提供底层支撑。 |