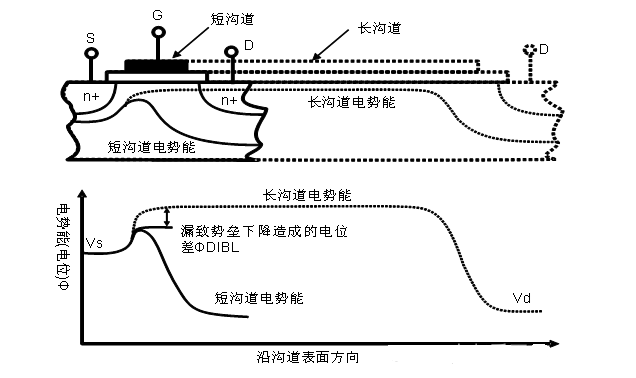

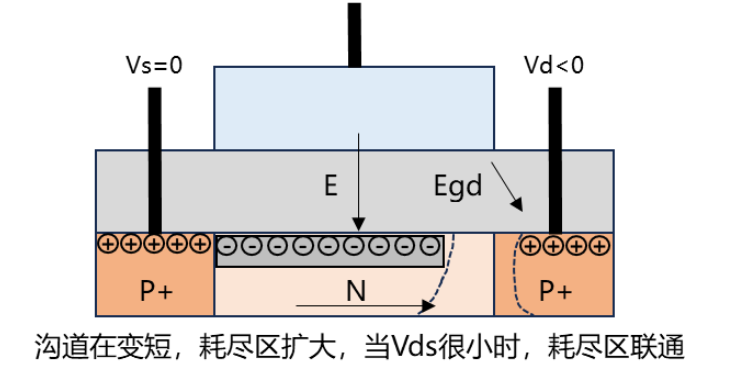

随着智能手机、电脑等电子设备不断追求轻薄化,芯片中的晶体管尺寸已缩小至纳米级(如3nm、2nm)。但尺寸缩小的同时,一个名为“漏致势垒降低效应(DIBL)”的物理现象逐渐成为制约芯片性能的关键难题。什么是漏致势垒降低效应(DIBL) 1.核心定义 DIBL全称Drain-Induced Barrier Lowering(漏致势垒降低效应),指晶体管中漏极电压升高时,源极与沟道之间的电势壁垒被削弱的现象。这会导致晶体管在关闭状态下仍产生漏电流,影响器件可靠性。  2.物理机制类比 想象源极和漏极之间有一道“水坝”(势垒),正常情况下,“水坝”高度足够阻挡电流(关闭状态)。但当漏极电压增大时,相当于“水坝”被外力压垮了一部分,电子便能“翻越”势垒形成漏电流。 3.发生条件 DIBL主要出现在短沟道晶体管中(沟道长度<100nm)。随着晶体管尺寸缩小,漏极电场对源极的干扰增强,传统器件结构难以维持势垒高度。 DIBL如何影响晶体管性能 ① 静态功耗飙升 DIBL导致晶体管关闭时漏电流显著增加。据研究,28nm工艺芯片中,DIBL贡献的漏电占总功耗的30%以上。这不仅缩短设备续航,还引发发热问题。  ② 阈值电压漂移 阈值电压(晶体管开启的临界电压)受DIBL影响会发生偏移。例如,某40nm工艺晶体管的阈值电压可能因DIBL降低50mV,直接导致电路逻辑错误风险上升。 ③ 器件寿命下降 持续漏电流会加速晶体管老化。实验表明,DIBL严重的器件在高温下工作1000小时后,性能退化速度比正常器件快2-3倍。 如何应对DIBL挑战 ① 材料革新:高介电常数(High-k)介质 传统二氧化硅(SiO₂)栅极介质的物理极限为1.2nm(约5个原子厚度),进一步减薄会加剧DIBL。英特尔在45nm节点引入铪基(HfO₂)High-k材料,在相同厚度下介电常数提升3倍,有效抑制漏电场穿透。 ② 结构升级:FinFET与全环绕栅极(GAA) FinFET(鳍式场效应晶体管):通过将沟道竖立为“鳍”状,三面包裹栅极,使栅极对沟道的控制力提升50%以上,显著降低DIBL(22nm节点后广泛应用)。 纳米片GAA:三星3nm工艺采用多层堆叠纳米片,栅极360°环绕沟道,进一步将DIBL导致的漏电降低至FinFET的1/5。 ③ 工艺优化:超浅结与应变硅技术 通过离子注入形成超浅源漏结(深度<20nm),减少漏极电场对沟道的横向干扰;引入应变硅技术(如GlobalFoundries的SiGe通道),提高载流子迁移率,降低工作电压需求。 |