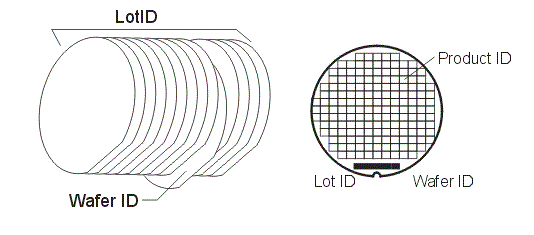

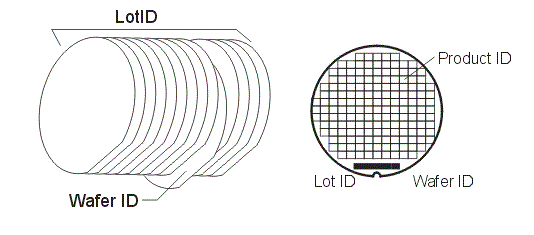

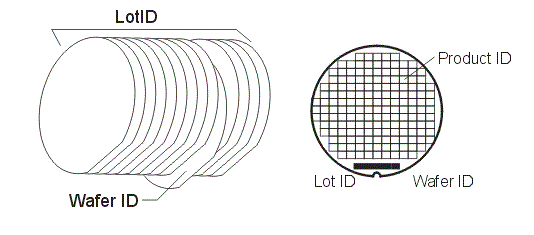

一个lot为啥是25张wafer?

时间:2025-03-26 20:12来源: 漫谈大千世界 作者:ictest8_edit 点击:

次

在半导体制造中,一个批次(lot)通常包含25张wafer,这一标准是设备设计、生产效率、行业协同和历史演进共同作用的结果,体现了“标准化”与“优化”的平衡。

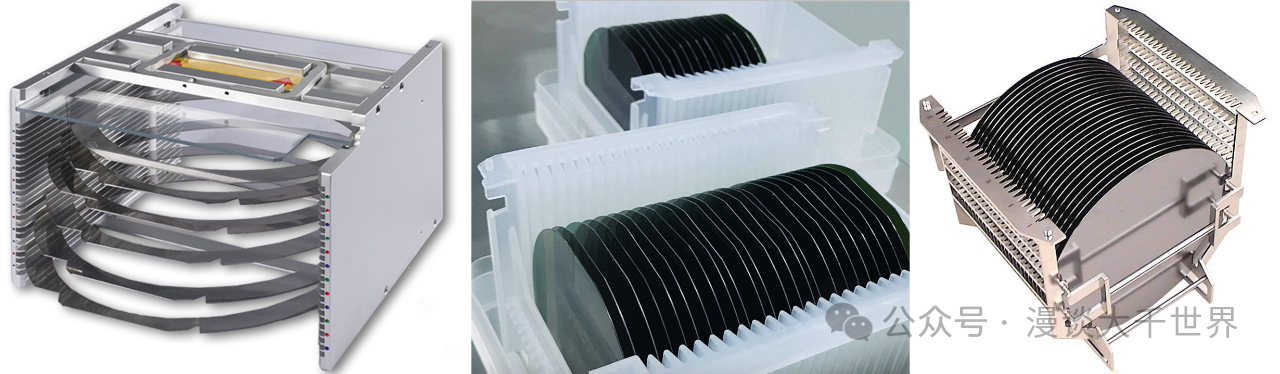

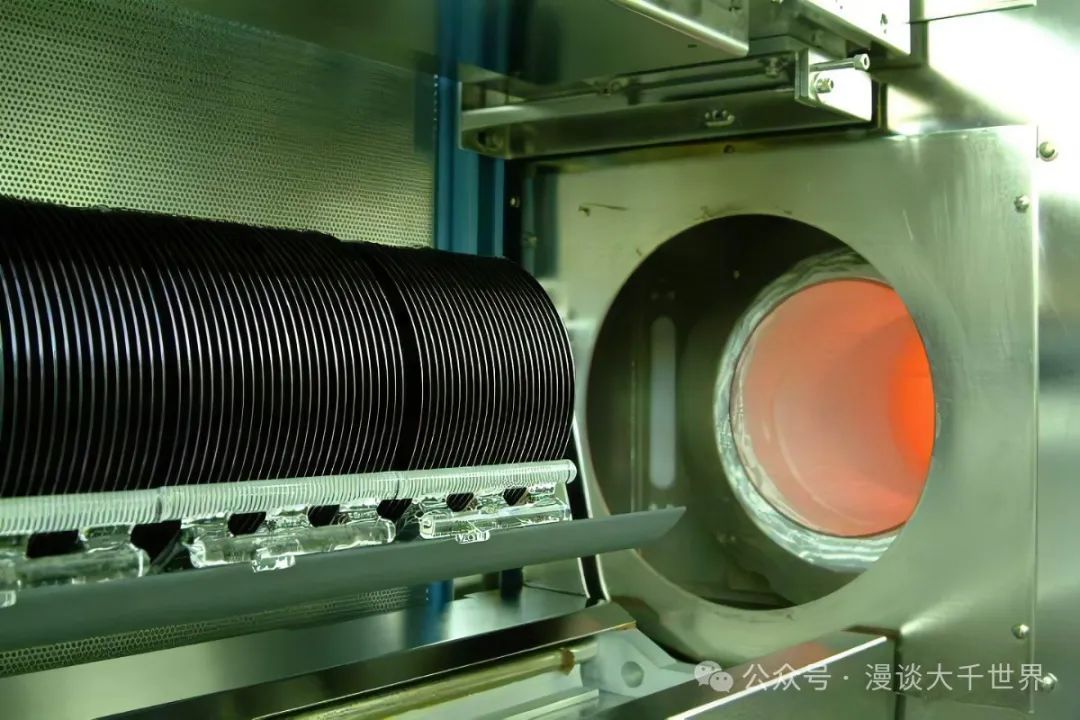

1. FOUP容量的物理学限制

· 重量临界点:12英寸晶圆单重约0.3kg,25片总重7.5kg(含FOUP壳体)。这一重量处于临界点:(1)人体工程学极限:操作员紧急干预时,8kg为单臂安全负荷阈值;(2)AMHS机械臂:碳纤维夹具在8kg负载下可保持微振动<0.1μm(满足纳米级制程要求)。

· 热力学平衡:FOUP内需维持氮气正压差(0.5-1.2Pa),25片间距6.35mm优化了气体流通效率与微粒沉积概率(<0.1 particles/cm³)。若增加片数,气流受阻可能导致污染风险上升。

2. 设备利用率的数学建模

在光刻机经济模型中,批量处理存在最优解:

设备综合效率OEE = (Lot处理时间)/(Lot处理时间 + 换型时间)

当晶圆厂采用ASML TWINSCAN NXT:2000i时:

· 单晶圆曝光时间:120s

· 批次校准时间:600s(含掩模版校准、激光器预热)

· 25片总耗时:120×25 + 600 = 3600s

· 理论最大OEE = (3000)/(3600) ≈ 83%

·

若批量减至13片,OEE将降至73%,导致单晶圆成本上升18%;批量过大则可能延长生产周期,降低灵活性。

3. 缺陷率与质量控制的统计约束

采用泊松分布模拟晶圆缺陷概率:

· P(k defects) = (λ^k e^{-λ})/k!

假设单晶圆缺陷率λ=0.1(先进节点良率标准):

· 25片中出现≥1缺陷的概率:1 - e^{-0.1×25} ≈ 92%

· 但通过批次级RTA(快速热退火)等补偿工艺,可将缺陷影响控制在±3σ内;

相比之下,50片批次的缺陷扩散风险指数增长,导致返工成本呈二次曲线上升。

4. 历史沿革与技术进步

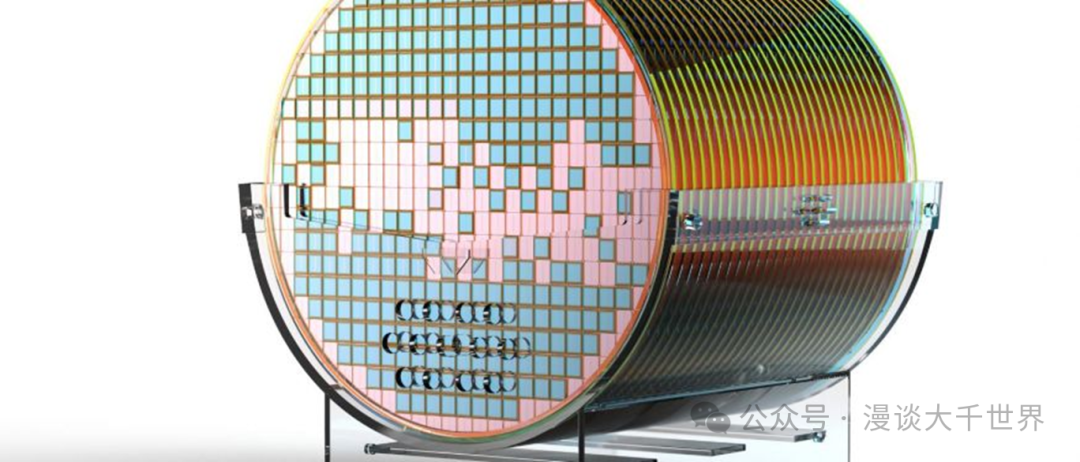

· 早期晶圆尺寸和处理数量的变化:早期晶圆尺寸较小(如6英寸),每批处理数量更多(如50片)。随着晶圆尺寸增大(12英寸成为主流)和自动化提升,25片逐步成为平衡搬运效率与设备负载的折中方案。

· 自动化机械臂的普及:自动化机械臂(AMHS)的普及也推动标准化,25片与自动化传输系统的速度、稳定性相匹配。

· 主流设备厂商和晶圆厂的普遍采用:主流设备厂商(如ASML、Applied Materials)和晶圆厂(如台积电、三星)普遍采用25片标准,上下游设备(传输、检测系统)均围绕此设计。标准化降低了供应链协调成本,提升了行业整体效率。

5. 例外情况

· 特殊工艺或研发阶段:研发线采用"Mini-Lot"(5-10片)时,需支付溢价:光罩使用效率下降40%;计量设备需加载动态采样算法(如SEMulatorX虚拟量测);

· 特殊工艺(如GaN-on-SiC):采用13片批次,源于:外延生长炉管热区长度限制(≤500mm);MOCVD反应腔驻波场均匀性要求;

· 部分设备兼容性:某些老式机台或特殊设备可能支持13片、26片等非标容量,但25片仍是行业主流。

|

------分隔线----------------------------