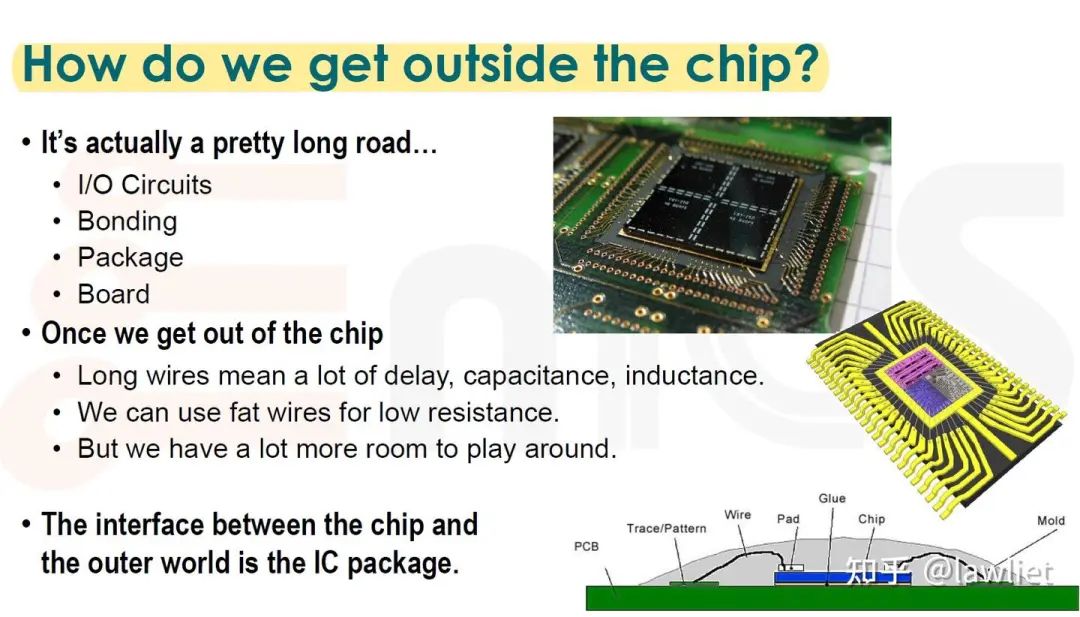

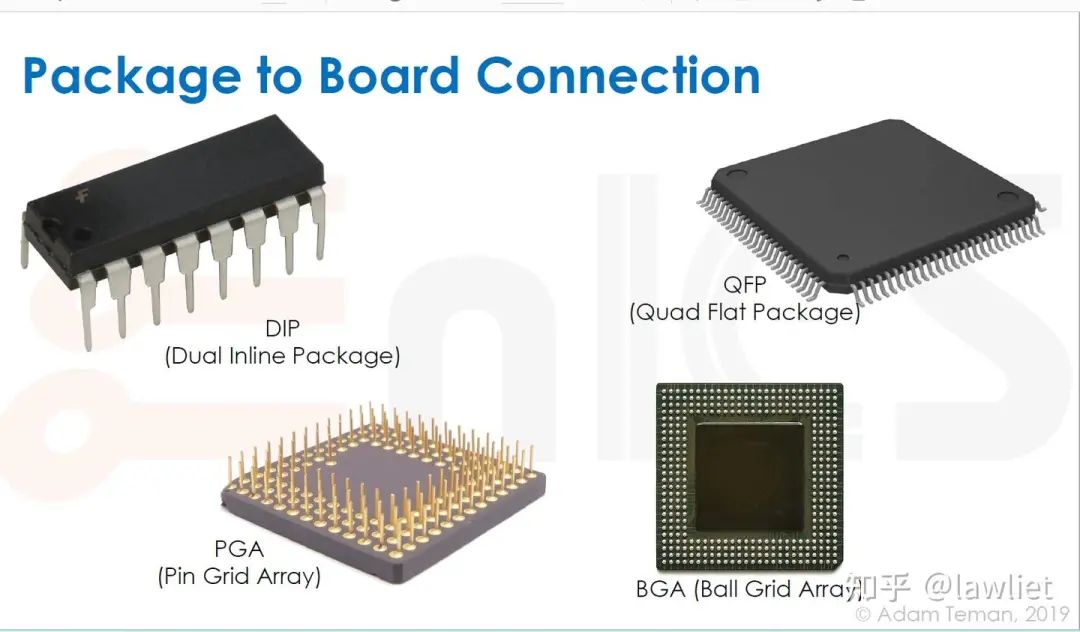

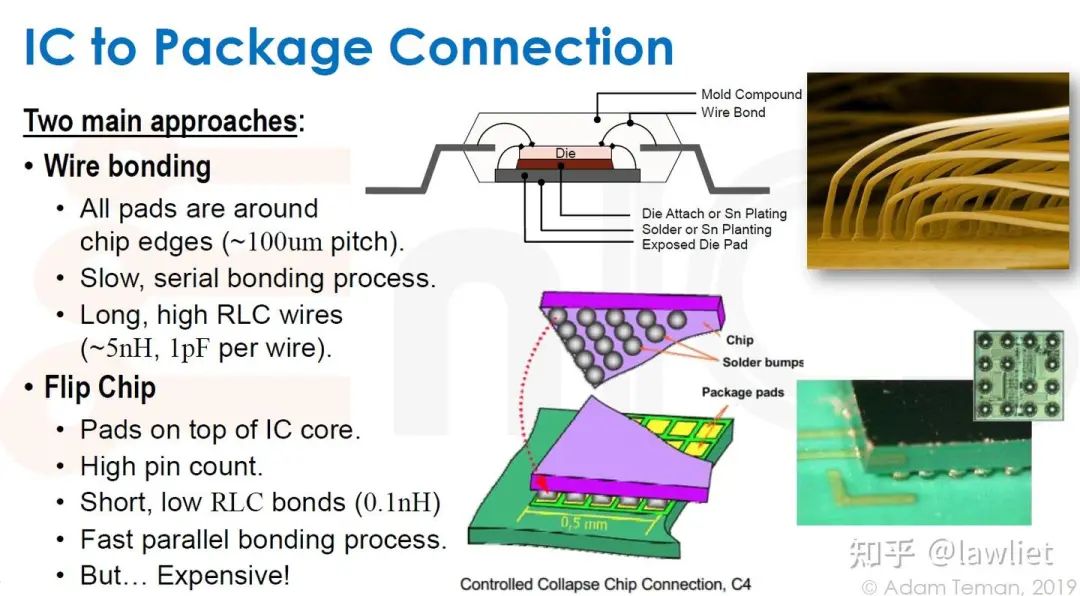

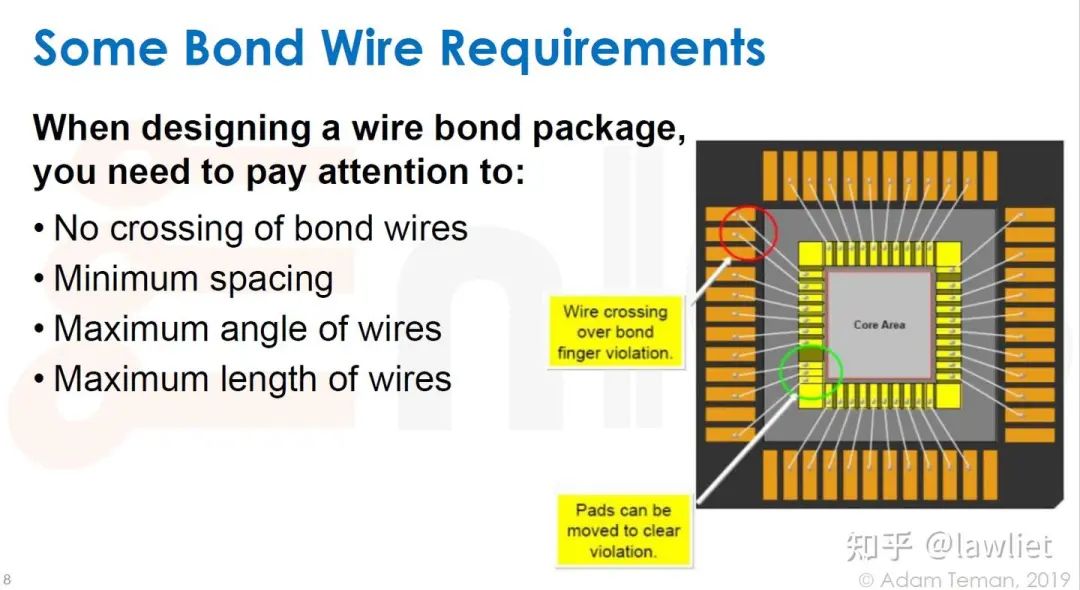

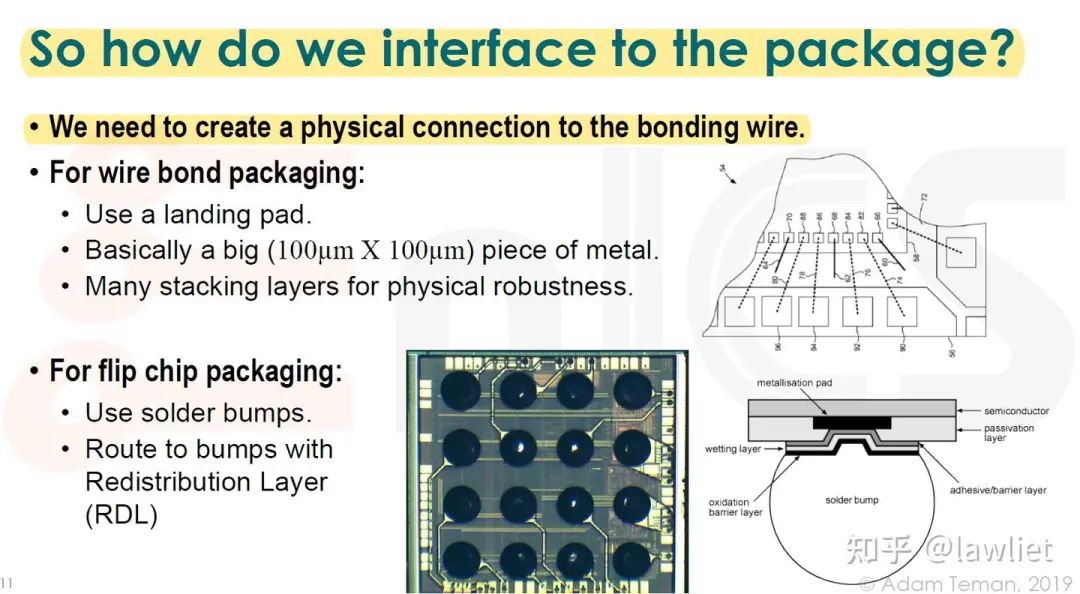

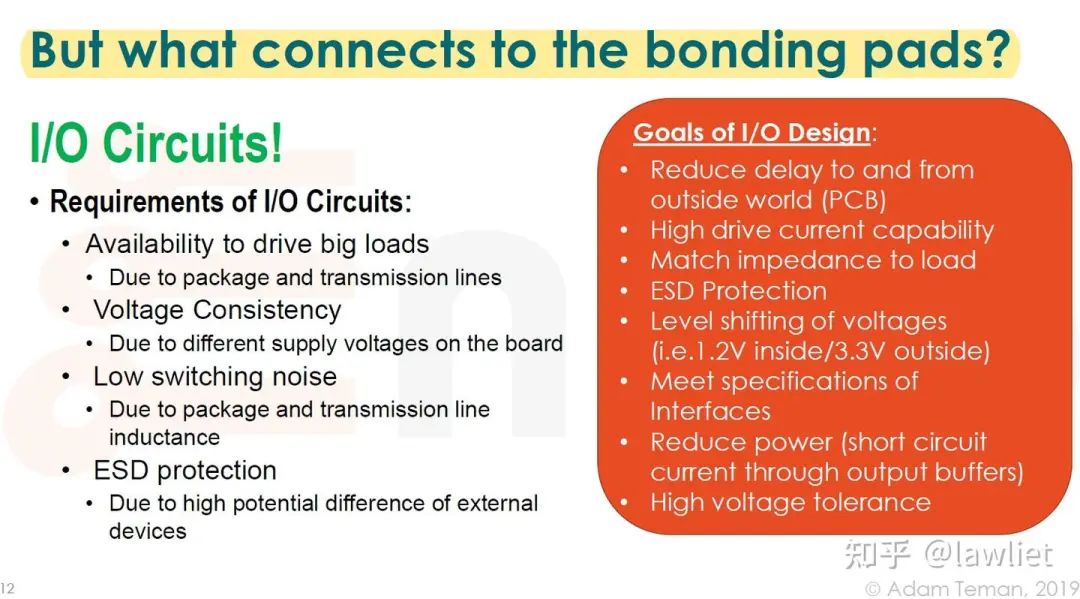

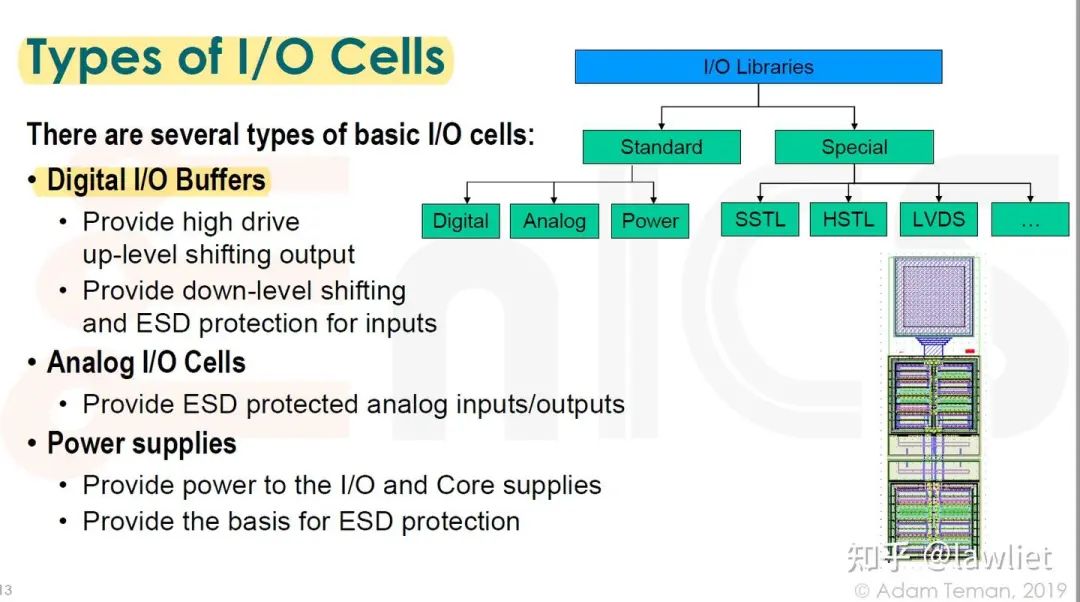

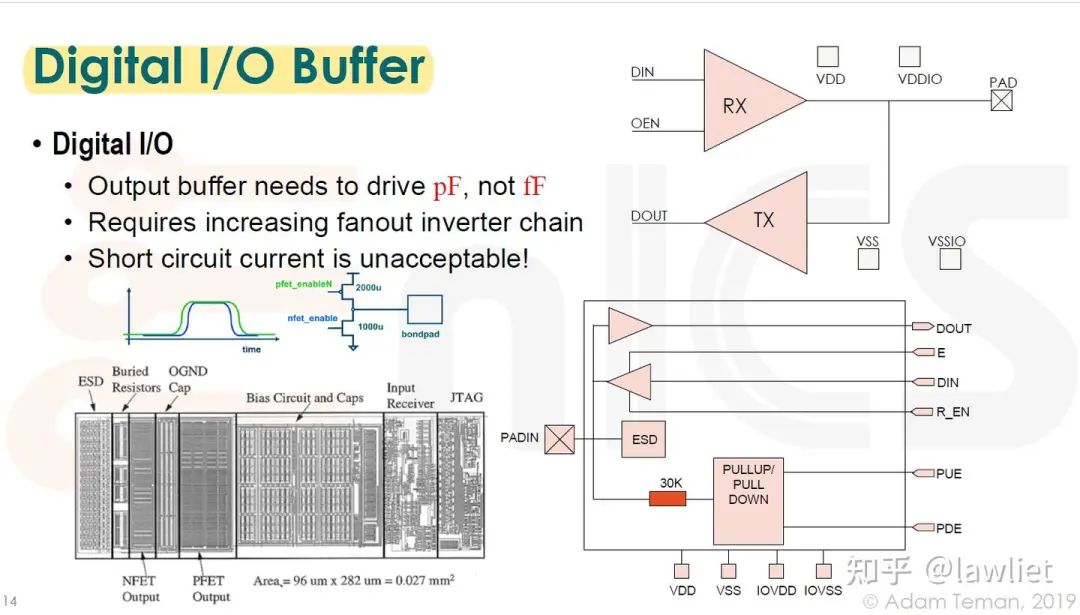

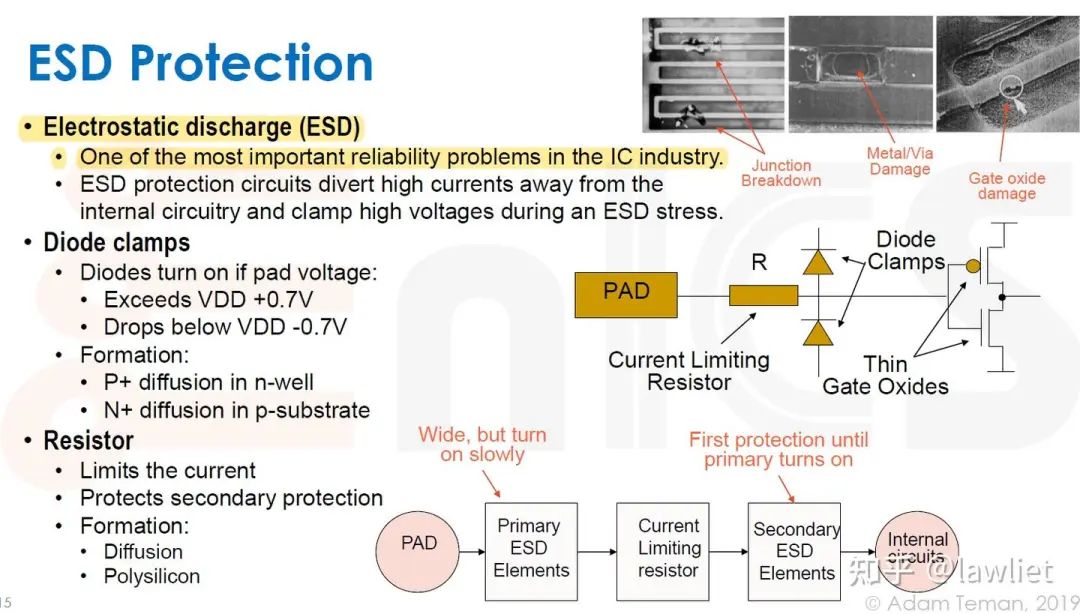

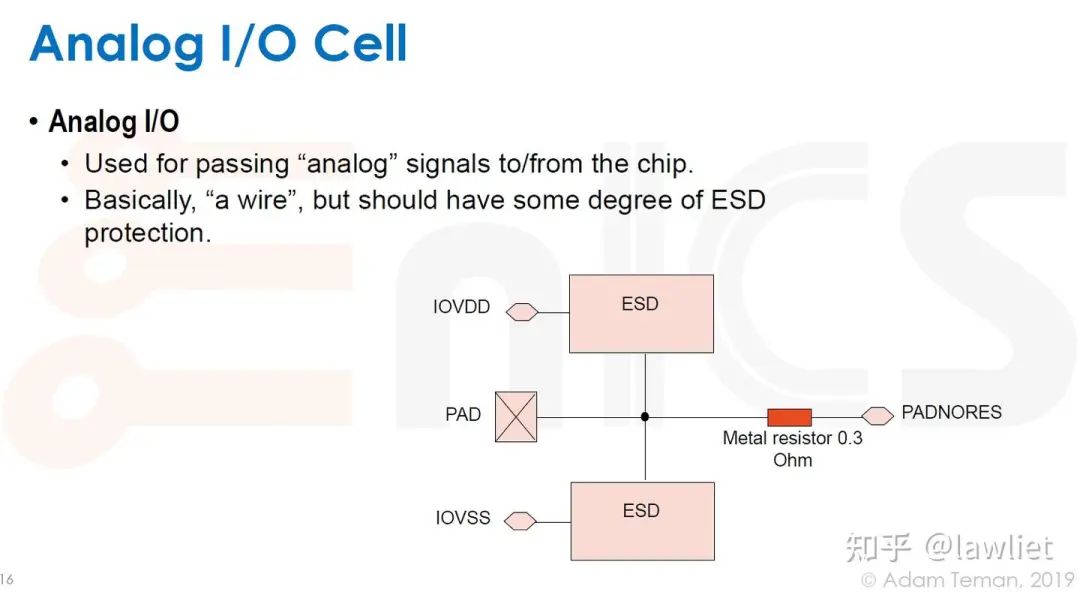

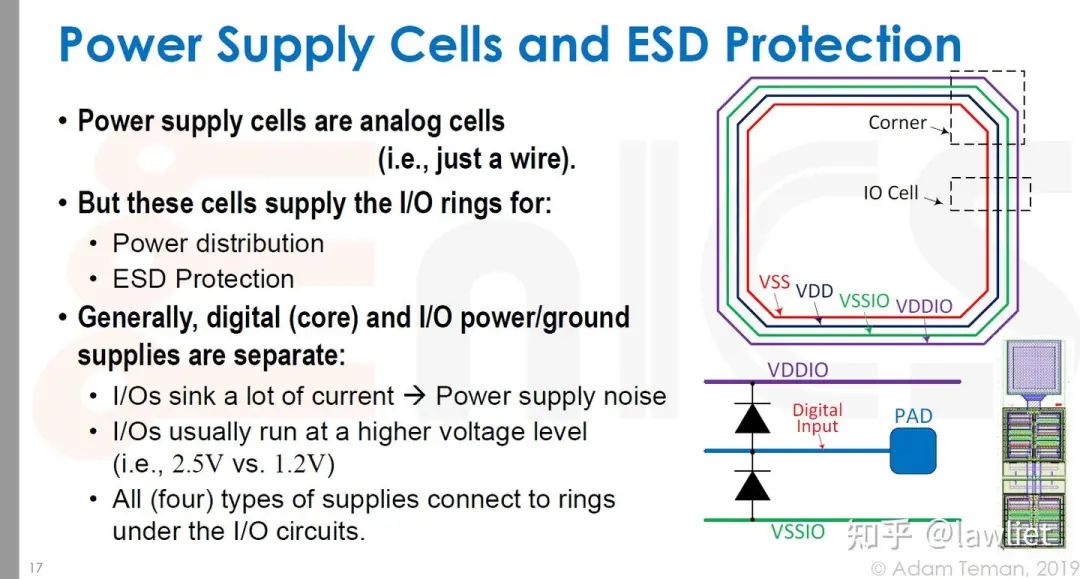

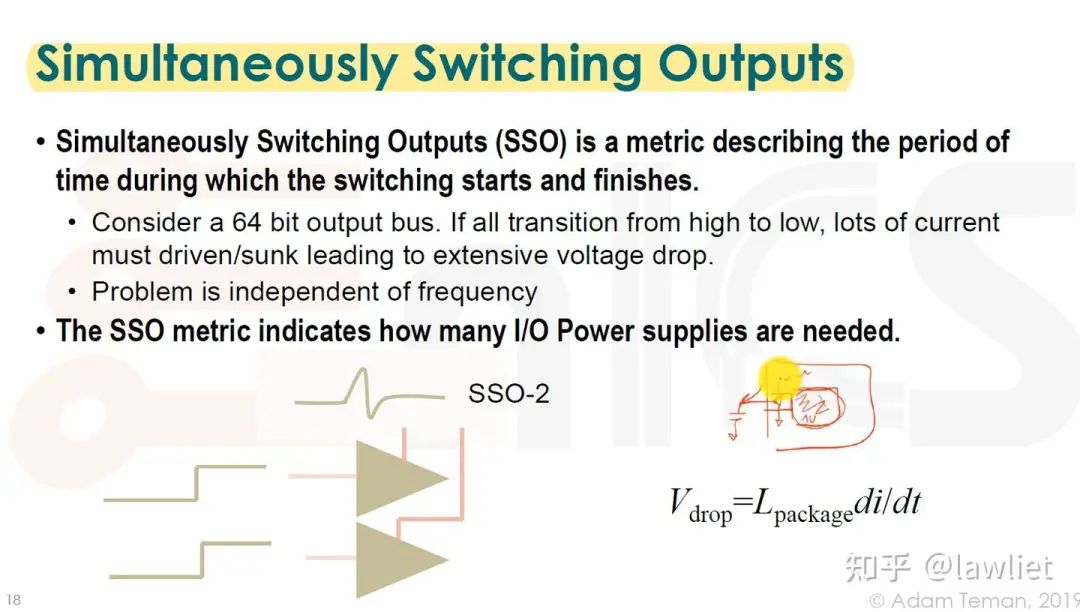

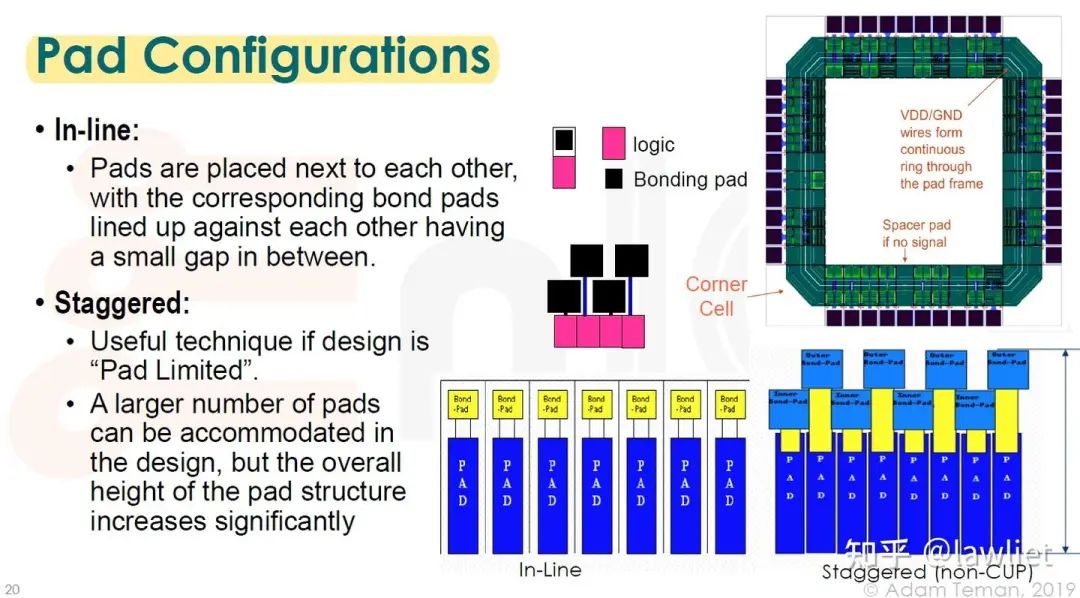

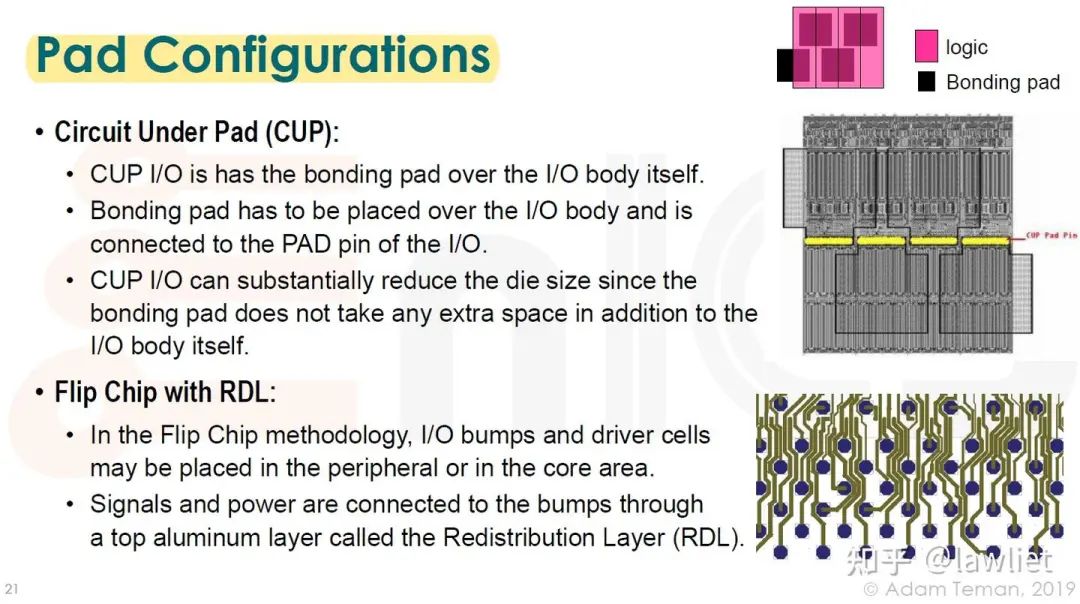

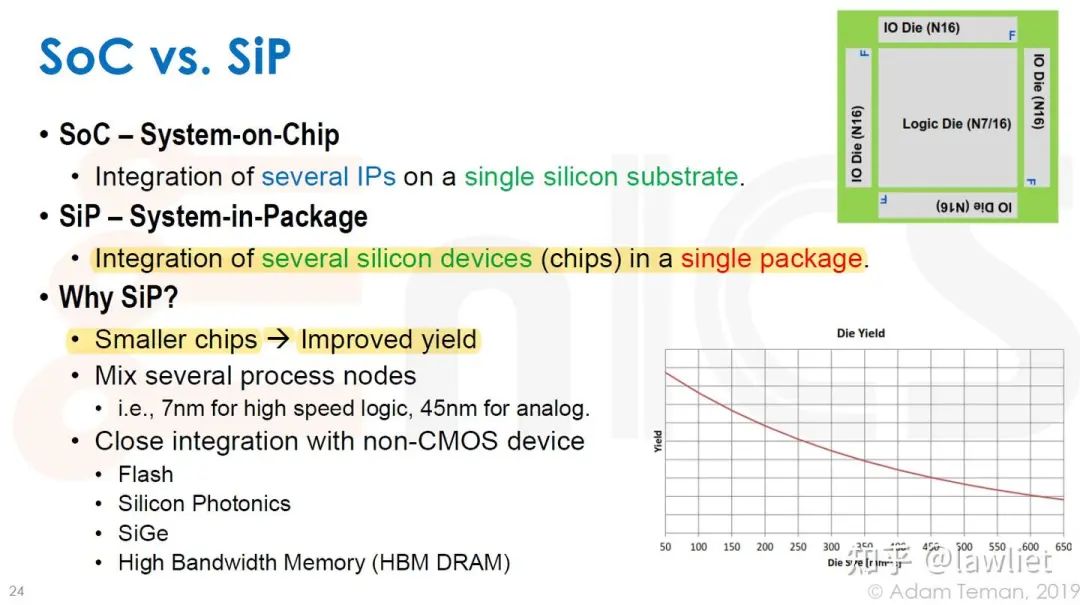

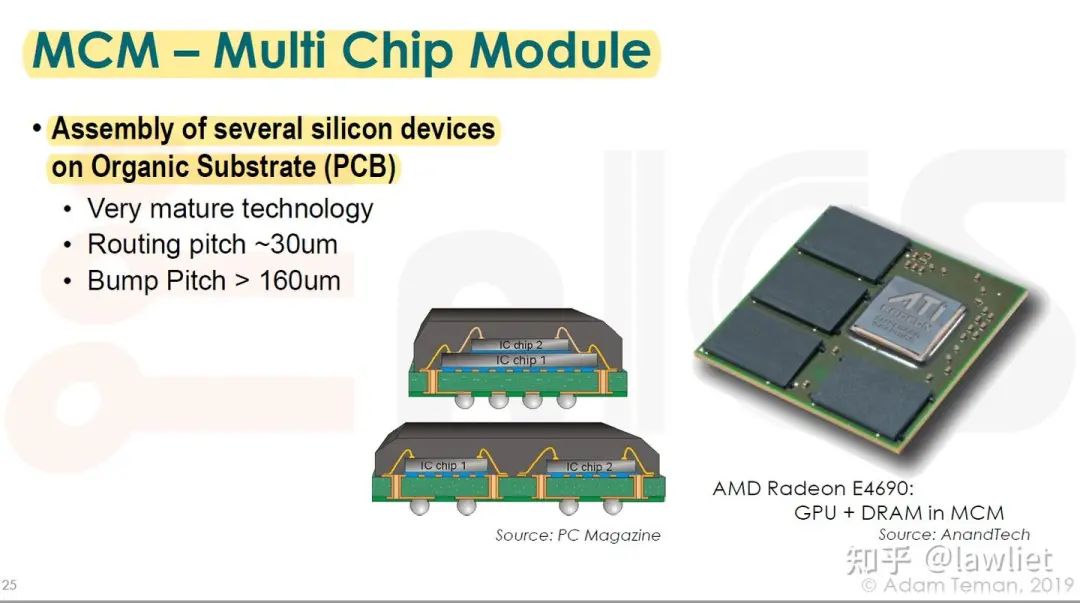

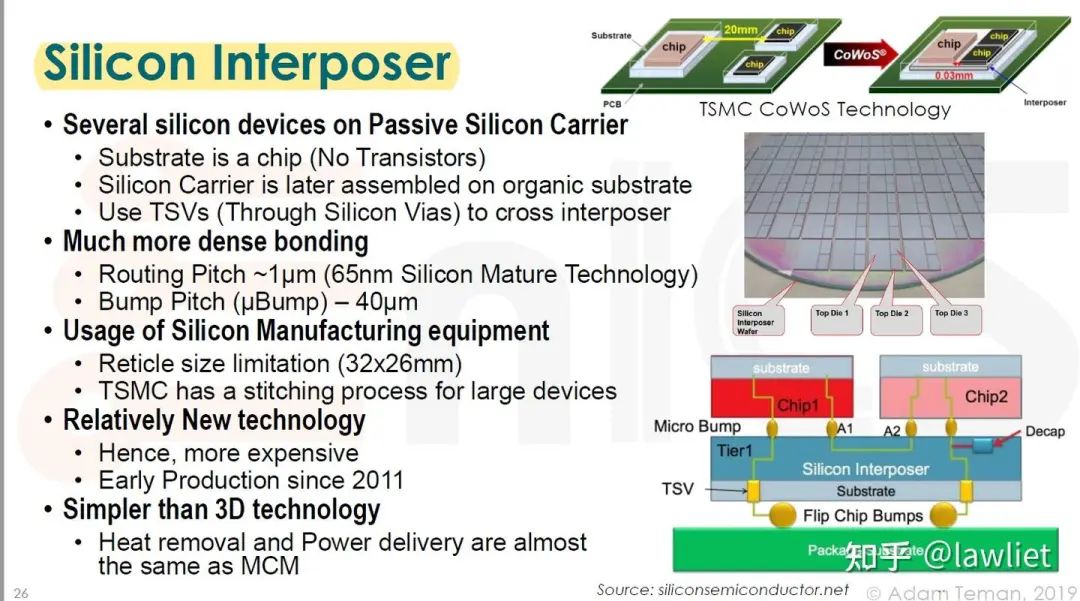

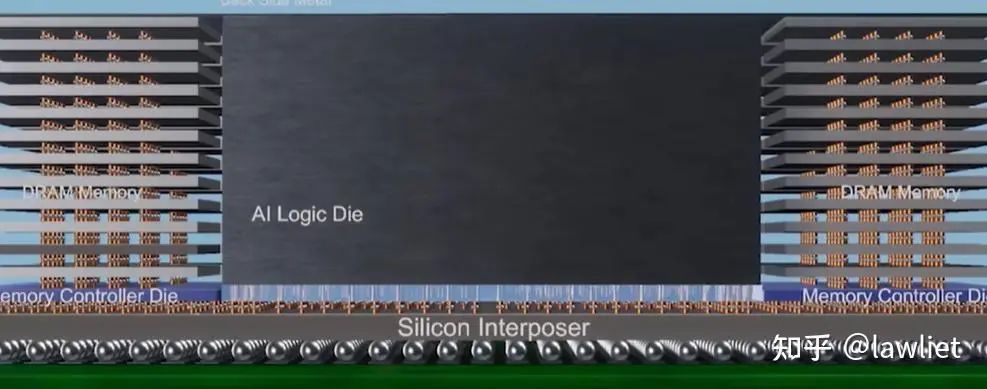

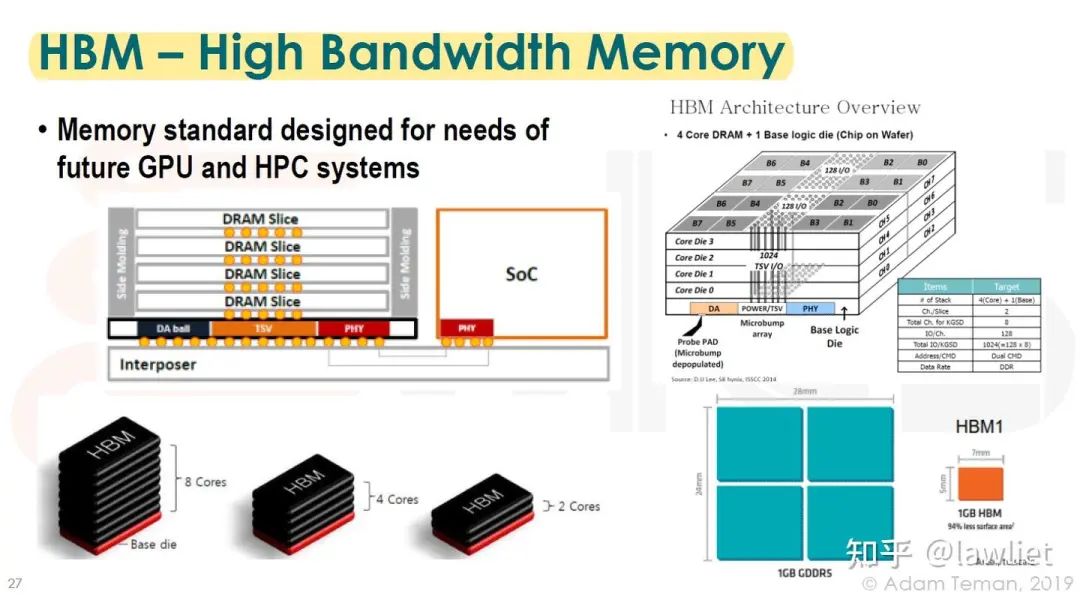

在前面的文章中,我们已经完成了布局布线了。接下来我们将讨论I/O和Pad Ring。以下是本篇文章的Outline。 1、A bit about Packaging首先让我们从封装开始讲起。 大家有没有思考过一个问题,一个芯片本身,它能直接拿来用吗?实际上肯定是不可以的,大家都见过芯片,芯片并不是光秃秃的放在那里。其一般是封装好以后才能够进行使用。这就引出了一个话题,我们是如何将信号传出芯片的呢? 实际上这个过程很复杂,芯片上设有I/O电路,通过绑定线接入封装,最终连接到电路板,完成整个过程以后我们得以将芯片和外部环境进行连接。 一旦离开芯片本身,我们就会碰到长导线,长导线意味着大量的延迟、电容和电感。这里的量级和芯片内部截然不同,要大得多得多。我们可以使用更粗的导线,从而降低电阻,并且外部空间相比芯片内部就没有那么拥挤了,我们可以灵活应用芯片外部的空间。 连接芯片和外部世界的Interface,我们称之为IC封装。我们看下面这个图的右下角部分,蓝色的那个代表芯片。所有的连接都通向基板上的一部分,通过bond wires进行连接。灰色的部分为摸具,确保所有元件稳固定位。  所以,到底什么是封装呢?听上去只是一个包装一样,但实际上非常重要。其有可能是整个产品中最昂贵的一部分。 我们看一下封装的一些属性。通过封装可以对芯片提供物理温度和电气保护。它采用物理连接的方式,将芯片和board连接在了一块,同时连接的也有电气信息。其保护芯片免受外部高压影响,同时还提供了热隔离。下图的右上角我们可以看到封装和芯片的一个电路连接示意图。 封装要求分为五个类别: Electrical:我们需要讨论芯片所有连接的电容、电阻、电感以及阻抗调谐问题; Interface:我们需要大量的IO引脚,用于连接芯片外部的各种各样的接口; Mechanical:我们还有机械方面的要求,即对于芯片本身以及其外部世界连接的焊点所采取的保护措施,同时这些保护措施要和PCB兼容; Thermal:热量如何从芯片排放出去; Cost:满足要求的情况下越低越好;(封装占成本的很大一部分)  我们看一下典型的芯片封装: DIP(Dual In-line Package):双排直插封装,适合在PCB上穿孔焊接,操作方便。但是其体积较大,引脚数有限,主要适用于一些中小规模的集成电路。以前学数字电路的时候教学芯片一般都用这个。随着电子技术的发展,高端芯片往往采用更先进的封装技术。 QFP(Quad Flat Package):四侧扁平式封装,QFP封装的芯片引脚之间距离很小,引脚很细。芯片面积与封装面积之间的比值较小。用这种形式式封装的芯片必须采用SMD(表面安装设备技术)将芯片与主板焊接起来。采用SMD安装的芯片不必在主板上打孔,一般在主板表面上有设计好的相应引脚的焊点。将芯片各引脚对准相应的焊点,即可实现与主板的焊接。用这种方法焊上去的芯片,如果不用专用工具是很难拆卸下来的。 PGA(Pin Grid Array):插针网格式封装,PGA封装在芯片的内外有多个方阵形的插针,每个方阵形插针沿芯片的四周间隔一定距离排列,安装时,将芯片插入专门的PGA插座(Socket),便于安装和拆卸;适用于需要高引脚数的应用。 BGA(Ball Grid Array):球栅阵列封装,BGA封装在芯片底部制作出球形凸点,以代替引脚,用于表面贴装。优点:提供了更高的I/O引脚数和更好的电热性能;适用于高密度、高性能的集成电路封装。 当然这里只是简单介绍一下,芯片封装是一个完整的产业,很大的topic,感兴趣的朋友可以搜索相关的内容。对于设计人员而言,简单了解,大概掌握不同封装的优缺点即可。  我们接着看IC和封装是怎么连接起来的。有两种典型的方式: Wire Bonding(引线键合技术):具体看这篇文章,爱在七夕时:半导体封装Wire Bonding 打线邦定(引线键合技术)的详解; Flip Chip(倒装芯片):如下图所示,将芯片翻转过来盖上去,加热基板,焊料凸点就会连接起来。(有点像BGA,但现在焊锡球就位于芯片本身上)。相比于传统的Wire Bonding只能连接到边缘而言,采用倒装芯片的方式可以将焊点置于芯片中央,并且连接进去。和金属层紧紧连接,显然这种方式获得的电气特性会更好更稳定。 ·  我们看下图,我们的芯片周围的黄色金属,那些就是PAD。这是我们后面将要讨论的IO。其通过Bonds连接到封装内部的相关连接点上。同时要注意以下要求: Bond Wires不能交叉; 要保持一定大小的最小间距,不能太小; 不能让角度太大,长度太长;  2、Input/Output Circuits所以怎么和Bonding Wire连接在一起呢?对于Wire Bonding和Flip Chip两种封装方式而言,是不一样的。以Wire Bonding为例,我们需要使用金属Pad。我们基于这个Pad,将芯片本身和封装的引脚通过Wire Bonding连接在一起。这里的Pad的面积通常比较大,要足够让线“着陆”。  这又引出一个话题,那就是怎么连接到金属PAD?那就是通过I/O电路!很多时候我们将I/O电路和金属PAD统称为I/O。对于I/O电路有以下要求: · 能够驱动大负载; · 确保电压的一致性; · 低开关噪声; · 静电放电保护; 基于这些要求,我们要设计相应的I/O电路。从逻辑上来说很简单,实际上我们设计的就是一种Buffer。  我们来看一下I/O单元的分类。这里我们只关注标准I/O Libraries。分别是数字部分、模拟部分和电源供应部分。  2.1、Digital I/O Buffer我们来看一看数字I/O Buffer。我们可以看到,其对外的接口为PAD。基于此可以作为输入也可以作为输出。如果作为输入的话,PAD连过来驱动DOUT,这是没有问题的。但如果作为输出的话,我们要考虑多驱的问题,为此我们使用一个输出使能信号,该信号使能的时候代表用PAD作为输出。由于驱动能力要求很高,我们需要非常非常非常大的反相器链来增加驱动能力。此外,我们看下图中那个反相器,我们一定不能让NMOS和PMOS同时导通,短路电流会非常大,这是不能接受的。  当我们考虑将缓冲器作为输入来使用的时候,必须要考虑到静电放电保护。其在整个芯片流程中非常重要,是很关键很关键的可靠性问题。如果不做相应的保护,静电的高电压作为输入,非常有可能烧毁芯片。 我们采用的方法称为二极管钳位。如果没有这个二极管,当高电压进来的时候,会同时击穿NMOS和PMOS,导致芯片烧毁。但如果有这个二极管,高电压进来的时候,会导通这个在正常情况下处于反向偏置的二极管,相当于把电流给引走了(KCL定律)。如果是正电压,导通上面那个二极管,否则导通下面这个二极管。无论哪种情况,都可以避免电流进入反相器。 同时我们一般会采用分级策略,有一个主ESD保护和一个次ESD保护。主ESD的二极管非常大,其偏置电压相应也很大,如果电压很大,它会hold住这个电压。但如果电压不大,就可以让次ESD应付就足够了。次ESD开启时间相比主ESD快得多,可以快速导通。  2.2、Analog I/O Cell我们接着看模拟I/O。其用于传输模拟信号,简单来说,是一根线。但是可以提供一定程度的ESD保护。具体的可以看下图,很简单。 2.3、Power Supply CellPower Supply Cell实际上也是模拟Cell。我们都知道电源电路实际上是模拟电路,这里也是一样的。对于这种模拟信号,我们不希望通过数字部分进行AD转换。我们需要的仅仅是一根导线。但这里的导线采用I/O ring的方式,具体可以看下图。通过这种环形的方式,我们只要将IO Pad放在下图IO Cell那个灰色框框类似的位置。就可以接入四种电压。通过和相应的电源轨道短接,便可以为整个芯片进行相应的供电。我们会有很多个这样的IO Pad,具体取决于芯片需要多少电流。  同时切换输出SSO,是一个指标,其反映了信号切换从开始到完成的时钟周期。我们假设有64-bit输出信号。如果某一个时刻这些信号全部从0变成1,这样就会有许多许多的电流要驱动或者吸收。这样就会引起电压降,进而影响电路的工作。这是一个和频率无关的问题。基于SSO指标,我们可以确定需要的IO电源数量。即应对这种极限的情况也要有足够的电流量。 有一点指的一提,如果VDD和VDD_IO的电压相同,我们仍然会将其划分为两个独立的电压域。为什么? 假设我们芯片内部有一个工作核心,其以1V的电压进行工作,由于其工作负载很大,因此其对噪声非常敏感。如果其和I/O也在一个电压域,那么其也要驱动外部负载,当特定的情况出现,比如64-bit输出信号全部从0变成1,其电流会突然变化,进而因此很大的电压降。电压下降会导致其对噪声更加无法承担。所以我们希望尽可能划分独立电压域,这样即使IO发生大规模Switch,仍然可以保证内部的工作核心不受噪声影响。  我们来看一下Power相关的 I/O design指导思想,具体的看下面的文字即可。  接下来看一下Pad Configuration。最典型的PAD是如之前见到一样,按照顺序规整的排列下来。但很显然,每一侧的长度直接决定了我们能够在芯片边缘上放置多少I/O Pad。 为了缓解这一问题,可以使用交错阵列的方式,错开排列。具体的可以看下图的右下角。  还有更加优化的方法,大家直接看图即可。  3、System in Package(SiP)接下来我们看一下什么是SiP。 SiP的思想和SoC很像,有关SoC可以看下面这个专栏(点击阅读原文)。SiP是一种封装技术,将多个芯片,即多个独立的硅器件,集成到一个单一的封装中。比如下图右上角,可以看到中间有一个芯片,周围还有别的芯片环绕。其还可以使用混合工艺,与非CMOS设备紧密结合等等。  最初的SiP解决方案为MCM即多芯片模块,这一技术至今仍然非常流行。其实际上就是将多个硅设备组装在一张有机基板上的过程。下图是两种不同的方式,一种方式是将两个芯片绑定在同一基板上,然后将他们一起封装。 另一种方式是将两个芯片叠放在彼此之上,并进行绑定,可以实现更短的互连。  更加新的方式是采用Silicon Interposer。这种方式我们将多个硅设备放置在一个无源硅载体上,其本身就是一个芯片。内部拥有多种不同的布线轨道,使我们能够实现芯片间的互连。 其采用了TSV技术,帮助我们在不同芯片和基板之间建立连接。其相比MCM可以提供更加密集的连接方式。  我们看一个典型应用,HBM。现在的GPU和高性能系统等,对带宽的要求非常大,带宽的速度跟不上运算的速度,这就是所谓的存储墙限制。 HBM技术将多个DRAM进行堆叠,采用硅通孔和微凸块将裸片进行连接,如下图所示。具体可以看看这个视频(点击阅读原文)。   |