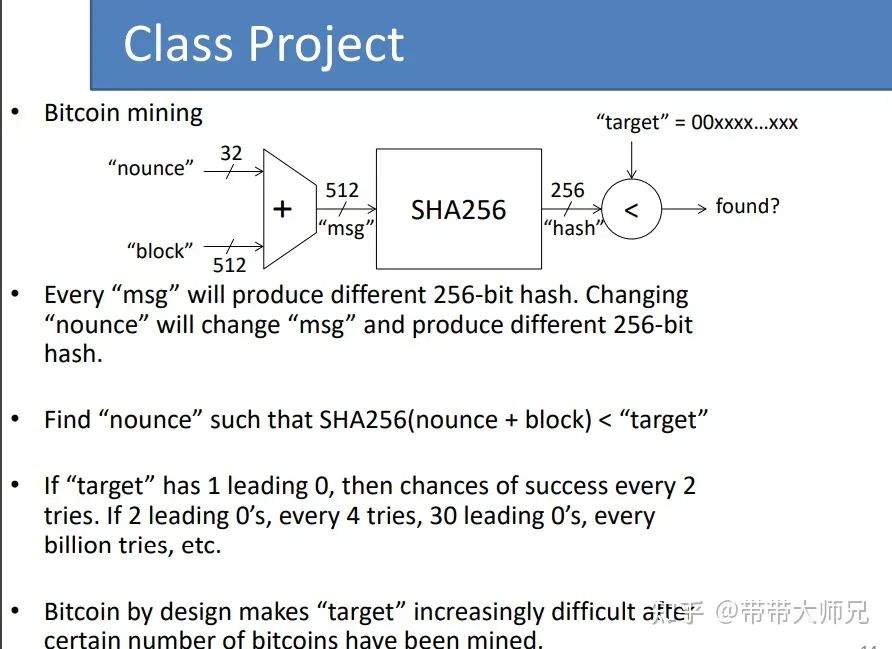

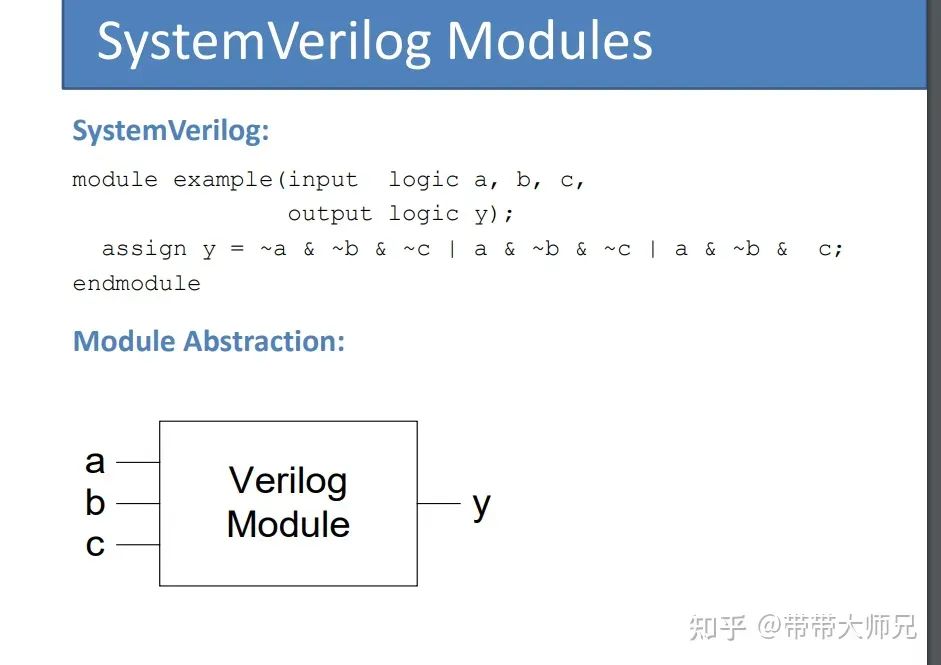

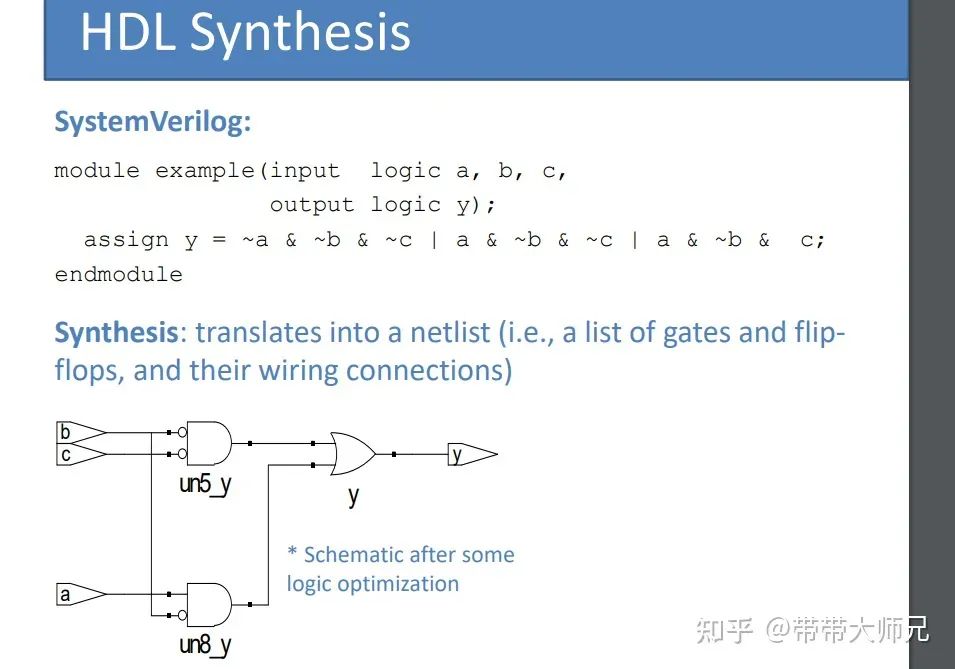

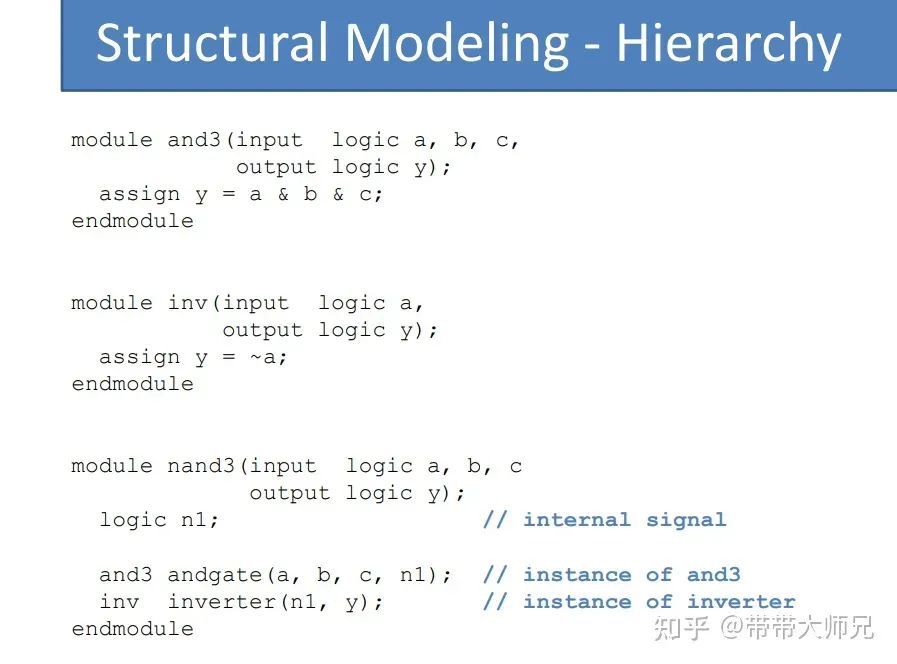

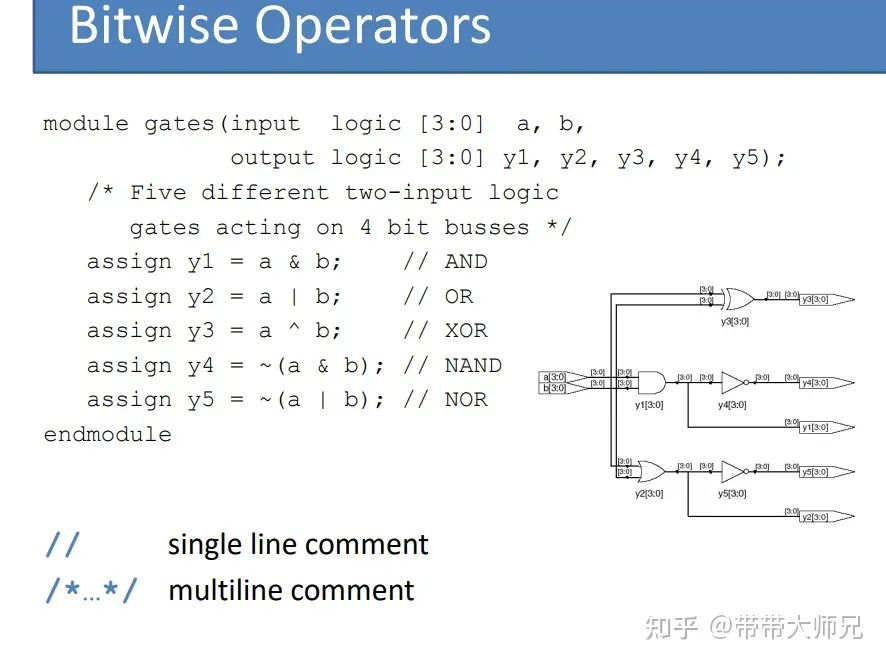

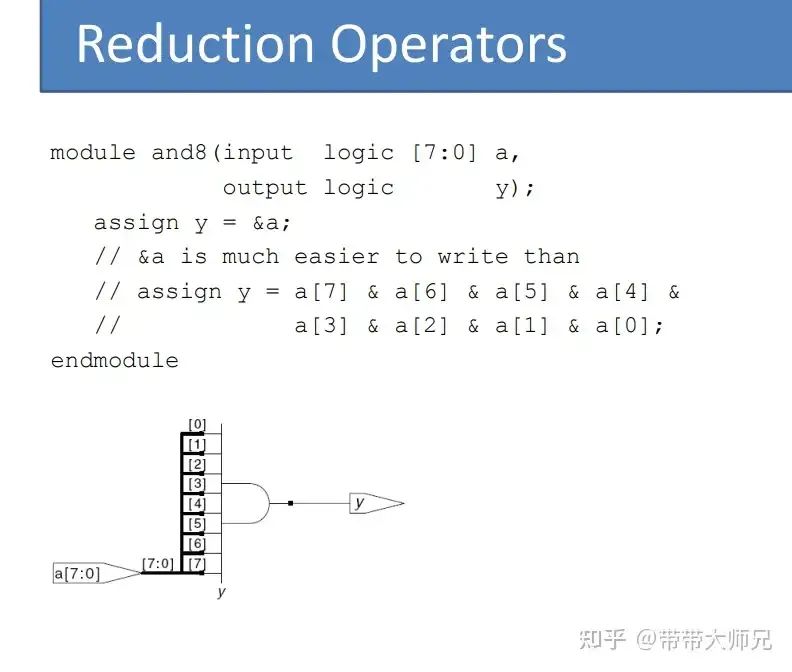

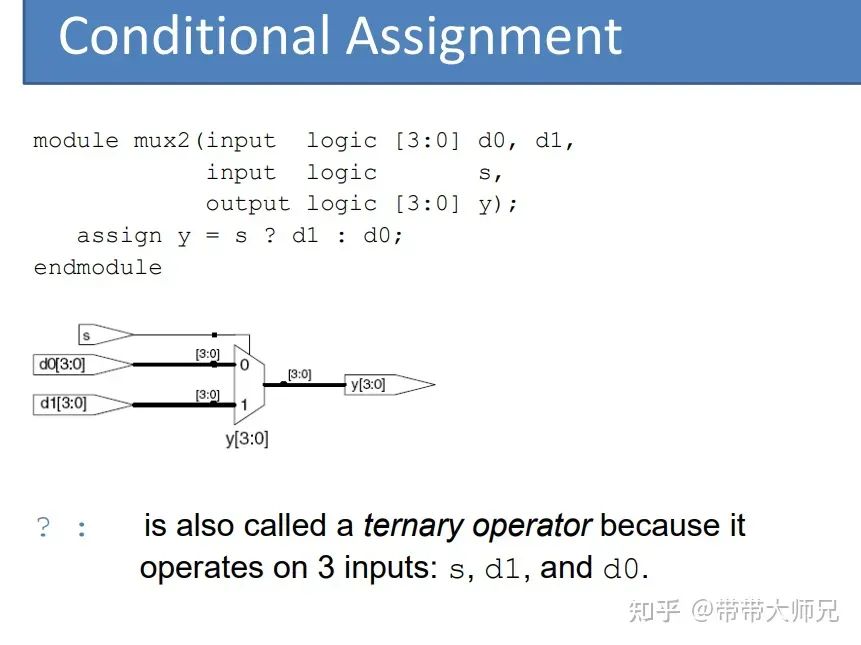

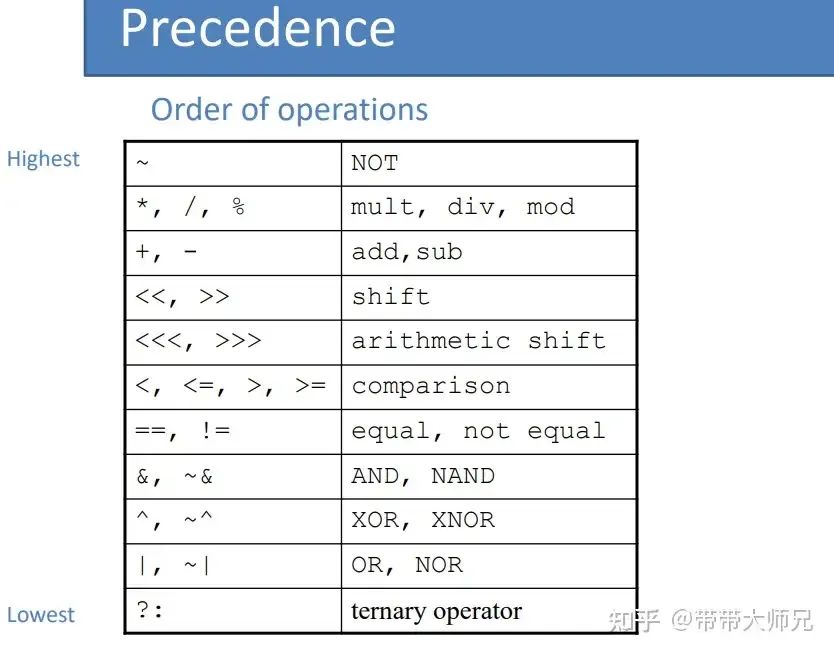

偶然发现了一门不错的课程,UCSD的ECE111。这门课最后开设是在2019的Winter学期,距今也没有太长时间。课程讲授的内容非常适合EE/CS专业的学生入门芯片设计。该课程主要介绍了基于SV的数字芯片设计,这门课还有几个Project作业,主要围绕Bitcoin相关展开。 这门课的课程目标是学会基于Verilog的数字芯片设计。实际上这门课主要使用的是SystemVerilog(后面简称SV),SV可以看作是Verilog的超集(实际上用作设计的话,SV相较于Verilog增加的东西并不算多)。SV文件以.sv结尾,区别于Verilog的.v结尾。  然后大致花了四五页的时间介绍了为什么要学习SV(目前主流的数字芯片设计都是基于Verilog或SV,数字芯片工程师吃饭必备的东西)。  然后介绍了一下本节课最终要实现的Project。个人觉得这份Project难度低于很多大作业布置的四/五级流水线CPU设计,对新手比较友好,在后续文章中我将讲解如何一步一步设计该Project。  接下来介绍了一下使用的开发工具,该课程官方使用的是Questasim。本人在后续将会使用vcs和Verdi工具,还会附带着讲解一些常用的脚本如bash/Makefile使用(大部分公司都是这套开发工具)。  然后介绍了一下推荐书籍,这里推荐Harris老师的Digitial Design and Computer Architecture,神书。 现在让我们开始进入干货!!!  理解SV语言既是一种“综合”语言又是一种“仿真”语言是非常重要的。所谓的综合即从代码映射到真实的逻辑电路,能够综合的语法只占SV的一小部分,这也是我们要重点掌握的。除此之外SV主要用于验证,这一部分涉及的语法较多,不在本课程讨论的重点。对于没学过Verilog或SV的同学来说,刚刚学习该语言的时候,可能会觉得很像C语言,但大家要理解,Verilog/SV是一门硬件描述语言(暂时不考虑验证),也就是对实际的电路进行描述。与传统的软件语言的设计思维完全不同。所以大家在学习这门课的时候,要有意识的“think in hardware"。接下来的文章我也会强调这点。  module是Verilog/SV中最基本的单元,也就是俗称的模块。模块可大可小,小到一个门电路,大到一个SoC,都可以是一个Module。需要注意的是,在绝大多数情况下,一个.v/sv文件通常只包含一个Module。上图的Module描述了一个逻辑电路。输入为a,b,c三根线,输出为y这根线。上述的逻辑运算定义了y和a,b,c之间的关系。  经过综合,该代码会变成如图所示的门电路(大家在做设计的时候,写RTL代码实际上就是去描述这样的逻辑电路)。  上图为一些语法相关的注意事项,比如该语言是区分大小写的、不能以数字开头、空白会被忽略以及如何写注释。  然后讲解了一下结构层次的概念。可以看到,在nand3这个模块中,调用了and3和inv这两个模块(也就是一个模块中可以包含子模块),这一点很好理解(一个大模块由若干个小模块组成)。需要注意的是,在nand3这个模块中需要定义n1这个内部变量,用来连接and3和inv两个模块。读者朋友有兴趣可以动手画一下,实际上就是一个与逻辑跟了一个反相器。  然后讲解了一下按位操作符。单个的& | ^等信号代表各个比特之间互相运算。比如a&b就是a[0]与b[0],a[1]与b[1]相与。输出的比特与输入的比特一致(在使用该运算符,应该保证两个变量之间比特长度相等,否则可能会有意想不到的错误)。该逻辑综合的电路如图所示,非常直观。  然后讲解了一下规约运算符,该运算符等价于各个比特之间做运算,直接看图即可。  然后讲解了一下三目条件运算符,三目运算符和C语言中的三目运算符基本类似。满足则选择前者。综合成实际电路的话是一个MUX逻辑(选择器)。  最后讲解了一下运算优先级,说实话,本人也不记得这么多。建议大家多用括号,来确保逻辑与自己的预期相一致。 上面的内容就是第一节课的Slides。大家学习的时候最好手上备一本数电书,再次推荐Harris老师的《数字设计和计算机体系结构》。 |