|

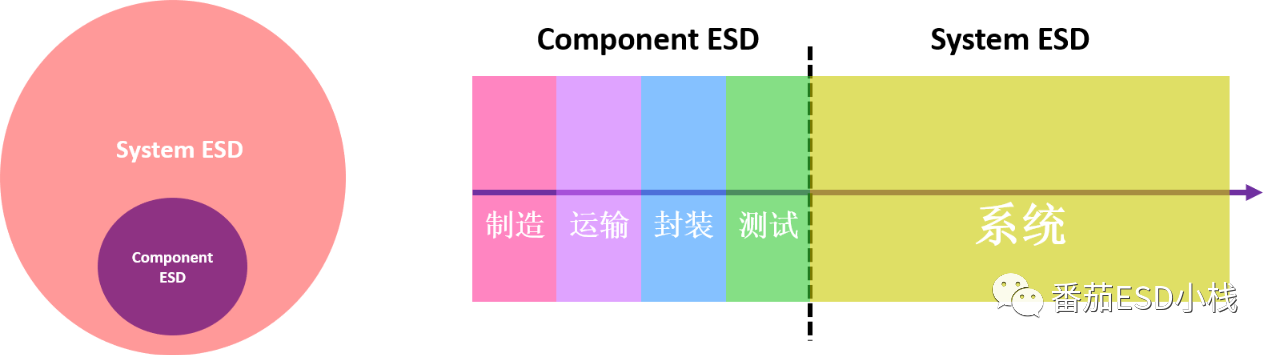

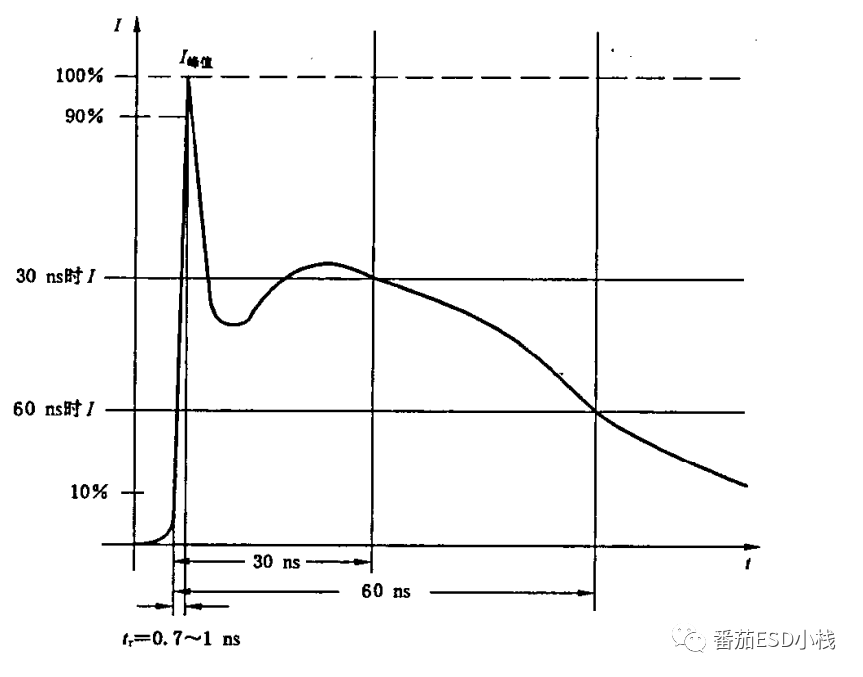

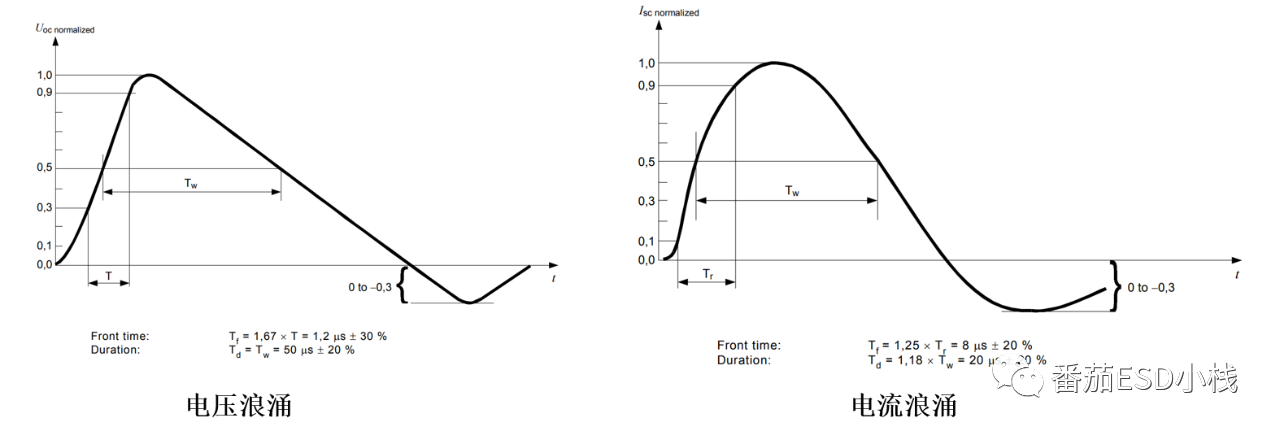

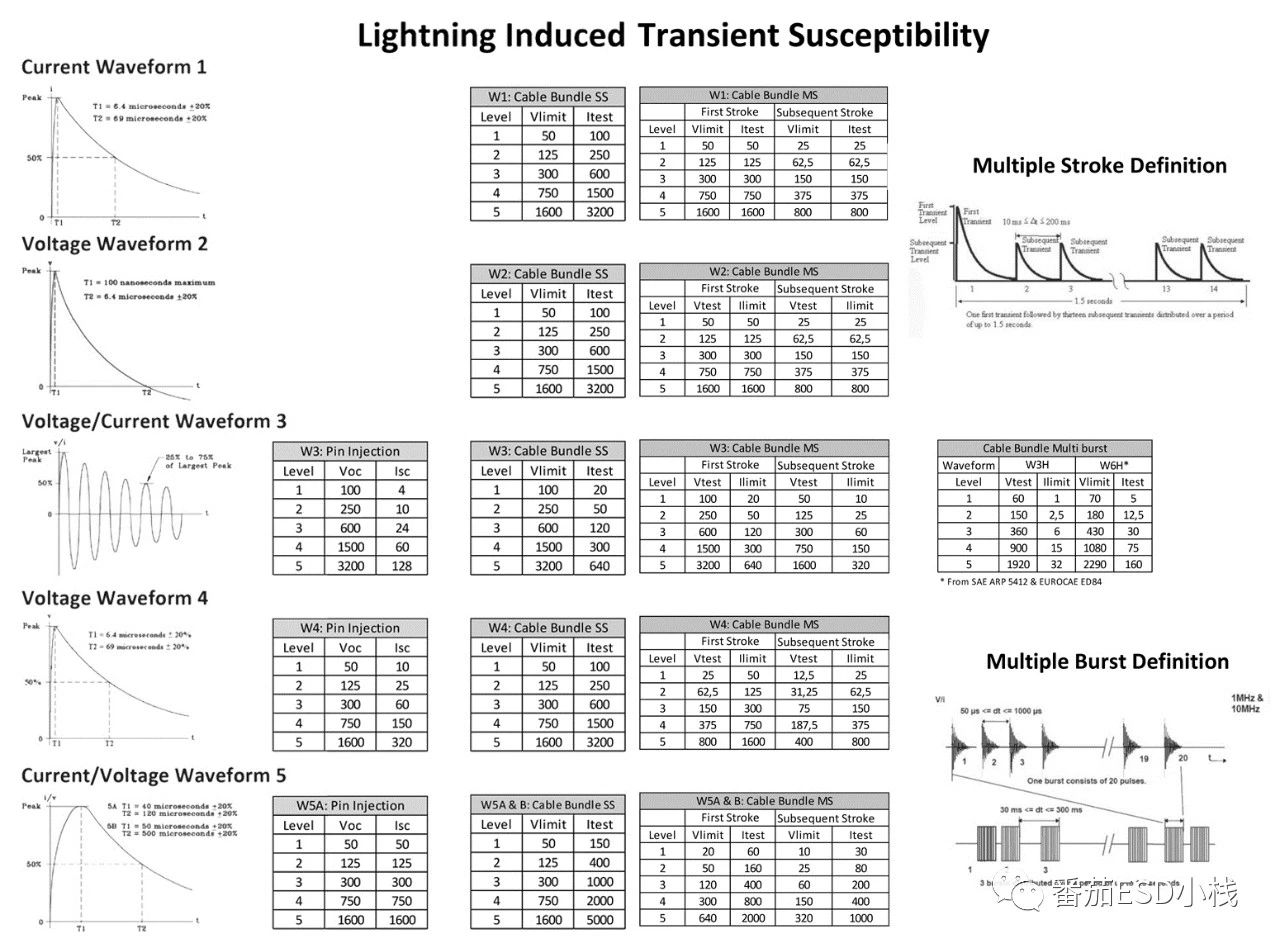

下了产线的芯片最终还是要与其他电路元件组成系统才能发挥其作用,所以当设计师进行全片ESD防护设计时除了要考虑芯片自身的ESD防护(Component ESD protection)外,还需要兼顾整个系统的ESD防护设计(System ESD protection)。 System ESD 是指芯片在PCB板上与其他电路元件构成一个系统后在使用过程中/间歇所承受的静电冲击,因为系统所面临的工作情况更加复杂,所以System ESD也更加繁杂。而Component ESD是指芯片在制造、封装、运输、测试过程中所承受的ESD冲击,其只是针对芯片自身的ESD事件。如图一所示,从芯片的使用周期来看,芯片大部分时间还是处在电路系统当中,其遭遇System ESD的机率远高于Component ESD,System ESD的破坏性也高于Component ESD,但是System ESD的设计手段也远比Component ESD丰富。为了保证系统的ESD鲁棒性,又不降低芯片自身面对Component ESD的防护能力,就需要对On-Chip ESD和Off-Chip ESD进行Co-Design协同设计。(更多关于System ESD的技术细节笔者日后会徐徐道来,这一期主要是讲片内与片外的Co-Design)  图一.System ESD与Component ESD对比示意图。 一.System ESD 简述。 目前常见的System ESD有五种: 1. 接触放电/空气放电 (IEC 61000-4-2),这两种放电波形参数相差不大,试验设备差距主要在放电枪头。接触放电:试验发生器的电极保持与受试设备的接触并由发生器内的放电开关激励放电的一种试验方法。空气放电:将试验发生器的充电电极靠近设备并由火花对受试设备激励放电的一种试验方法。该ESD波形中有两个峰值,第一个峰值是由导体外围区域放电造成,峰值高,持续时间短。第二个峰值是由剩余的累积电荷造成,峰值低,持续时间长,衰减慢,波形的主要能量集中在第二个峰内。  图二.IEC 61000-4-2 静电波形示意图。 2. HMM (Human Metal Model),为了研究System ESD对芯片的影响,提出了HMM模型。其波形参数与试验设备与IEC 61000-4-2相近。 3. 浪涌 (IEC 61000-4-5) ,浪涌是指信号或者电源在进行切换时可能会产生的一种电学现象,其分为电压浪涌和电流浪涌,浪涌的持续时间远高于其余静电事件,在设计时可以近似于持续一段时间的直流电压/电流。  图三.IEC 61000-4-5 电压/电流浪涌波形示意图。 4. 热插拔 热插拔所造成的System ESD比较复杂,既可能造成静电,也可能造成浪涌。 5. 雷击 (DO160G),标准中根据不同的场景划分了波形1,波形2,波形3,波形4,波形5A和波形5B等多种情况。  图四.DO160G 雷击波形示意图。 二. Co-Design 概念简介。 因为整个系统存在大量元器件,所以面对System ESD时On-Chip ESD防护器件与Off-Chip ESD防护器件之间会有相互耦合,这种作用既有可能是积极的,也有可能是消极的,如图五所示。  图五. On-Chip ESD与Off-Chip ESD防护器件之间相互作用示意图。 2.1. 冒险与竞争关系: On-Chip ESD与Off-Chip ESD之间发生冒险与竞争。当System ESD发生时,On-Chip ESD会从Off-Chip ESD“掠夺”走ESD电流,System ESD经过芯片内部实现泄放,造成芯片损坏。如图六所示,当HMM等级到一定程度之后,流经TVS的电流骤然降低,On-Chip SCR ESD Device的电流增大,HMM静电流基本由芯片内部的SCR Device泄放。  图六. On-Chip ESD与Off-Chip ESD冒险与竞争示意图。 2.2. 协作与分流关系: On-Chip ESD与Off-Chip ESD之间发生协作与分流,当System ESD发生时,On-Chip ESD会协助Off-Chip ESD泄放ESD电流,可以提高泄放效率,降低On-Board TVS数量,这对提高信号完整性,降低PCB面积大有裨益。  图七. On-Chip ESD与Off-Chip ESD协作与分流示意图。 2.3. 相互独立: On-Chip ESD与Off-Chip ESD之间相互独立,当System ESD发生时,静电流只通过Off-Chip ESD进行泄放,On-Chip ESD维持在关闭状态,既不竞争也不协助。 由此可以看出On-Chip ESD与Off-Chip ESD之间的关系比较复杂,On-Chip ESD既有可能提高System ESD防护能力,又有可能从而突破口,降低整个系统的ESD防护等级。所以Co-Design的设计思路就是对On-Chip ESD与Off-Chip ESD实行统筹规划,统一设计,根据彼此的工作特性与I-V曲线,在 Component ESD与System ESD之间做出平衡,根据系统使用场景,建立On-Chip ESD与Off-Chip ESD的Design Window,依此做出最优的设计,不能厚此薄彼,要以整个系统的防护等级为目标进行设计,避免出现防护短板。 三.Co-Design 设计策略。 根据不同的需求与场景On-Chip ESD与Off-Chip ESD的Co-Design有不同的设计策略。 针对空气放电、接触放电、HMM这三种System ESD,尽可能的让On-Chip ESD与Off-Chip ESD进行协作与分流,因为这三种System ESD的持续时间与HBM相近,虽然总能量上高于HBM并且存在高峰值脉冲,但是随着波形的衰减,静电脉冲后半部分的能量与电流峰值会降低到On-Chip ESD承受范围内,On-Chip ESD能协助泄放部分的System ESD脉冲。 当面对雷击与浪涌冲击时,最好的策略是让On-Chip ESD与Off-Chip ESD之间相互独立,因为这类脉冲持续时间长,能量大,一旦On-Chip ESD介入泄放,芯片很难承受这类高能脉冲,失效风险很高。所以进行这两种防护设计时,还需要在Off-Chip ESD与芯片间设计限流器件消耗残余功率。在所有的System ESD中雷击的瞬态能量是最高的,且还伴随着热电聚集与电磁效应,所以芯片/系统的防雷击设计是极其繁琐与昂贵的。 文章到这里就会得出两个结论: 1. Off-Chip ESD与On-Chip ESD是息息相关的,Off-Chip ESD也因场景与On-Chip ESD有其Design Window。 2. 因为竞争与冒险的存在,所以On-Chip ESD的防护等级并不是越高越好,需要兼顾Off-Chip ESD的设计。 这一期就先开个头,笔者下一期讲解Off Chip的Design Window和设计实例。 |