|

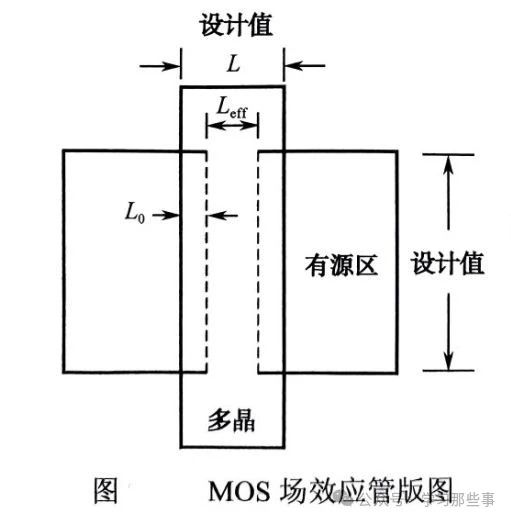

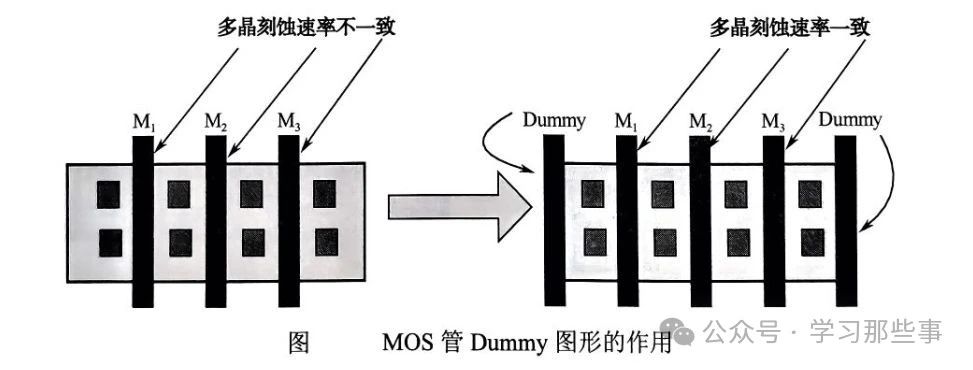

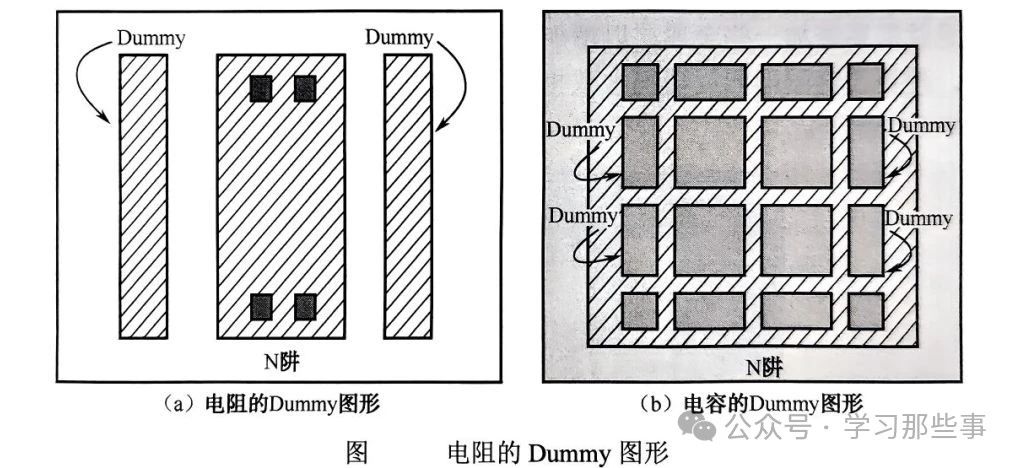

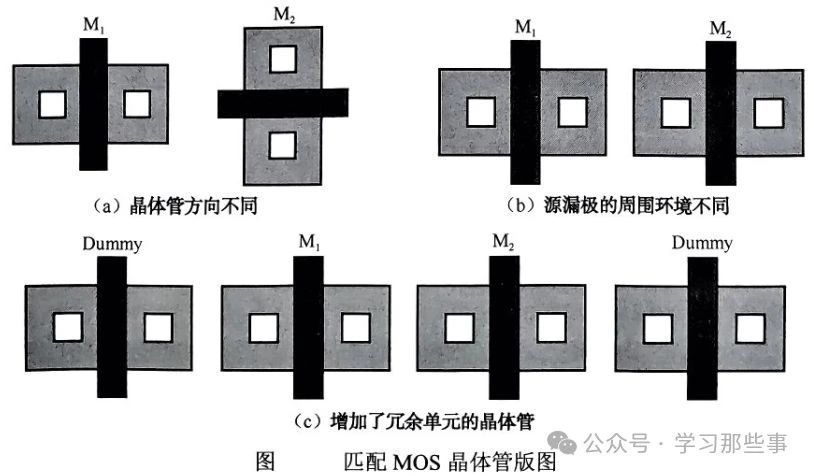

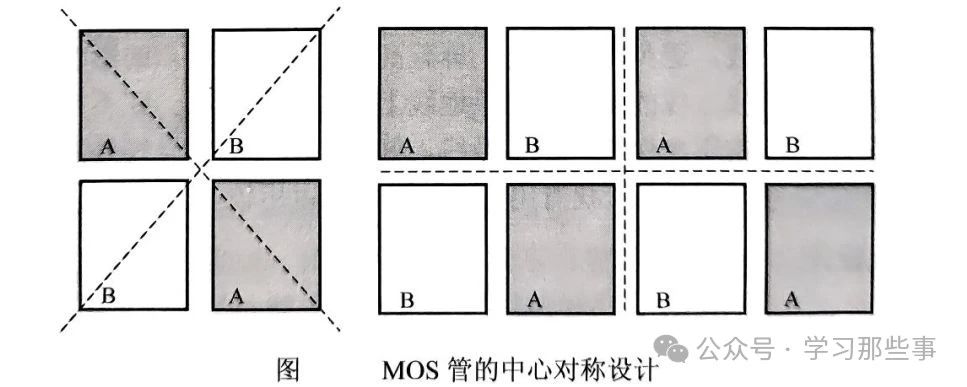

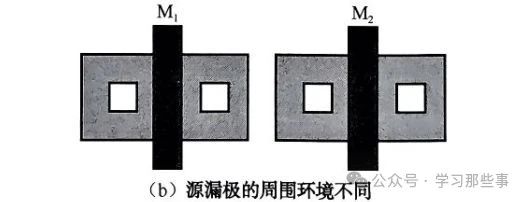

可靠性测试结构设计 层次化版图设计通过模块化分解和系统级优化,显著提升了设计效率、布局优化和失配控制。然而,工艺偏差和复杂设计仍是挑战。结合Dummy Layer技术、工艺参数控制、先进设计工具及模块化方法,可有效应对挑战,推动集成电路性能与可靠性的持续提升。本文分述如下: . 器件制造中的影响因素 .版图设计技术与匹配原则及其应用 1.器件制造中的影响因素 在MOS场效应管的制造过程中,设计尺寸与最终硅片上的实际尺寸存在差异,主要因素包括: 一、有效尺寸 1.有效沟道长度(Leff) 设计值L:多晶硅线宽的设计值。 实际值Leff:由于离子注入、掺杂、退火等工序中的横向扩散,实际电学沟道长度减小,即 Leff=L−ΔL,其中 ΔL 为扩散引起的长度减小量。  2.有效沟道宽度(Weff) 设计值W:有源区的边长设计值。 实际值Weff:由于场氧生长引起的有源区侵蚀,实际宽度减小,即 Weff=W−ΔW,其中 ΔW 为工艺引起的宽度减小量。 3.电气分析依据 宽长比:使用有效值之比 Leff/Weff 进行电路性能分析。 二、匹配设计与失配分析 匹配设计是模拟集成电路精度的关键,失配分为随机失配和系统失配: 1.随机失配: 原因:元器件尺寸、掺杂浓度、氧化层厚度的微观波动。 减小方法:电容,失配与面积平方根成反比,容量加倍可减小失配约30%;电阻,失配与宽度成反比,阻值加倍可减小失配50%;MOS管,阈值电压和跨导的失配与晶体管面积平方根成反比。 2.系统失配: 原因:工艺偏差、接触孔电阻、扩散区相互影响、机械压力和温度梯度。 实例分析:多晶硅电阻,宽度偏差0.1μm导致阻值比失配2.4%;双层多晶电容,刻蚀偏差0.16μm导致电容面积失配1.1%。 三、实际应用中的最佳实践 1.MOS管的Dummy技术 在MOS管设计中,Dummy技术主要用于提高器件的可靠性和一致性。  Dummy Poly的作用 避免栅长变化:在MOS管两侧增加Dummy Poly,防止栅极长度因工艺偏差而受到影响。 保护环设计:NMOS管,先加P型保护环连接到地,再加N型保护环连接到电源;PMOS管,先加N型保护环连接到电源,再加P型保护环连接到地。 拆分原则:拆分MOS管时,应保证偶数根,Source端与四周保护环就近连接。 实例分析 保护环连接:保护环的设计有助于减小噪声和工艺偏差对MOS管性能的影响。 Dummy Poly布局:通过合理布局Dummy Poly,可以平衡MOS管周围的工艺条件,提高器件的一致性。 2.电阻和电容的Dummy技术 电阻和电容的Dummy技术主要用于减小噪声和工艺偏差的影响。 电阻的Dummy技术:N阱使用,在多晶或扩散区电阻下面增加N阱,连接高电位与衬底反偏,以减轻噪声对电阻的影响;金属覆盖,在N阱电阻上面覆盖金属并连接高电位,以降低光照使电阻阻值下降的影响。  电容的Dummy技术:N阱阻挡,用N阱阻挡来自衬底的噪声,N阱接高电位,衬底反偏;布局优化,在电容周围增加Dummy电容,保证电容阵列的一致性。 2版图设计技术与匹配原则及其应用 一、版图设计技术 版图设计技术旨在减小系统失配,提高元器件的匹配性能 1.单元元器件复制技术 原理:匹配的两个元器件由某一个元器件单元的多个复制版本串联或并联构成。 优势:降低工艺偏差和欧姆接触电阻不匹配的影响。 2.冗余单元增加 原理:在元器件周围增加冗余单元,保证周围环境的一致性。  实例:如上图(c)通过增加冗余单元减小了晶体管的不匹配。 3.元器件距离控制 原理:使匹配元器件之间的距离尽量接近,减小扩散区之间的相互影响。 优势:提高元器件的匹配性能。 4.公用重心设计法 原理:使匹配元器件的“重心”重合,减小线性梯度的影响。  实例:上图采用重心重合的MOS管设计。 5.元器件隔离 原理:匹配元器件与其他元器件保持一定距离,减小扩散区之间的相互影响。 优势:提高元器件的匹配精度。 二、 匹配原则 匹配原则旨在提高元器件的匹配性能: 1.靠近放置 原理:将匹配的器件靠近放置,以减小工艺偏差的影响。 优势:提高元器件的匹配精度。 2.方向一致 原理:保持器件的方向一致,以提高匹配性能。  实例:图(b)中晶体管方向一致但周围环境不同,仍存在一定不匹配。 3.对称结构 原理:采用对称结构,减小管子的失配。 优势:提高电路的性能和可靠性。 4.布线最小化 原理:减少寄生电容,提高电路性能。 优势:减小噪声对关键信号的影响。 三、应用场景与最佳实践 1.应用场景 改善匹配性:通过添加Dummy图案,使芯片的各个区域在工艺过程中受到更加均匀的处理。 防止刻蚀过度或不足:Dummy图案作为刻蚀阻挡层,帮助控制刻蚀的深度和范围。 降低寄生电容和电感:通过合理设计Dummy图案,降低寄生电容和电感。 提高芯片的可靠性:Dummy图案帮助缓解应力,提高芯片的可靠性。 2.最佳实践 分析DRC报告:根据DRC报告确定需要添加Dummy的区域。 选择合适的工具:使用Calibre等EDA工具添加Dummy。 检查和优化:插入Dummy后,再次运行DRC检查,确保新的版图满足所有的设计规则。 LVS验证:完成Dummy插入的版图需要再次进行LVS验证。 |