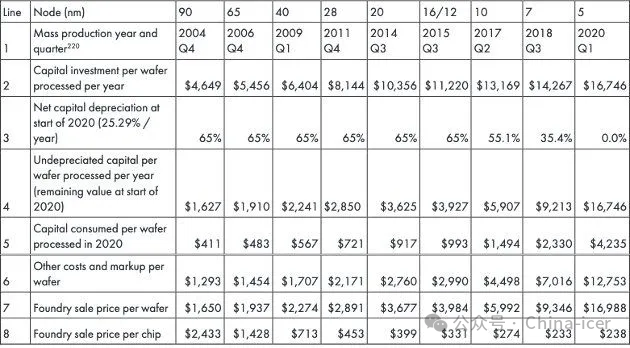

设计公司在NT.O之前都很谨慎, 为何流片都很谨慎?有哪些可以已知风险可以规避的呢?笔者用自己的经验给大家分析, 希望助力国内芯片产业的整体提升。T.O之所以极为谨慎,是因为其涉及到高昂的成本、复杂的技术以及较长的研发周期等多方面因素。芯片设计在进入流片阶段前,虽经过大量的模拟验证,但实际流片过程仍存在诸多不确定性。一旦流片失败,企业将面临巨大的经济损失和时间浪费。 但随着半导体工艺的升级,芯片设计和流片费用都要呈指数级增长。有芯片大厂算过这么一笔账: 14nm工艺芯片,流片一次需要300万美元左右(折合人民币2170万) 7nm工艺芯片,流片一次需要3000万美元(折合人民币2.17亿) 5nm工艺芯片,流片一次更是达到4725万美元(折合人民币3.41亿) 流片到底为啥那么贵?贵在哪了? 其实流片最主要的花费是晶圆(wafer)和掩模板(mask)的制作。 先说Foundary 根据Tsmc的代工价目表来看,最先进的制程3nm报价每片晶圆19865美元,折合人民币大概14.2万。  如在 2010 年左右,某芯片初创公司致力于一款高性能通用芯片的研发,由于在流片前对物理层设计的一些潜在兼容性问题预估不足,在流片后发现芯片存在严重的信号传输错误,导致该芯片无法正常工作。此次失败使得这家初创公司耗费大量资金投入的项目被迫搁置,资金链断裂,最终只能走向破产清算,这充分彰显了流片谨慎性的重要意义 Fabless流片前我们可以需要做什么? 当然各种 Signoff 、Freeze、TR 必不可少, 需要了解更多详细信息,可以私信作者(下面有微信)免费索取作者总结流程图,除了这个外,还有以下几个方面: 设计定型与验证: · 确保整个芯片设计已经完成,并通过所有必要的验证 · 进行功能验证,检验其前端设计是否用代码实现了相应的功能。 1.制造准备: · 确定工艺流程和技术参数,准备好全掩膜制造所需的全部数据。 · 检查设计规则,包括电容的长宽比、版图中的空位添加接地孔以避免闩锁效应、连接到栅上的大面积金属注意天线效应等。 2.可靠性测试: · 进行机械应力测试,通过振动、冲击等机械应力对半导体进行测试,评估半导体在机械冲击和振动环境下的可靠性。 · 高加速寿命测试(HALT),在极端条件下对半导体进行快速测试,以找出潜在的失效模式。 · 热失控测试,模拟芯片在过载或短路条件下的热行为,评估芯片在极端条件下的安全性。 · X射线和显微镜检查,使用X射线或显微镜检查芯片内部结构,识别潜在的缺陷。 · 失效分析,对失效的半导体进行详细分析,找出失效原因。 · 寿命测试,在标准工作条件下持续运行半导体,记录其性能变化,评估半导体的实际使用寿命。 3.电性测试: · 进行参数测试,检查芯片的电气参数是否在设计规范范围内 · 功能测试,验证芯片的逻辑功能和性能是否正常工作 · 静态测试,在静态条件下检测芯片的电气性能,如漏电流和功耗 检测技术: · SEM 和 Xray, IR等检查到可能的缺陷 通过上述检查工作,芯片设计公司可以在NTO前确保芯片的良率(笔者经验85%+)和寿命(相对设计寿命有一定冗余),为后续的量产打下坚实的基础。 |