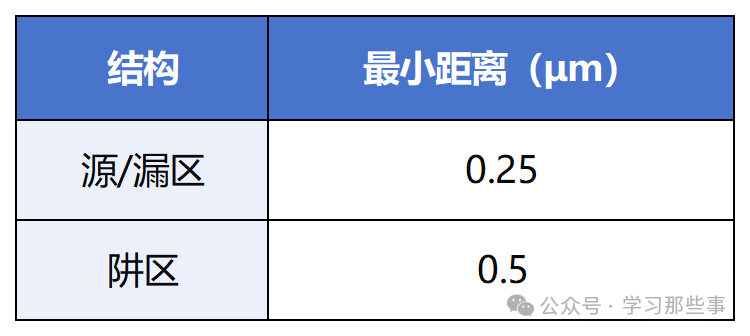

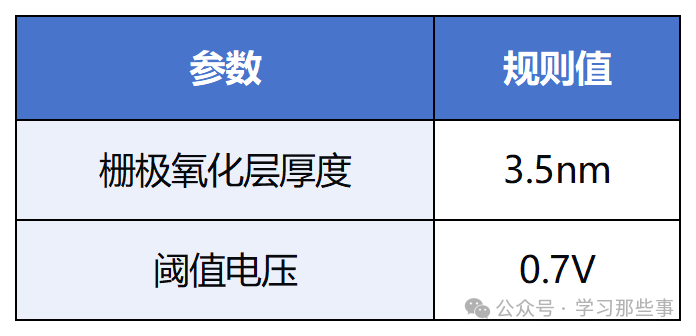

编者荐语:欢迎与我们在车规半导体认证测试服务、晶圆设计咨询服务、封装研发咨询服务以及应用相关咨询服务之领域聊聊,与各位共享共赢车规半导体产业链丰富资源,微信或电话,直接邮件CHENMINGFENG@ASI-SH.CN。。 可靠性测试结构设计研究展示 深入梳理设计规则,设计者可在可靠性测试结构优化中兼顾性能、成本与质量,推动半导体技术的持续创新。  本文分述如下: § 可靠性测试结构设计概述 § 几何设计规则介绍与应用实例 § 多项目晶圆(MPW)流片方式 1 可靠性测试结构设计概述 一、设计规则的核心参数与工艺适配 1.关键参数定义 设计规则通过定义最小线宽、间距、覆盖、露头、凹口和面积等参数,确保芯片制造的可行性。例如: ·最小线宽:在2μm工艺中,线宽不得小于2μm,以防止导线断裂。 ·间距规则:不同层导体间距需大于工艺允许的最小值(如0.5μm),避免短路。 ·归一化工艺适配:通过λ(归一化单位)实现跨工艺移植,例如定义栅极宽度为2λ,其他尺寸为整数倍,便于从2μm工艺迁移至1μm工艺。 2.性能与成品率的平衡 设计规则是成品率与性能的折中 ·保守规则:提高成品率,但可能限制性能(如增大线宽降低信号速度)。 ·激进规则:允许更小线宽或间距以提升性能,但成品率风险增加。 二、设计规则的实际应用与工具支持 1.自动化验证流程 通过DRC(设计规则检查)工具实现规则合规性验证: ·扫描与报告:工具自动检测版图中的违规项(如线宽不足、间距过小),生成修正报告。 ·迭代修正:设计师根据报告修改版图,重复验证直至所有违规项消除。 2.跨领域设计规则类比 设计规则不仅限于芯片,其他领域也有类似规范: ·建筑示例:轻钢龙骨间距≤400mm(保证结构稳定性),石膏板吊顶主龙骨间距900mm(符合力学要求)。 ·室内设计:地板铺装需30mm厚水泥砂浆找平层(防止空鼓),地暖管间距需内嵌300mm宽无纺布(防开裂)。 三、设计规则的工艺演进与未来趋势 1.先进工艺的挑战 随着工艺节点缩小(如FinFET结构),设计规则需应对三维复杂性: ·三维验证:DRC工具需评估鳍片高度、栅极包裹完整性等新参数。 ·材料特性:高介电常数材料引入后,需调整间距规则以避免寄生电容。 2.AI与数字化工具的影响 ·AI辅助优化:通过机器学习预测最佳线宽/间距组合,平衡性能与成品率。 ·实时规则更新:工艺改进后,AI工具可自动调整设计规则参数(如从2μm到1μm工艺的线宽缩放)。 四、设计规则与可靠性测试结构的关联 1.测试结构的设计约束 ·互连线:宽度需满足最小线宽要求,间距需避免电迁移效应。 ·晶体管:沟道宽度(W)和长度(L)需符合设计规则比例(如W/L≥2以抑制短沟道效应)。 ·电容与电阻:金属层厚度和面积需符合工艺规范,确保匹配精度。 2.成品率量化影响 ·规则违反的后果:线宽不足可能导致导线断裂(成品率下降5-10%),间距过小引发短路(成品率损失15%以上)。 ·经济成本:修正一次设计规则违规的平均成本约为5,000−20,000(取决于工艺节点)。 五、结论:设计规则的创新与边界探索 设计规则是工艺能力与设计自由度的边界定义者。未来趋势包括: ·动态规则调整:通过传感器实时反馈调整设计规则(如根据晶圆平整度微调间距)。 ·异构集成规则:3D堆叠芯片需定义层间对准容差(如<10nm)和TSV(硅通孔)密度规则。 ·可持续设计:结合环保材料(如低介电常数生物材料)调整设计规则,降低工艺能耗。 2.几何设计规则介绍与应用实例 一、几何图形距离定义 1.最小宽度 ·定义:封闭几何图形内边间的最小距离,由光刻工艺极限决定。 ·示例:在0.18μm CMOS工艺中,多晶硅层最小宽度为0.18μm,防止导线断裂。 2.最小长度 ·定义:同一几何图形较长方向上的边到边距离。 ·示例:金属层矩形图形的长度不得小于0.5μm,确保电流均匀分布。 3.最小间距 ·定义:相邻几何图形外边界的最小距离,避免短路。 ·示例:两层金属线间距需≥0.25μm(0.18μm工艺),防止电容耦合干扰。 4.最小延伸 ·定义:B层图形在A层图形上的单边交叠,其余方向无限制。 ·示例:接触孔需延伸过有源区0.1μm,确保可靠连接。 5.最小包含 ·定义:A层图形完全被B层图形包裹,四边均需满足最小内边距。 ·示例:有源区需完全被栅极覆盖,内边距≥0.08μm。 6.最小交叠 ·定义:两几何图形内边界的最小交叠长度,防止工艺偏差导致开路。 ·示例:多晶硅栅与有源区交叠≥0.12μm(0.18μm工艺)。 二、设计规则实例分析 1.0.18μm CMOS工艺规则 ·线条最小宽度:  ·N型注入掩膜最小距离:  ·电学设计规则:  2.设计规则检查(DRC)应用 ·错误示例:金属线宽度不足0.18μm时,DRC工具标记为红色违规区域。 ·修正方法:调整线宽至0.18μm以上,或采用更高精度光刻工艺。 3.成品率与性能平衡 ·保守设计:增大线宽至0.25μm,成品率提升5%,但信号延迟增加10%。 ·激进设计:采用0.16μm线宽,成品率下降3%,但速度提升15%。 三、版图设计工具介绍与流程优化 1.版图设计工具核心功能对比  2.工具集成与典型设计流程 ·前端设计 逻辑综合:Synopsys Design Compiler / Cadence Genus 仿真验证:Cadence Spectre / Synopsys VCS ·后端设计 布局布线:数字设计,Synopsys IC Compiler II → Astro(传统流程);模拟/混合信号:Cadence Virtuoso → Innovus(数字部分) 验证工具链: DRC/LVS,Mentor Calibre / Cadence Assura;时序分析,Synopsys PrimeTime / Cadence Tempus ·协同设计示例 场景:28nm工艺数字SoC设计(含模拟IP) 流程:使用Virtuoso完成模拟IP版图设计;通过IC Compiler II进行数字部分布局布线;采用Encounter进行全芯片时序优化;通过Calibre进行全芯片DRC/LVS验证。 3.工具选择策略与成本优化 ·学术研究/教育:推荐工具,Tanner L-Edit + Open-Source PDK;优势,低成本、易上手,支持基础工艺节点(如180nm)。 ·初创公司/小型项目:推荐工具链,Synopsys Custom Compiler + IC Compiler II(云端订阅);优势,按需付费,减少初期投资,支持先进节点。 ·大规模SoC设计:推荐工具链,Cadence Genus + Innovus + Voltus;优势,全流程集成,支持多电压域和复杂功耗管理。 ·硅光集成设计:推荐工具,Tanner L-Edit(光子器件) + Synopsys Sentaurus(光电仿真);优势,覆盖从器件到系统的全设计流程。 3.多项目晶圆(MPW)流片方式 一、MPW的核心价值与产业影响 1.成本革命 ·数据对比:非MPW流片单次成本约50,000(12英寸晶圆),MPW模式下单个项目成本可低至5,000(按10个项目分摊),成本下降90%。 工艺节点敏感性:先进工艺(如7nm)中,单一项目流片成本超过$300万,MPW模式使中小设计团队也能承担试验。 2.设计效率提升 ·周期缩短:传统流片需等待整片晶圆订单,MPW服务提供定期流片批次(如每月1次),设计验证周期缩短50%以上。 ·快速迭代:支持敏捷开发模式,设计者可在数周内完成设计-流片-测试闭环。 3.生态培育 ·人才孵化:高校通过MPW开展实践教学,如复旦大学每年培养数百名IC设计学生。 ·企业成长:初创企业利用MPW验证产品原型,降低融资门槛,企业存活率提升3倍。 二、MPW技术流程介绍(以0.18μm CMOS为例) 1.设计阶段 ·输入格式:设计单位提交GDSII或CIF文件,包含: ·标准单元库:逻辑门、触发器(如NAND2X1、DFFRX1)。 ·IP核:ADC、PLL等硬核(需预先验证)。 ·设计规则检查(DRC):确保层间距、线宽等符合工艺要求。 2.MPW整合 ·虚拟芯片生成:MPW中心将多个设计拼接成矩形布局,晶圆利用率提升至85%以上。 ·掩模优化:采用层次化掩模技术,减少掩模数量(如4层金属工艺需4张掩模)。 3.流片与测试 ·工艺参数(0.18μm CMOS示例) 电源电压:1.8V/3.3V 阈值电压:0.5V(NMOS)/ -0.5V(PMOS) 特征频率:>200MHz ·测试流程 晶圆切割:激光划片,精度±5μm。 在片测试:使用探针卡测量I/O特性。 封装测试:QFP/BGA封装后,进行功能验证。  三、MPW服务的未来趋势 1.先进工艺扩展 ·FinFET支持:MPW服务将覆盖7nm/5nm节点,采用多图案光刻技术。 ·3D集成:支持TSV(硅通孔)设计,提供堆叠芯片MPW服务。 2.自动化工具升级 ·智能布局算法:基于机器学习优化晶圆利用率,减少空白区域20%。 ·云端协同设计:支持多团队实时协作,版本控制自动化。 3.绿色MPW计划 ·环保工艺:采用低能耗工艺,减少碳足迹。 ·废品回收:未通过测试的芯片进行金属层回收。 通过MPW服务,设计者可在成本、周期、性能之间找到最优平衡,推动半导体技术的持续创新。随着工艺节点的演进和服务模式的升级,MPW将成为IC设计生态中不可或缺的“加速器”。 |