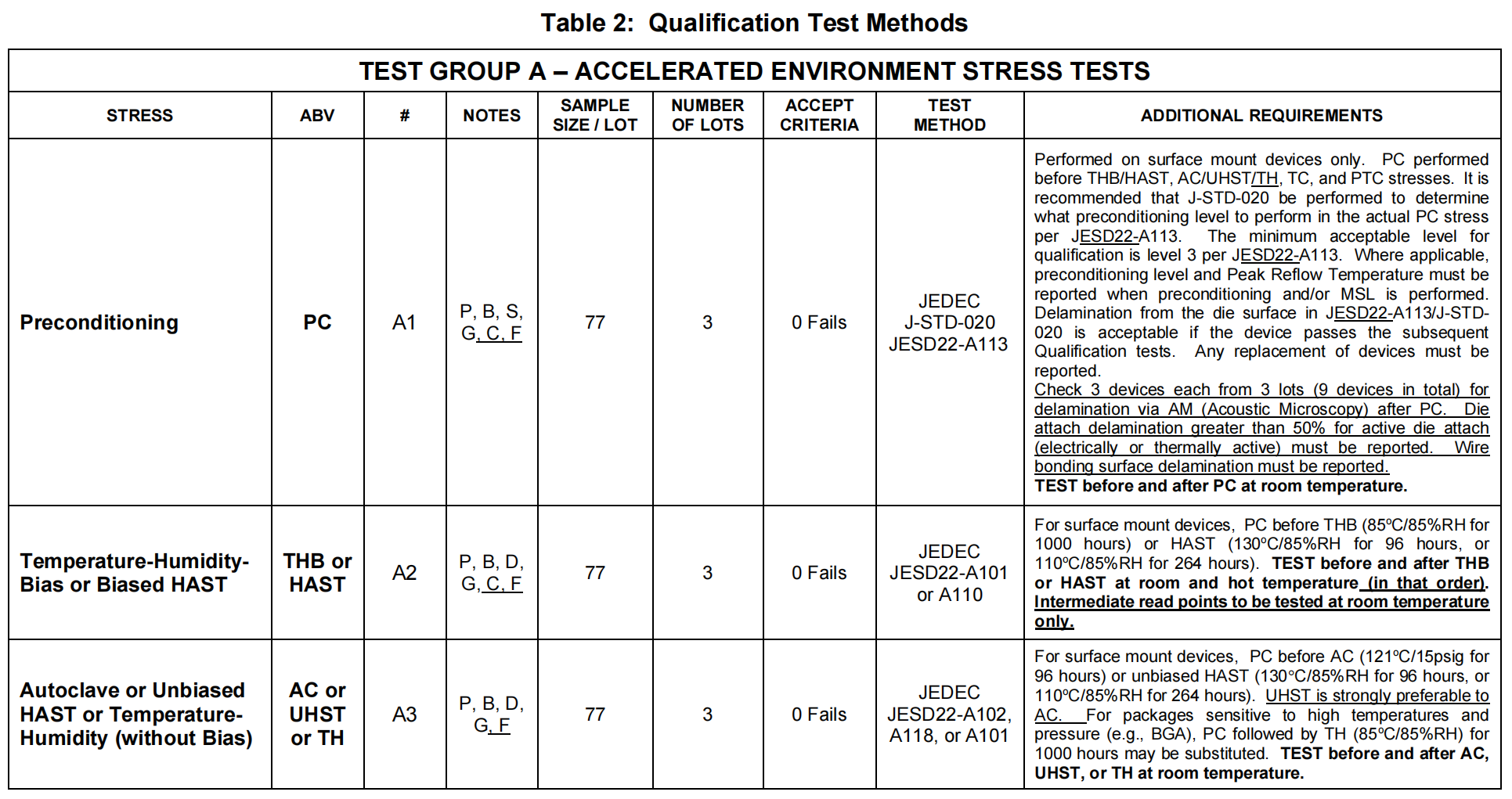

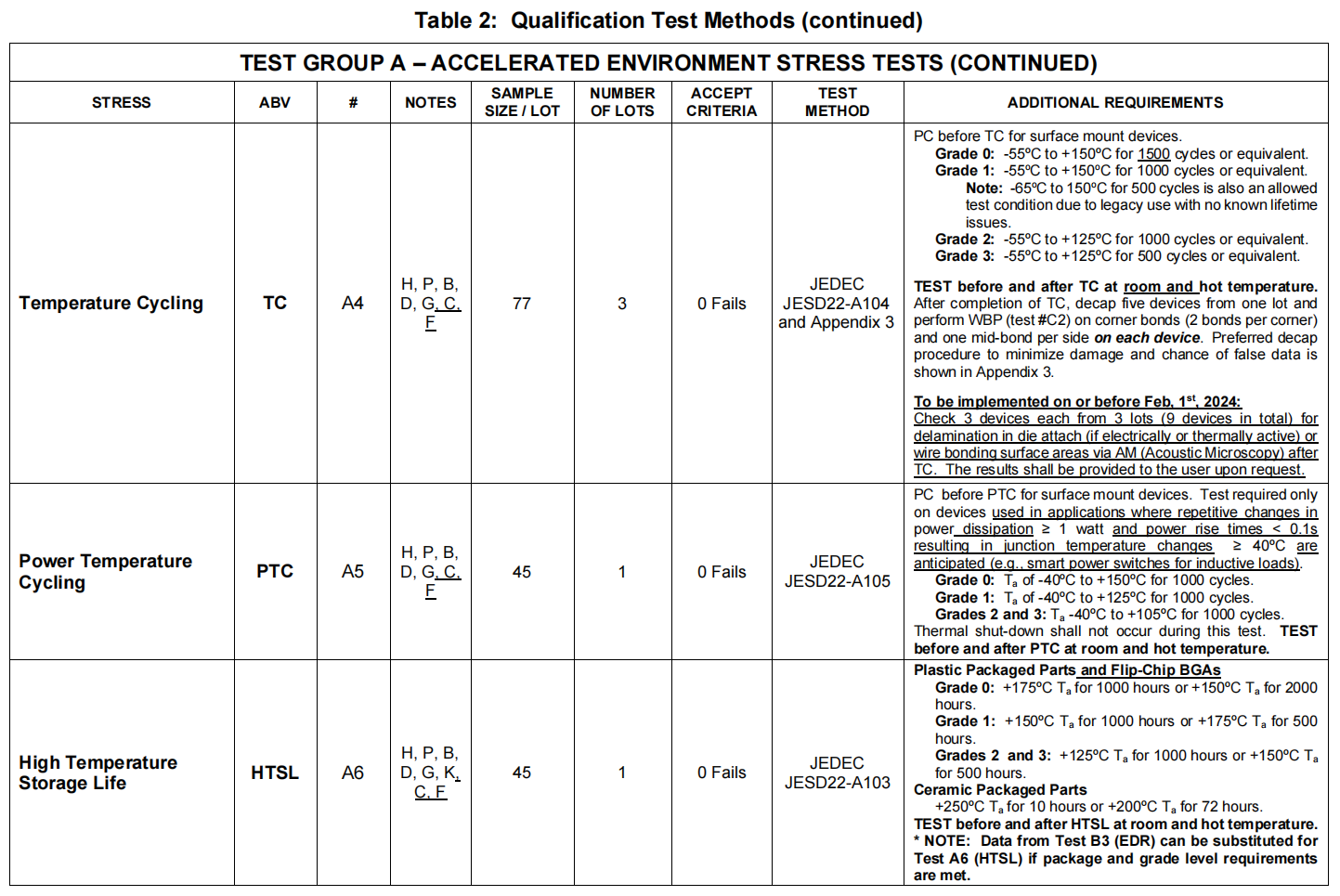

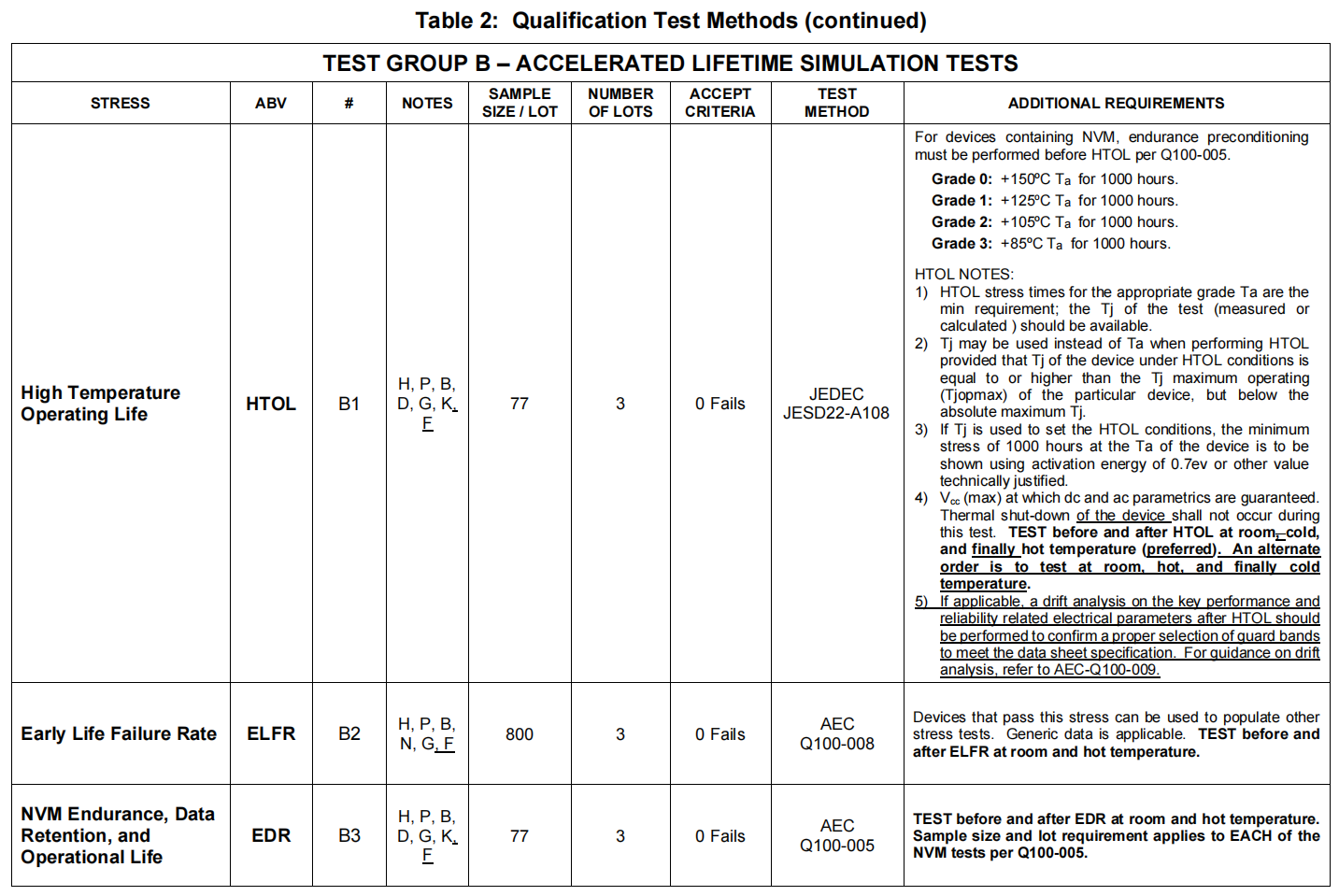

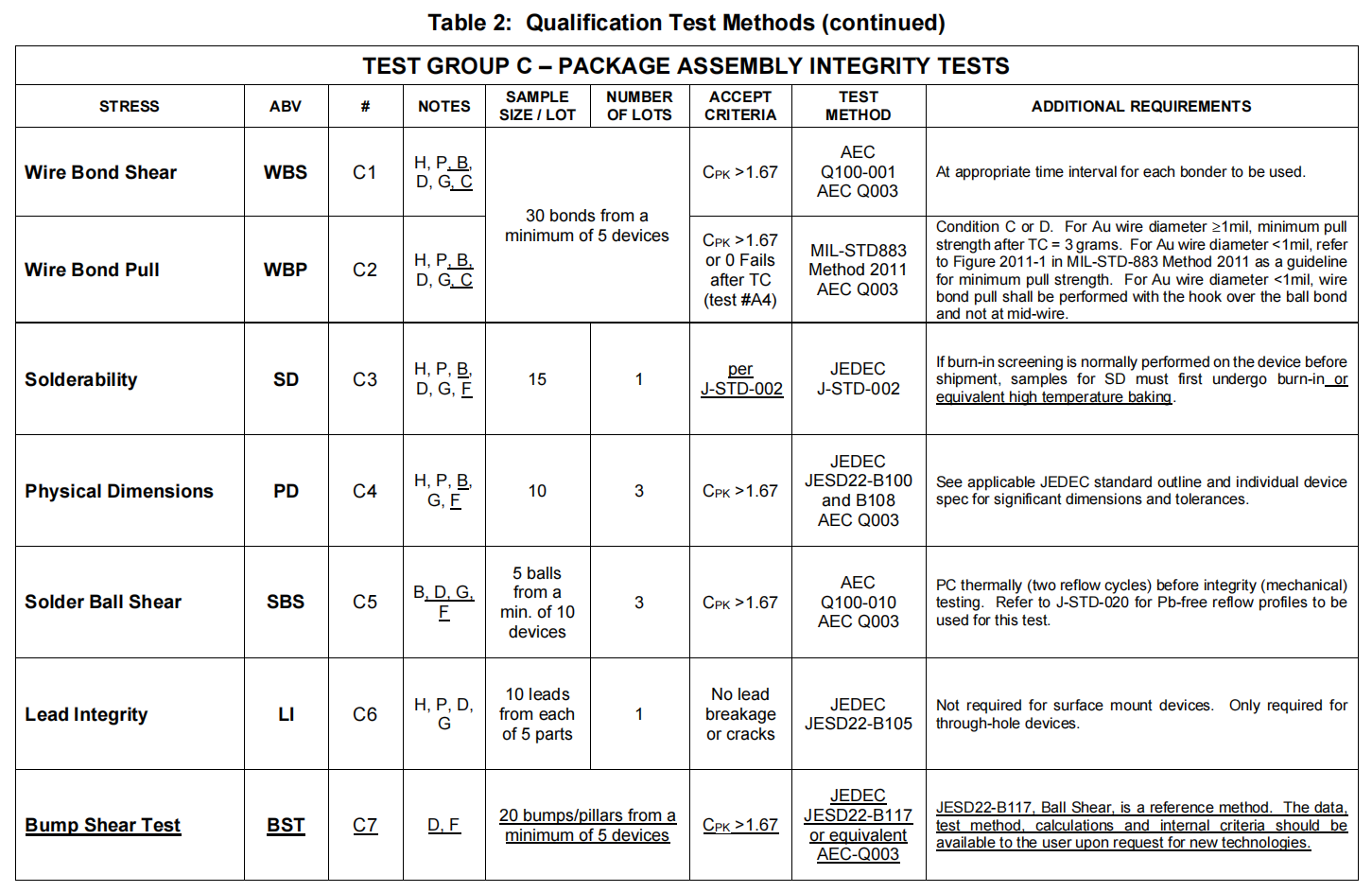

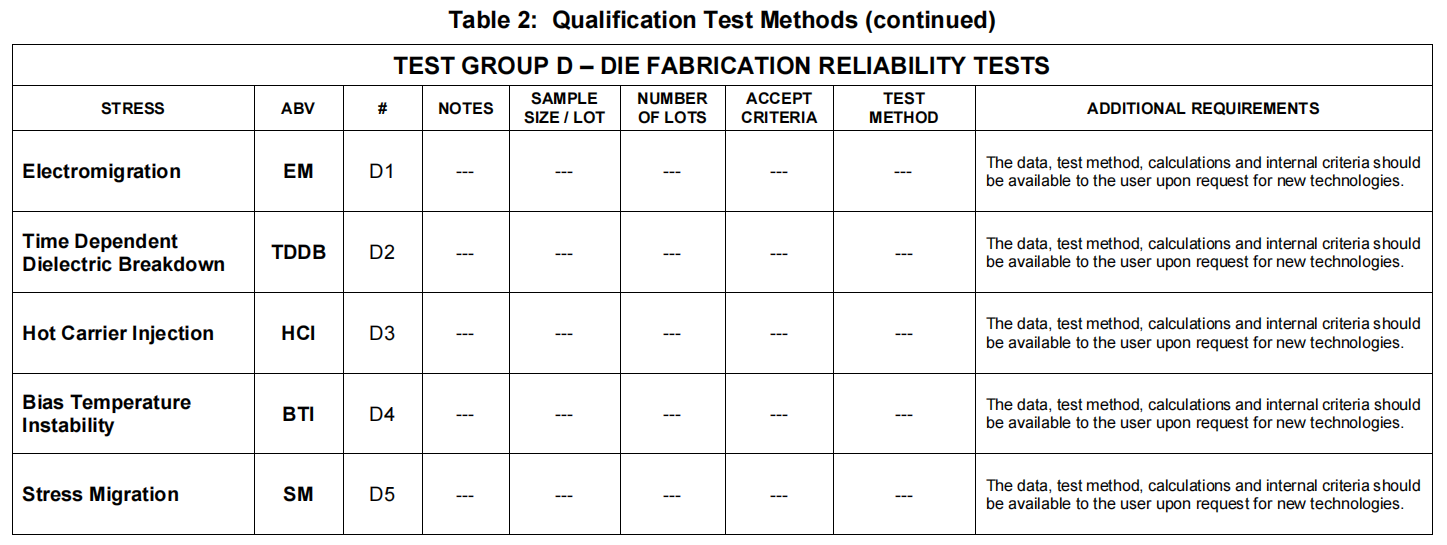

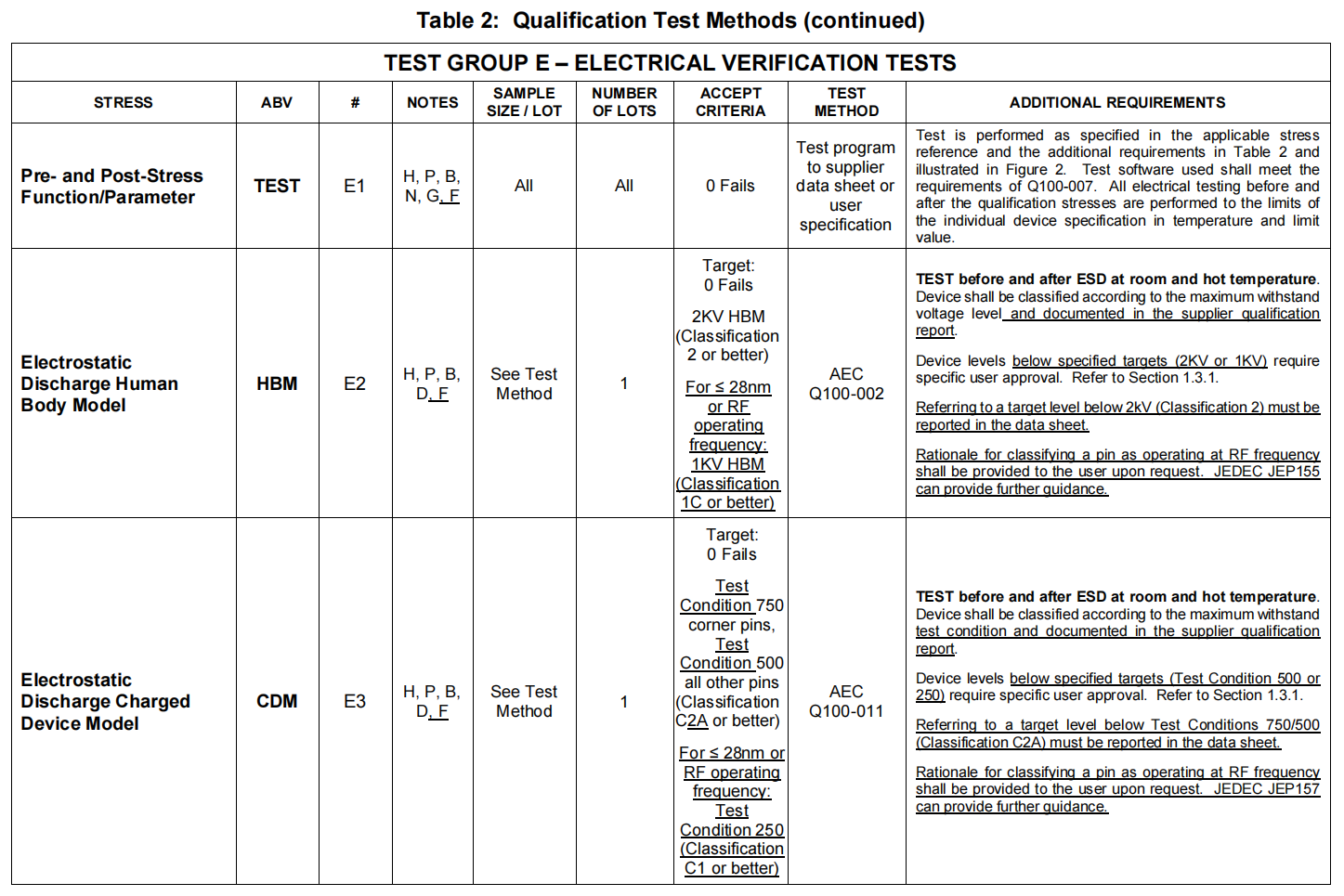

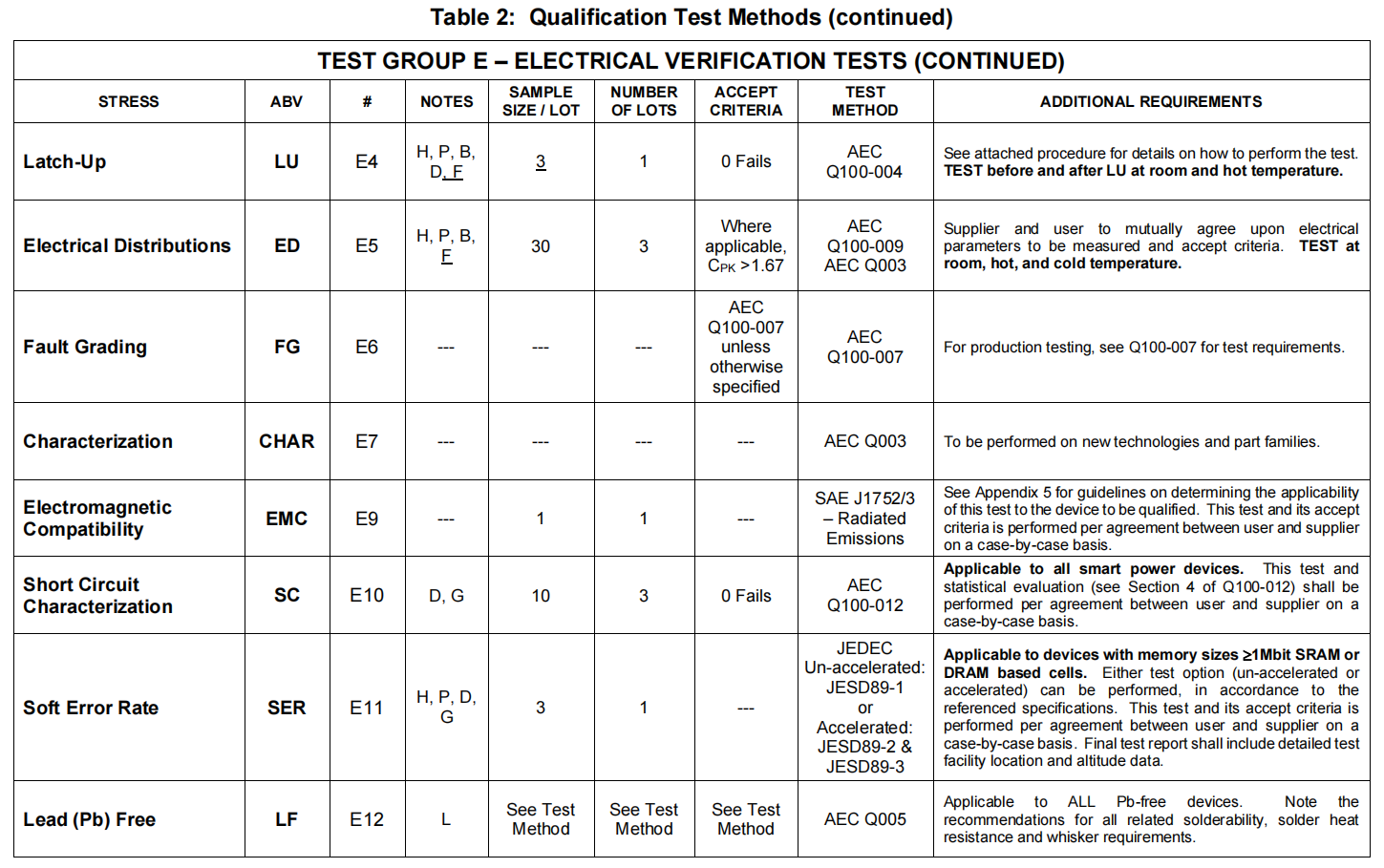

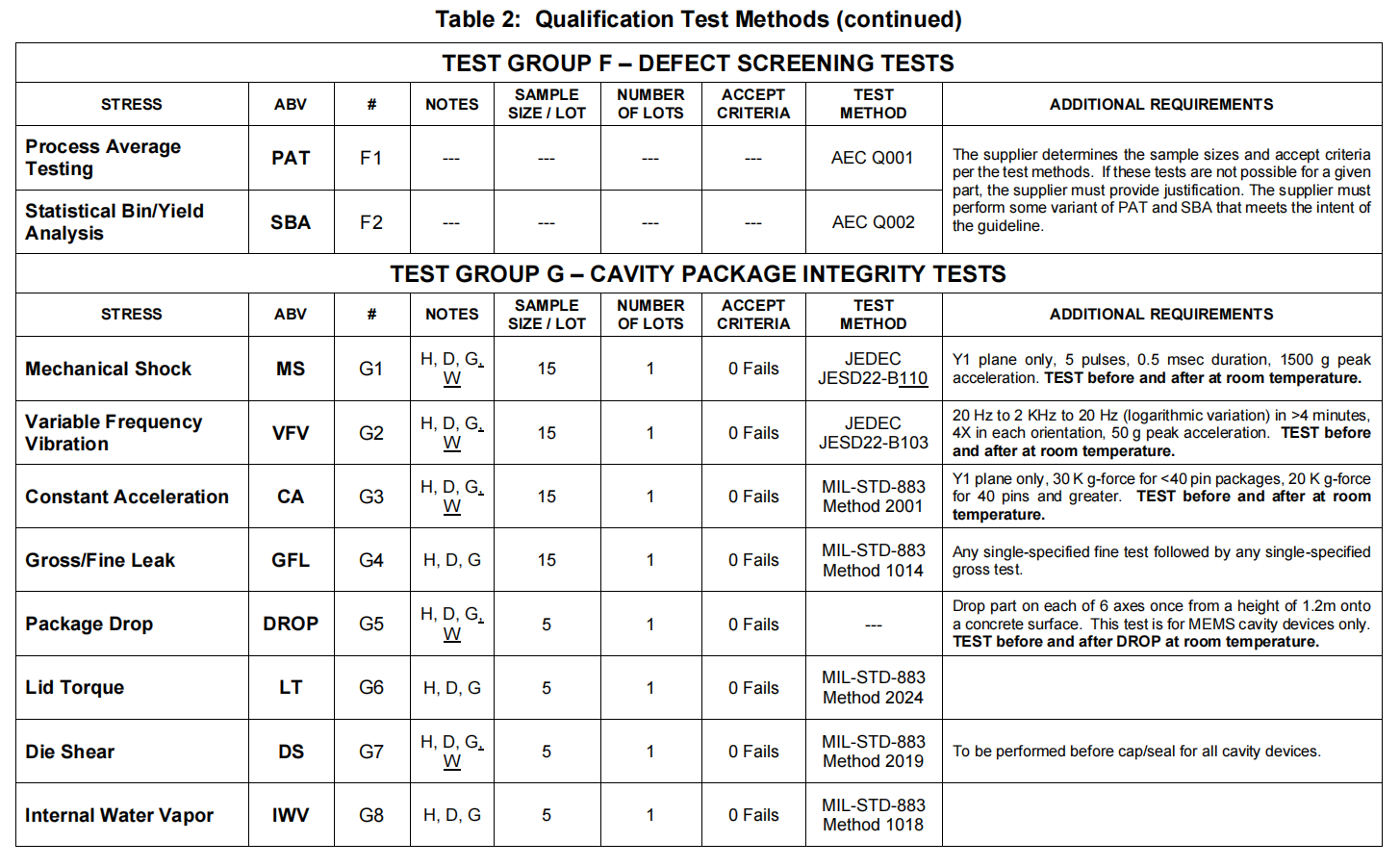

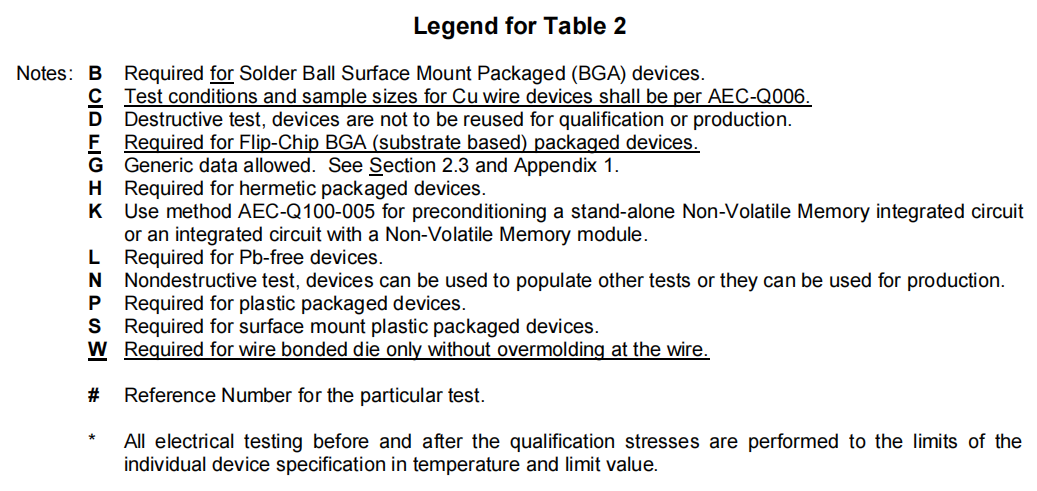

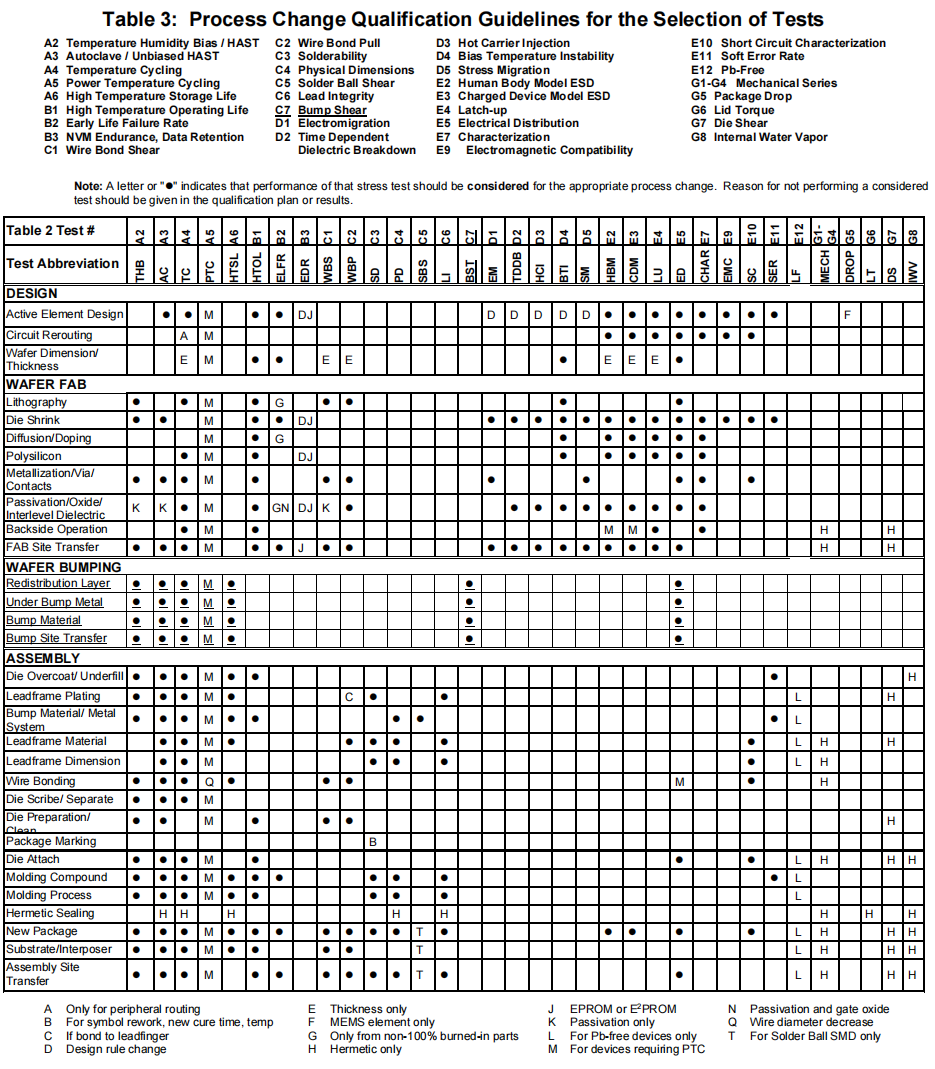

一、新器件认证与变更器件认证上期主要围绕AEC-Q100中的GROUP A~GROUP G的7组测试项目展开,对应的是标准文档表2的内容。         针对新器件的认证,AEC-Q100规定: · 对于每个资格认证,供应商必须有所有这些测试的数据,无论是器件上合格的应力测试结果还是可接受的通用数据。 · 应对同一通用家族中的其他器件进行审查,以确保该家族中没有常见的故障机制。 · 无论何时,使用通用数据的理由必须由供应商证明并由用户批准。 针对变更器件的认证,AEC-Q100规定: · 当供应商对产品和/或工艺进行更改,影响(或可能影响)器件的外形、安装、功能、质量和/或可靠性时,需要对器件进行重新认证(见表3的指导原则)。 · 附录1中定义的产品的任何变更都需要用表3来确定重新认证的测试计划,进行表2中列出的适用测试。表3应用于确定哪些测试适用于特定器件变更的资格认证,或是否可以为该测试提交等效的通用数据。 表3是用于选择试验的工艺变更认证指南,如下图所示。  表2如同一个矩阵,横向表示可靠性测试的试验项目,纵向表示设计或工艺材料/参数/流程。字母或“●”表示对于适当的工艺变化应考虑该应力测试的表现。不进行测试的原因应在资格鉴定计划或结果中给出。 DESIGN 设计 Active Element Design 有源元件设计 Circuit Rerouting 回路重新走线 Wafer Dimension/Thickness 晶圆尺寸/厚度 WAFER FAB 晶圆制造 Lithography 光刻 Die Shrink 芯片收缩 Diffusion/Doping 离子注入/掺杂 Polysilicon 多晶硅 Metallization/Via/Contacts 金属化/通孔/触点 Passivation/Oxide/Interlevel Dielectric 钝化/氧化物/层间介质 Backside Operation 背面操作 FAB Site Transfer 制造场所转移 WAFER BUMPING 晶圆凸块 Redistribution Laver 重布线层 Under Bump Metal 凸块下金属化 Bump Material 凸块材料 Bump Site Transfer 凸块站点转移 ASSEMBLY 封装 Die Overcoat/ Underfill 芯片模套/底部填充胶 Leadframe Plating 引线框电镀 Bump Material/ MetalSystem 凸块材料/金属化系统 Leadframe Material 引线框材料 Leadframe Dimension 引线框尺寸 Wire Bonding 邦线 Die Scribe/ Separate 芯片划片/分割 Die Preparation/Clean 芯片准备/清洁 Package Marking 封装打码 Die Attach 固晶 Molding Compound 塑封料 Molding Process 塑封工艺 Hermetic Sealing 气密封装 New Package 新封装 Substrate/lnterposer 基板/中介层 Assembly SiteTransfer 封装厂转移 字母的含义如下: A 仅用于外围布线 B 适用于元件返工,新的固化时间,温度 C 如果键合到引脚上 D 设计规格更改 E 仅针对厚度 F 仅针对MEMS的元件 G 仅来自非100%老化零件 H 仅针对密封器件 J EPROM或EEPROM K 仅针对钝化 L 仅适用于无铅器件 M 适用于需要进行PTC的器件 N 钝化和栅极氧化层 Q 线径减小 T 仅适用于焊球SMD器件 以WAFER FAB中FAB Site Transfer为例:按照标准要求,需要对以下20项(并非所有测试适用于所有器件,例如PTC、EDR等)进行测试并确保通过,从而证明芯片符合车规认证要求。 A组(含PC):THB、AC、TC、PTC B组:HTOL、ELFR、EDR C组:WBS、WBP D组:EM、TDDB、HCI、BTI、SM E组:HBM、CDM、LU、ED G组:MECH、DS 以ASSEMBLY中New Package为例:按照标准要求,需要对以下21项(并非所有测试适用于所有器件,例如LI、LF等)进行测试并确保通过,从而证明芯片符合车规认证要求。 A组(含PC):THB、AC、TC、PTC、HTSL B组:HTOL、ELFR C组:WBS、WBP、SD、PD、SBS、LI E组:HBM、CDM、ED、SC、LF G组:MECH、DS、IWV 以ASSEMBLY中Assembly Site Transfer为例:按照标准要求,需要对以下17项(并非所有测试适用于所有器件,例如MECH、DS等)进行测试并确保通过,从而证明芯片符合车规认证要求。 A组(含PC):THB、AC、TC、PTC B组:HTOL、ELFR C组:WBS、WBP、SD、PD、SBS、LI E组:ED、SER G组:MECH、DS、IWV 二、通用数据与认证家族 AECQ100为使用通用数据提供了以下指南,以加速和简化供应商和用户的资格认证过程。关于如何在适当时候使用通用数据,供应商和用户可以使用本指南达成一致。 对于归为产品认证家族的器件,它们都必须共享如下所定义的相同的主要产品、工艺和材料元素。特定产品的认证将在但不限于以下所列类别中定义。A1.1节中定义的关键产品功能细节以及A1.2节和A1.3节中定义的关键工艺步骤和材料不需要完全匹配,但应通过技术论证应用家族通用数据的最坏情况。 除第4.2节的器件具体要求外,当一个家族成员成功完成认证时,同一产品认证家族中的所有产品均得到关联认证。对于涉及多个属性(如地点、材料、工艺)的广泛变化,请参考本附录第A1.5节和Q100第2.4节,将选择最坏情况下的测试手段以涵盖所有可能情况。 A1.1 产品 a.产品功能(例如,运算放大器、调节器、微处理器、Logic - HC/TTL)b.工作电源电压范围 c.指定的工作温度范围d.指定的工作频率范围 e.Fab技术设计库单元 · 存储IP(例如单元结构、建筑块) · 数字设计库单元(如电路块、IO模块、ESD单元)和/或模拟设计库单元(如有源电路元件、无源电路元件)在数据表上的电压水平,以及在数据表上或更好的温度范围和功耗 · 存储库单元格的速度/性能 f.存储类型和大小g.焊盘下的有源电路设计规则h.由供应商定义的其他功能特性对于指定在不同电源下(如5.0 V和3.3 V)运行的器件,应提供两个供电范围的产品认证家族数据。 对于指定在不同温度范围内运行的器件,需要提供数据表中器件温度下3个批次的表2 E1 TEST测试数据。在Q100表2中A、B、E和G组中规定的温度下的应力分类必须等于或高于认证的器件。在Q100表2中A、B、E、G组中规定的温度下,需要提供来自产品家族在数据表器件频率的3个批次的表2 E1 TEST测试数据。数据表中设备频率的产品系列数据需要符合Q100表2规定的温度A、B、E和G。所有存储类型必须认证3个批次以上,且使用最大存储规格取得家族器件的认证。如果要认证的器件存储规格大于已经取得认证的器件,则供应商必须对更大存储配置的器件进行至少1个批次的测试。 A1.2 晶圆工艺 每种工艺技术(例如CMOS、NMOS、双极)必须单独考虑和认证。无论多么相似,一种基本晶圆技术的工艺都不能用于另一种技术。对于BiCMOS器件,必须根据所考虑的电路从适当的技术中获取数据。当工艺或材料发生改变时(指南见表A1.1和表A1.2),“最坏情况”家族需要重新认证且进行适当的测试。以下列出了定义一个晶圆厂工艺的重要特性: a.晶圆制造技术(例如CMOS,NMOS,Bipolar) b.晶圆制造工艺-由以下列出的相同属性构成 · 电路元件特征尺寸(例如布局设计规则、芯片收缩、接触、栅极、绝缘) · 基板(例如定位、掺杂、外延、晶片尺寸) · 掩模数(供应商必须证明放弃此要求的理由) · 光刻工艺(例如接触与投影、电子束和X射线、光刻胶极性) · 掺杂工艺(例如扩散和离子注入) · 栅极结构、材料和工艺(例如多晶硅、金属、硅化物、湿刻蚀与干刻蚀) · 多晶硅材料、厚度范围和层数 · 氧化工艺和厚度范围(例如栅极和场氧化物) · 层间介电材料和厚度范围 · 金属化材料、厚度范围和层数 · 钝化工艺(例如钝化氧化物开口)、材料和厚度范围 · 芯片背面制备工艺和金属化 c.晶圆厂站点 A1.3 封装工艺-塑料、陶瓷、或倒装BGA 塑料和陶瓷封装技术的工艺必须单独考虑和认证。对于属于认证家族的器件,它们都必须共享以下定义的相同主要工艺和材料元素。当工艺或材料发生变化时,需要通过适当的测试重新进行家族认证。供应商必须向用户提交技术证明,以支持接受与认证器件不同的引脚(球)数、芯片尺寸、基板尺寸/材料/厚度、焊盘尺寸和芯片长宽比的通用数据。供应商必须拥有技术数据,以证明接受通用数据的合理性。定义认证家族的重要属性如下:a.封装类型(例如 DIP, SOIC, PLCC, QFP, PGA, PBGA, FC-BGA) · 同一封装类型下的最坏情况(例如由于热膨胀系数不匹配导致的封装翘曲) · 焊盘(标志)尺寸(最大和最小尺寸)符合所考虑的芯片尺寸/长宽比的要求 · 基底材料(例如PBGA、FC-BGA) · 非封装器件(如裸芯片、WL-CSP)不在本节范围内 b.封装工艺-由下面列出的相同特性组成 · 引线框架基础材料 · 引线框架镀层工艺和材料(封装内部和外部) · 芯片头/热焊盘材料 · 芯片粘贴材料 · 绑定线材料和直径 · 绑定线方式,向下键合和工艺 · 塑料模具复合材料、有机基材材料或陶瓷封装材料 · 焊球金属化系统(如适用) · 散热器类型、材料和尺寸 · 填埋材料 · 再分配层、凸块下金属化(UBM),以及凸块材料 · 用于结合倒装BGA的热界面材料 · 塑料模具复合供应商/ID · 芯片制备/成型 c.封装站点 A1.4 认证/再认证批次要求

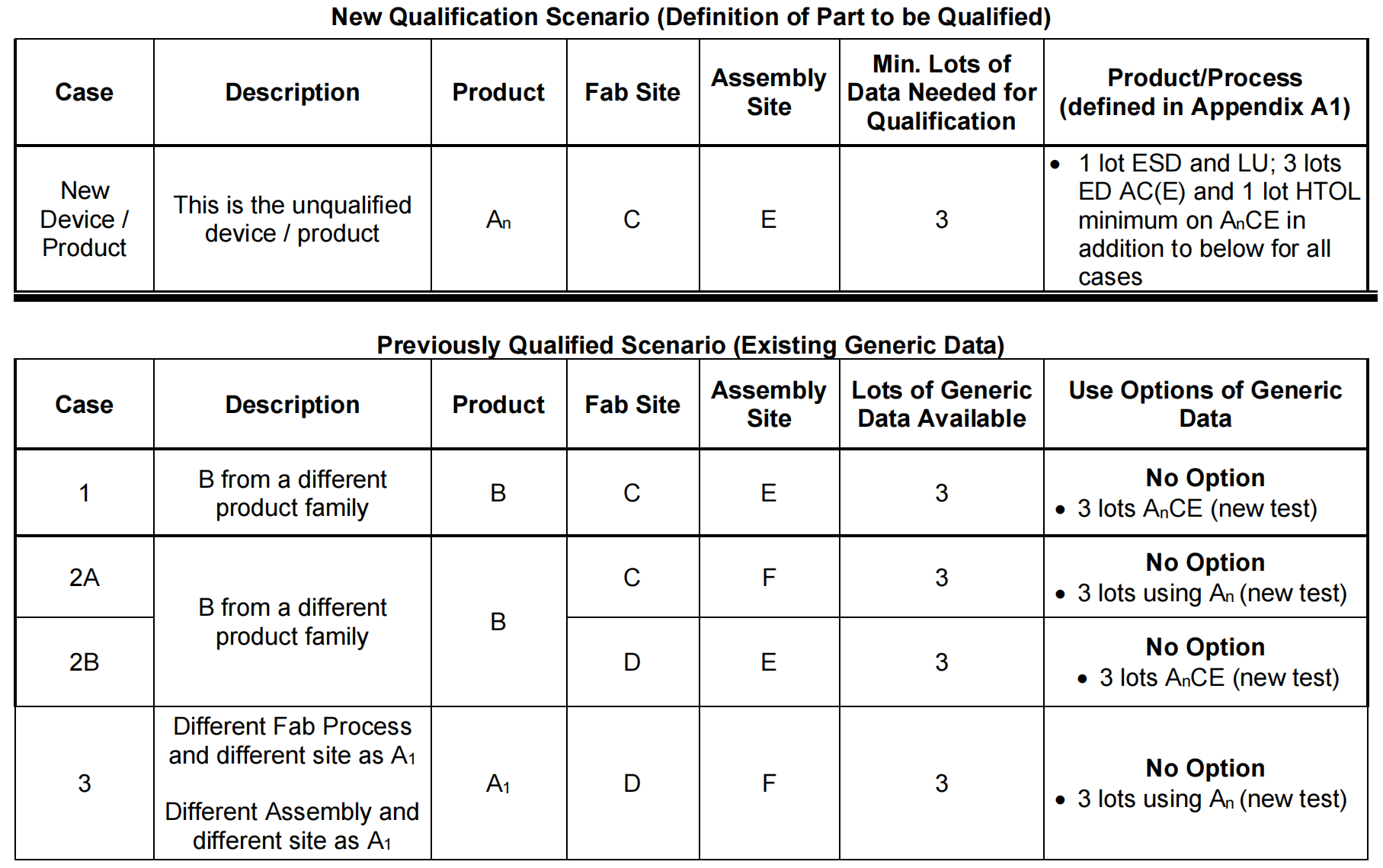

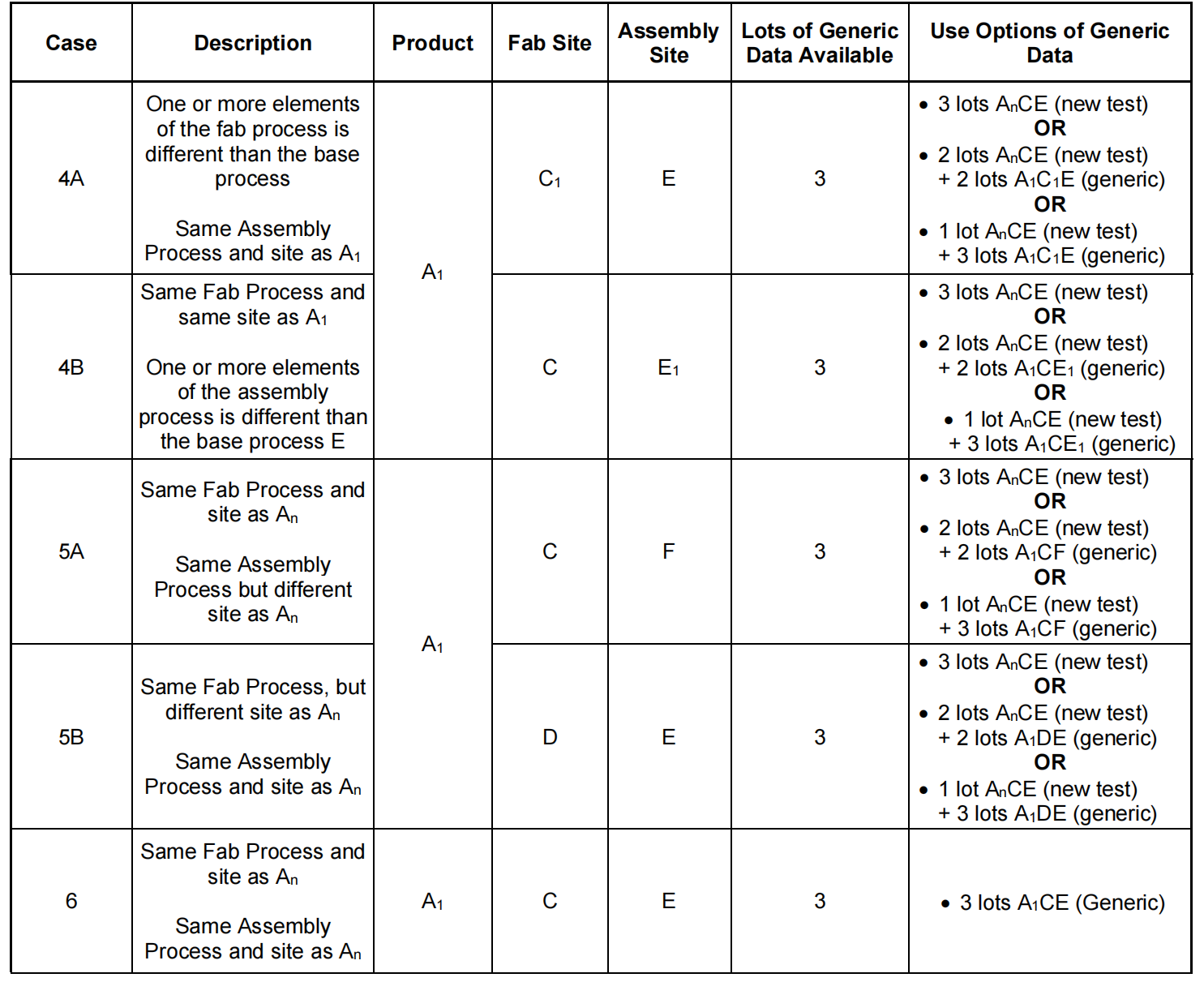

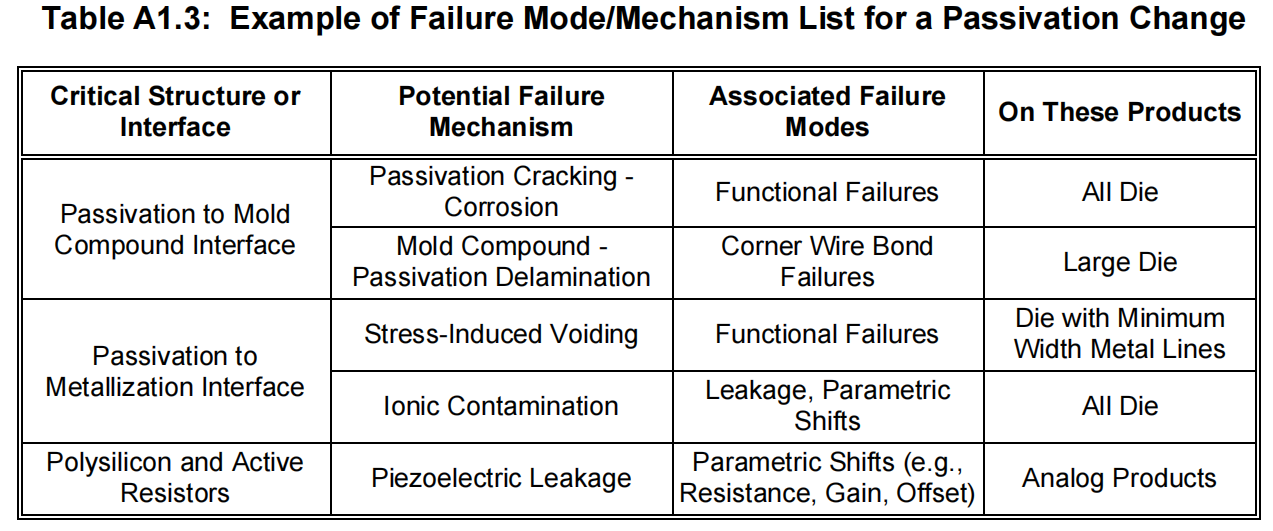

表中通用数据部分列出的案例表示产品和站点组合以前已经经过了认证且存在通用数据的场景。在表格的认证部分 ,每种情况描述的通用数据使用选项定义了器件An允许使用的通用数据。 表A1.2的使用指南: 1. 产品An是属于产品家族A中有待认证的产品。 2. 产品A1应该是产品家族中一个代表性的、可能是一个更复杂的覆盖最多(如果不是全部)的其他家族成员的案例家族成员(例如60V调节器相比45V调节器,8通道相比4通道运放)。 3. 相同的Fab是相同的工艺节点和材料。不同的Fab具有一个或多个不同的工艺要素。 4. 相同的装配是相同的工艺、材料和封装类型。不同的装配有一个或多个不同的工艺、材料元素或封装元素。 5. 新的测试是根据4.1节进行的认证测试 6. Fab工艺C1与C相同,除一个或多个不同的元素(例如金属Al和Cu)。 7. 组装工艺E1与E相同,除一个或多个不同的元素(例如,Al和Cu绑定线、模塑化合物)。 8. 产品B在功能上不同于产品A(例如逻辑与模拟器件、电压调压器与放大器)。 9. 产品复杂性的增加会降低下表部分的适用性。 A1.5 多站点和家族变更的认证 A1.5.1 多个站点 当需要认证或重新认证的特定产品或工艺属性将影响多个晶圆厂或封装厂时,每个受影响的地点至少需要进行一次测试。 A1.5.2 多个家族 当需要认证或重新认证的特定产品或工艺属性将影响多个晶圆厂家族或封装家族时,认证测试方式应该为1)预计对变更属性最敏感的家族中,每个家族每个器件类型1个批次 或 2)如果只有一个或两个家族存在,最敏感家族的3个批次(来自任何可接受的通用数据和应力测试数据的组合)。 以下是跨许多工艺和产品家族的认证变更的推荐流程 a. 确定受到所提出的工艺变更影响的所有产品。 b. 确定可能会受到所提出的工艺变更影响的关键结构和接口。 c. 确定并列出关键结构和接口的潜在失效机制和相关失效模式(请参见表A1.3中的示例)。请注意,步骤(a)到(c)等价于创建一个FMEA。 d. 根据与待评估的结构和器件敏感性相关的相似特性来定义产品分组或家族,并提供技术判据证明分组的基本原理。 e. 提供认证测试计划,包括变更的描述、测试矩阵以及能够解决每个潜在失效机制和相关失效模式的代表性产品。 f. 必须在每个受影响的工艺步骤的每个站点展示强大的过程能力(例如,每个过程步骤的控制,过程中涉及的每个设备的能力,所有受影响站点的逐步工艺等效性)。  表A1.3给出了一个针对钝化层变更的失效模式/机制清单的例子。关键的结构或界面有塑封料界面的钝化层、金属化界面钝化层、多晶硅和有源电阻。 对于塑封料界面钝化层:潜在的失效机制包括钝化层开裂腐蚀和塑封料与钝化层分离。前者相关失效模式为功能失效,所有芯片都可能会发生;后者相关失效模式为角落引线键合失效,发生于比较大的芯片。 对于金属化界面钝化层:潜在的失效机制包括应力诱失空洞和离子污染。前者相关失效模式为功能失效,发生于具有最小金属线宽度的芯片;后者相关失效模式为泄漏和参数漂移,所有芯片都可能会发生。 对于多晶硅和有源电阻:潜在单位失效机制为压电泄漏,相关失效模式为参数漂移(例如电阻、增益、失调),发生于模拟产品。 注:文中所有表格截图均取自于AEC-Q100 Rev J标准原文档。 |