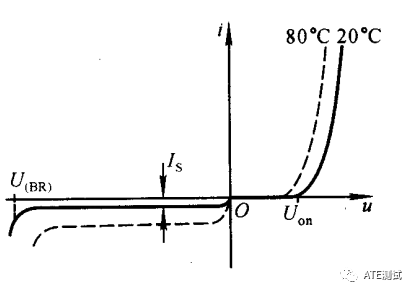

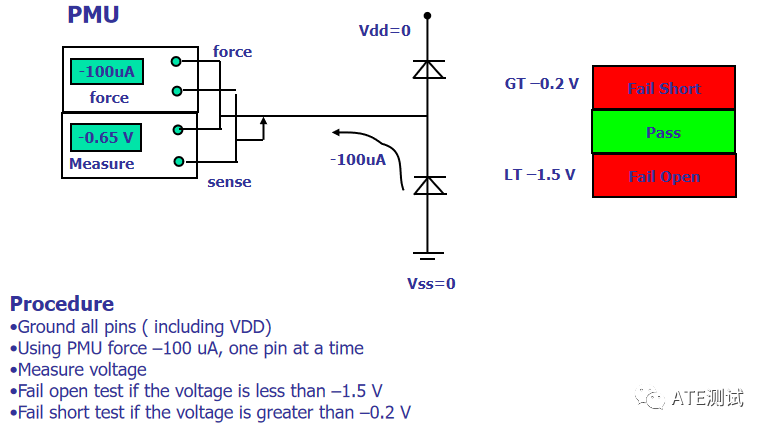

开短路测试open/short test也称为continuity test或contact test,它是一种非常快速发现芯片的各个引脚间的是否有开短路缺陷,例如晶圆阶段的制程缺陷,封装成品阶段打线缺陷,引脚ESD损坏,通常都会被放测试程序的最前面.它还能及时发现测试时接触是否良好,探针卡或测试座是否有问题.OS测试的测试原理比较简单,分为对VDD和VSS测试,一般来说芯片的每个引脚都有ESD保护电路,是两个首尾相接的二极管,一端接VDD,一端接VSS,根据二级管特性曲线,正常二极管导通压降约为0.65V左右,下图为对电源和对地的OS测试原理图    下面介绍主流ATE的几种OS测试方法: 1. 模拟源PMU串行测试,即每一根引脚单独进行测试,优点是直观明了,可以快速查看是哪根引脚有问题,缺点是测试时间过长,影响测试效率 2. 模拟源PMU并行测试,即除VDD/GND外所有引脚同时进行测试,优点是测试时间比较快,缺点是无法诊断pin to pin之间短路问题 3. 数字源DPU先并行测试,即运行OS pattern测试,如若pattern fail, 再利用模拟源PMU串行测试 综上第三种方法是一种最优OS测试方案,可以极大的缩短测试时间,所以我们在设计测试loadboard时需要充分考虑分配数字源和模拟源给各引脚 |