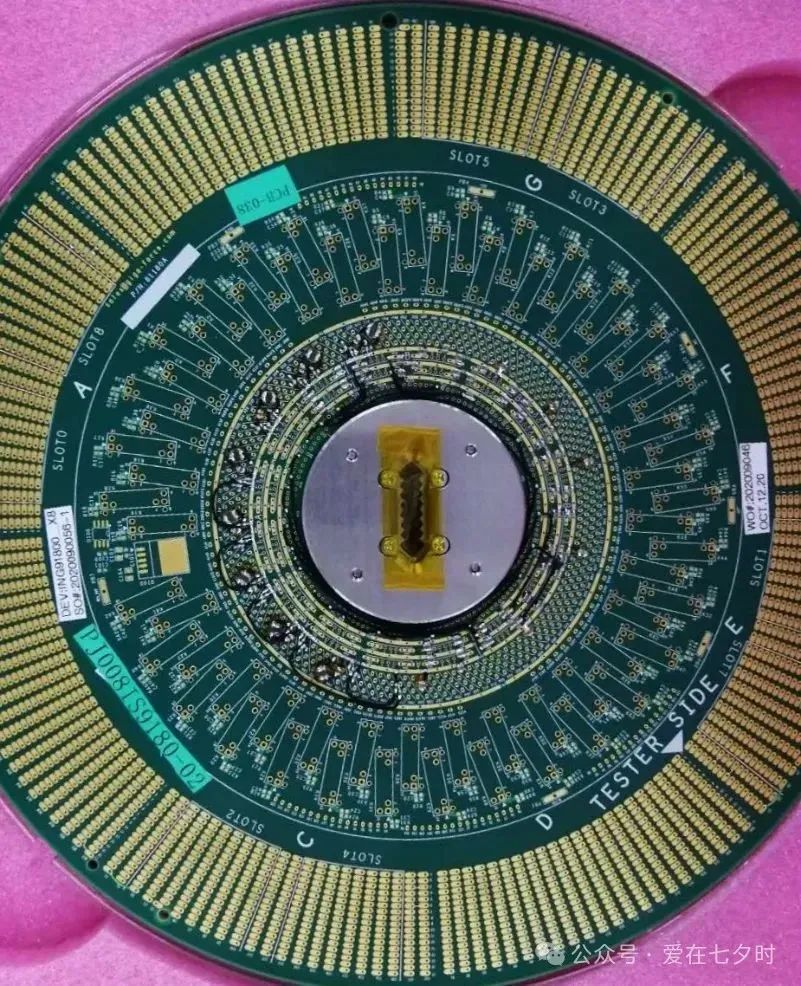

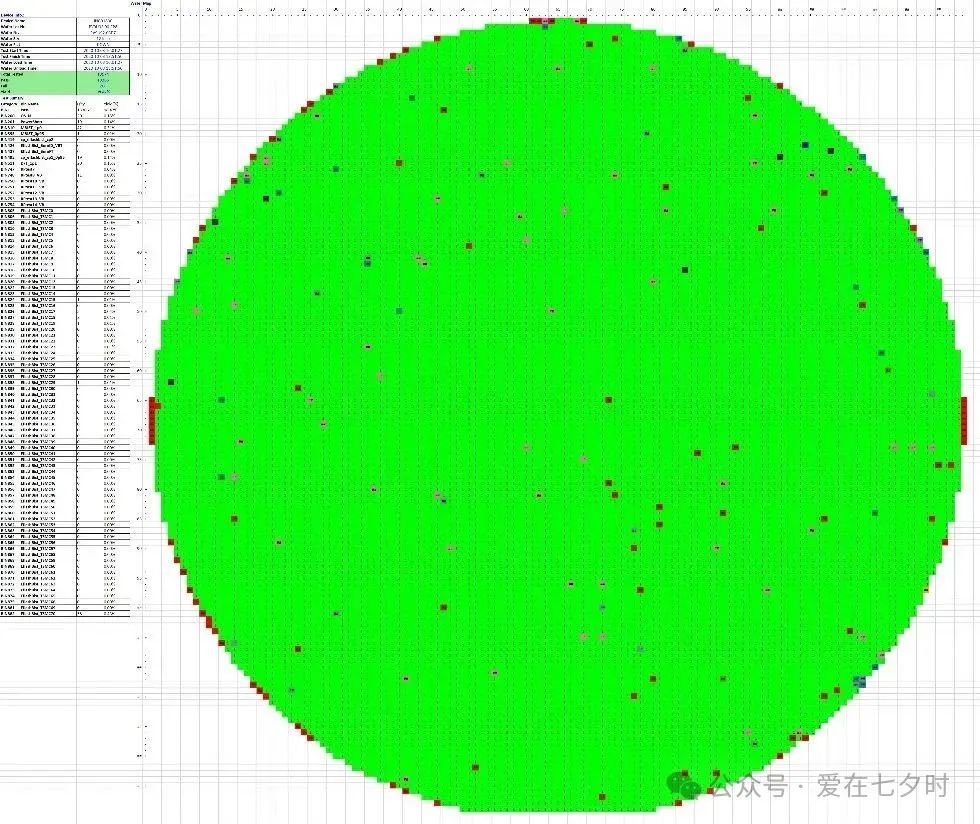

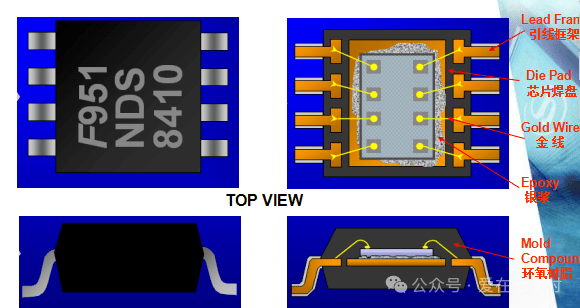

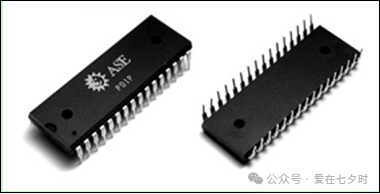

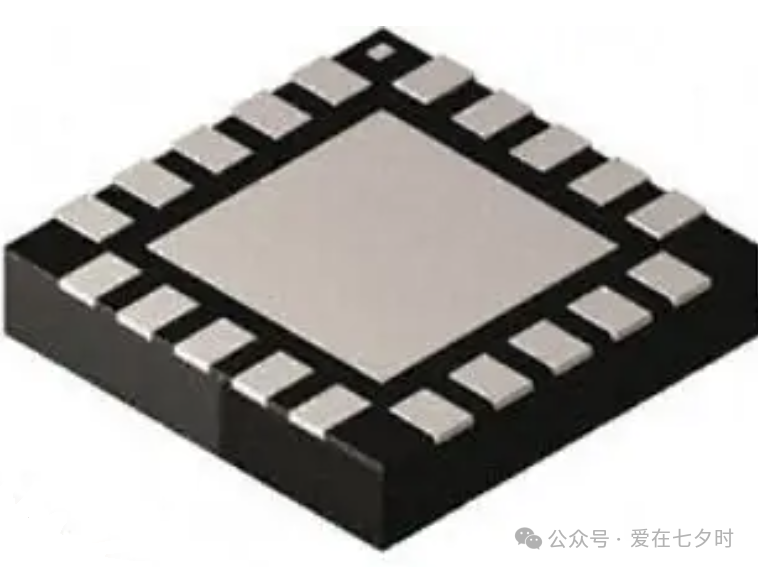

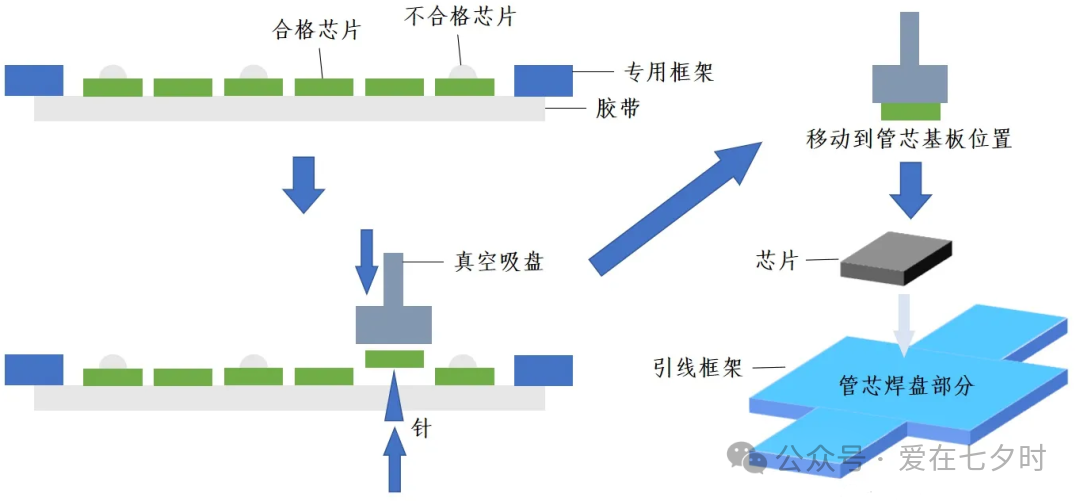

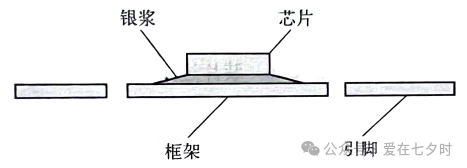

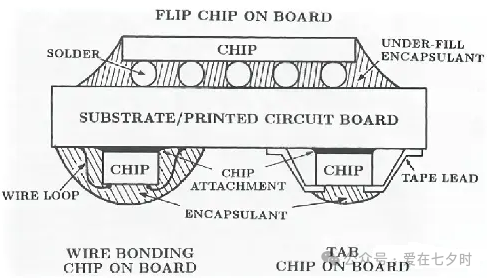

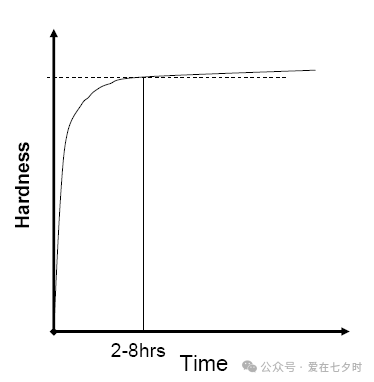

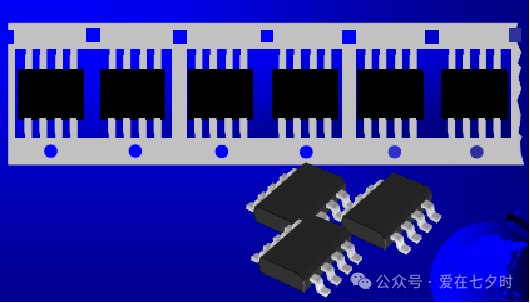

今天主要跟大家分享一下关于半导体芯片设计制造过程中的“封装测试”工序的详细介绍,希望有兴趣的朋友可以多多支持并批评指正!一、芯片CP测试 CP测试在整个芯片制作流程中处于晶圆制造和封装之间。晶圆(Wafer)制作完成之后,成千上万的DIE(未封装的芯片)规则地分布满整个Wafer。 在未进行划片封装的整片Wafer上,通过探针将裸露的芯片与测试机连接,从而进行的芯片测试就是CP测试。测试对象是针对整片wafer中的每一个Die,目的是确保整片wafer中的每一个Die都能基本满足器件的特征或者设计规格书,通常包括电压、电流、时序和功能的验证。它的难点是在于如何在最短的时间内筛掉晶圆中的故障芯片。 CP测试用到的设备有测试机 (IC Tester) 和探针卡(Probe Card),软件方面需要制作Test program。Probe Card包括探针和芯片外围电路。裸DIE规则地布满整个Wafer,无论哪片Wafer,每颗DIE都有固定的位置,芯片管脚的位置也就固定。这些位置坐标和间距等信息在芯片投产前已经确定,制作针卡需要这些参数。探针有钨铜、镀铜或钯等材料,这些探针在强度、导电性、寿命、成本等方面各有特点。  探针卡 整片Wafer的测试结果通常生成一个WaferMap文件,数据生成一个datalog,例如STD文件WaferMap主要包含良率、测试时间、各BIN的错误数和DIE位置,datalog则是具体的测试结果。工程师通过分析这些数据,决定是否进入量产。  WaferMap截图 二、芯片封装的类型与作用 芯片封装指芯片和不同类型的框架以及塑封料形成的不同外形的塑封体。  塑封体内部结构示意 按照封装材料目前主流的封装形式主要有陶瓷封装(Ceramic Package)、金属封装(Metal Package)、塑料封装(Plastic Package)三种。首先是金属封装。作为半导体封装的最原始形式,金属封装具有较高的机械强度和良好的散热性能,同时具备气密性。然而,金属封装的价格较高,而且在外形灵活性上相对较差。  添加图片注释,不超过 140 字(可选) 金属封装其次是塑料封装,这种封装方式具有低成本、轻质和良好的绝缘性能等优点,适于大批量生产,应用范围极广。然而,相对于陶瓷封装和金属封装而言,塑料封装在散热性、耐热性和密封性方面相对较差。  添加图片注释,不超过 140 字(可选) 塑料封装最后,我们来看陶瓷封装。陶瓷封装具有气密性、耐湿性好、机械强度高、热膨胀系数小和热导率高等优点。然而,与其它两种封装方式相比,陶瓷封装的成本较高,同时在工艺自动化和薄型化封装方面的能力相对较弱。  添加图片注释,不超过 140 字(可选) 陶瓷封装在半导体封装方式中,陶瓷封装因其独特的优势而备受关注。陶瓷基板封装具有导热性能优异、热膨胀系数小、高频性能好、热稳定性佳、气密性好、耐湿性强、绝缘性好等优势。这使得陶瓷封装在满足半导体行业对封装材料要求的同时,也为高致密封装提供了强大的支持。 2. 按照安装方式可以分为通孔式(PHT)和表面贴装式(SMT),即通常说的插件和贴片。  PHT和SMT 3. 按照外形可以分为SOT、SOIC、TSSOP、DFN、QFN、QFP、BGA、PGA、CSP等。  QFN封装 对于芯片而言封装主要有保护、支撑、连接、散热等作用。 (1)保护:半导体芯片的生产车间都有非常严格的生产条件控制,恒定的温度、恒定的湿度、严格的空气尘埃颗粒度控制及严格的静电保护措施,裸露的芯片只有在这种严格的环境控制下才不会失效。但是,我们所生活的周围环境完全不可能具备这种条件:低温可能会有-40°C、高温可能会有60°C、湿度可能达到100%;如果是汽车产品其工作温度可能高达120°C以上;还会有各种外界的杂质、静电等等问题会侵扰脆弱的芯片。所以需要封测来更好地保护芯片,为芯片创造一个好的工作环境。 (2)支撑:支撑有两个作用,一是支撑芯片,将芯片固定好便于电路的连接,二是封测完成以后,形成一定的外形以支撑整个器件、使得整个器件不易损坏。 (3)连接:连接的作用是将芯片的电极和外界的电路连通。引脚用于和外界电路连通,金线则将引脚和芯片的电路连接起来。载片台用于承载芯片,环氧树脂粘合剂用于将芯片粘贴在载片台上,引脚用于支撑整个器件,而塑封体则起到固定及保护作用。 (4)散热:增强散热,是考虑到所有半导体产品在工作的时候都会产生热量,而当热量达到一定限度的时候便会影响芯片的正常工作。事实上,封装体的各种材料本身就可以带走一部分热量,当然,对于大多数发热量大的芯片,除了通过封测材料进行降温外,还需要考虑在芯片上额外安装一个金属散热片或风扇以达到更好的散热效果。 (5)可靠性:任何封装都需要形成一定的可靠性, 这是整个封装工艺中最重要的衡量指标。原始的芯片离开特定的生存环境后就会损毁,需要封装。芯片的工作寿命,主要取决于对封装材料和封装工艺的选择。 三、芯片封装的工艺流程 下面开始介绍芯片封装工艺的基本工艺流程,包括硅片减薄、硅片切割、芯片贴装、成型技术、去飞边毛刺、切筋成型、上焊锡打码等工序。其中塑料封装之前的工艺步骤称为前段工艺(FOL),即Front of Line;在成型之后的工艺步骤称为后段工艺(EOL),即End of Line。 前段工艺(FOL)流程 晶圆(Wafer)→ 背面减薄(back grinding)→晶圆安装(Wafer mounting)→ 晶圆切割(Wafer Saw)→ 晶圆清洗(Wafer Wash)→ 第二道光检(2nd Opitical)→ 芯片粘贴(Die Attach)→ 银浆固化(Epoxy Cure)→ 引线焊接(Wire Bond)→第三道光检(3rd Opitical)→ EOL(后段工艺) 简单逐一解释下每一道工序。 背面减薄(back grinding):刚出场的晶圆(wafer)进行背面减薄,达到封装需要的厚度(8miles~10miles)。在背面磨片时,要在正面(Active Area)粘贴胶带来保护电路区域。研磨之后,去除胶带,测量厚度。 晶圆切割(wafer Saw):将晶圆粘贴在蓝膜(Mylar)上,再将晶圆切割成一个个独立的Dice。 晶圆清洗(Wafer Wash):对Dice进行清洗,主要清洗Saw时产生的各种粉尘。 第二道光检(2nd Opitical):主要是针对Wafer Saw之后在显微镜下进行Wafer的外观检查,是否出现废品。(第一道光检是晶圆检测) 芯片粘接(Die Attach):简称装片、黏晶,就是把芯片装配到管壳底座或引线架上去芯片装片。黏晶的目的是将一颗颗分离的晶粒放置在引线架上并用银胶黏着固定。引线架是提供给晶粒一个黏着的位置 (晶粒座),并预设可延伸集成电路晶粒电路的延伸脚 (分为内引脚及外引脚)。  芯片粘贴流程 粘贴完成后的芯片和框架如下图所示。  芯片粘贴示意图 银浆固化(Epoxy Cure):175℃,1小时;N2环境防止氧化。银浆(Epoxy)成分为环氧树脂填充金属粉末(Ag),作用主要是将Die固定在Die Pad上、散热以及导电。 引线键合(Wire Bond):利用高纯度的金线、铜线或铝线把Pad和Lead通过焊接的方法连接起来。Pad是芯片上电路的外接点,Lead是Lead Frame上的连接点。芯片互连常见的方法除了引线键合,还有载带自动键合(TAB)和倒装芯片键合(FCB)。载带自动键合(TAB)是指将芯片焊区与电子封装外壳的I/O或基板上的金属布线焊区用具有引线图形金属箔丝连接的技术工艺。倒装芯片键合(FCB)则是指芯片面朝下,芯片焊区与基板焊区直接互连的一种方法。  三种芯片互连方法 第三道光检(3rd Opitical):贴片/引线键合检测 后段工艺(EOL)流程 注塑(Molding)→ 极光打字(Laser Mark)→ 高温固化(PMC)→ 去溢料(De-flash)→ 电镀(Plating)→ 电镀退火(Annealing)→ 切筋&成型(Trim&Form)→ 第四道 光检(4th Opitical) 简单逐一解释下每道工序。 注塑(Molding):防止外部冲击,用EMC(塑封料)把产品封装起来,同时加热硬化。  Mold前后对比 激光打字(Laser Mark):在产品上刻上相应的内容,例如产品名称、生产日期、批次等等。 高温固化(PMC):Post Mode Cure,用于Mold后塑料的固化,保护IC内部结构,消除内部应力。Cure temp:175±5℃,Cure time: 8hrs。  添加图片注释,不超过 140 字(可选) 去溢料(De-flash):目的是去除Molding后在管体周围Lead之间多余的溢料。方法是弱酸浸泡,高压水冲洗。 电镀(Plating):利用金属和化学的方法在Leadframe的表面镀上一层镀层,以防止外界环境潮湿和热的影响。同时提高导电性能,增强可焊接性。一般有无铅电镀和有铅电镀,前者采用99.95%以上的高纯度的锡,为目前普遍采用的技术;后者使用铅锡合金,锡占85%,铅占15%,由于不符合RoHS,目前基本被淘汰。 电镀退火(Annealing):目的是让无铅电镀后的产品在高温下烘烤一段时间(150+/-5C,2hrs),消除电镀层潜在的晶须生长的问题。 切筋&成型(Trim&Form): Trim,将一条片的Lead Frame切割成单个的Unit(IC)的过程;Form,对Trim后的IC产品进行引脚成型,达到工艺要求的形状,并放置进Tube或Tray盘中。  Trim示意图 第四道光检(4th Opitical):Final Visual Inspection。在低倍放大镜下对产品外观进行检查。主要针对EOL工艺可能产生的废品,例如Molding缺陷,电镀缺陷和Trim&Form缺陷等。 四、芯片FT测试 FT测试则是芯片出厂前的最后一道拦截,测试对象是针对封装好的chip。与CP测试的区别在于:受测试治具比如探针的限制,CP测试通常用于基本的连接测试和低速数字电路以及其他一些容易测试或者必须测试的项目。FT阶段则是需要严格精细全面地测试芯片的性能,它的难点是如何在最短的时间内保证出厂的Unit能够完成全部的功能且满足设计规格。FT测试一般是通过自动测试设备(ATE)+机械臂(Handler)+仪器仪表来完成,同时需要制作的硬件有测试板(LoadBoard)和测试插座(Socket)。 |