|

在芯片测试中,Continuity(连通性)测试是一个非常基础但至关重要的测试项,通常被归入Bin 1~Bin 4 或特殊Bin位。它的目的是验证芯片各个引脚或接点之间是否存在开路(open)或短路(short)等硬件层面的问题。 Continuity 测试是什么?Continuity Test(连通性测试)主要是在晶圆级(CP,Chip Probing)和成品级(FT,Final Test)对芯片的 引脚(Pin)、Pad、电源网络等进行通断检查,确认: 是否每个引脚都已正确连接; 是否存在不应该连通的短路; 是否存在焊线失败、Pad损伤、Bonding不良等问题。 测试内容详解:

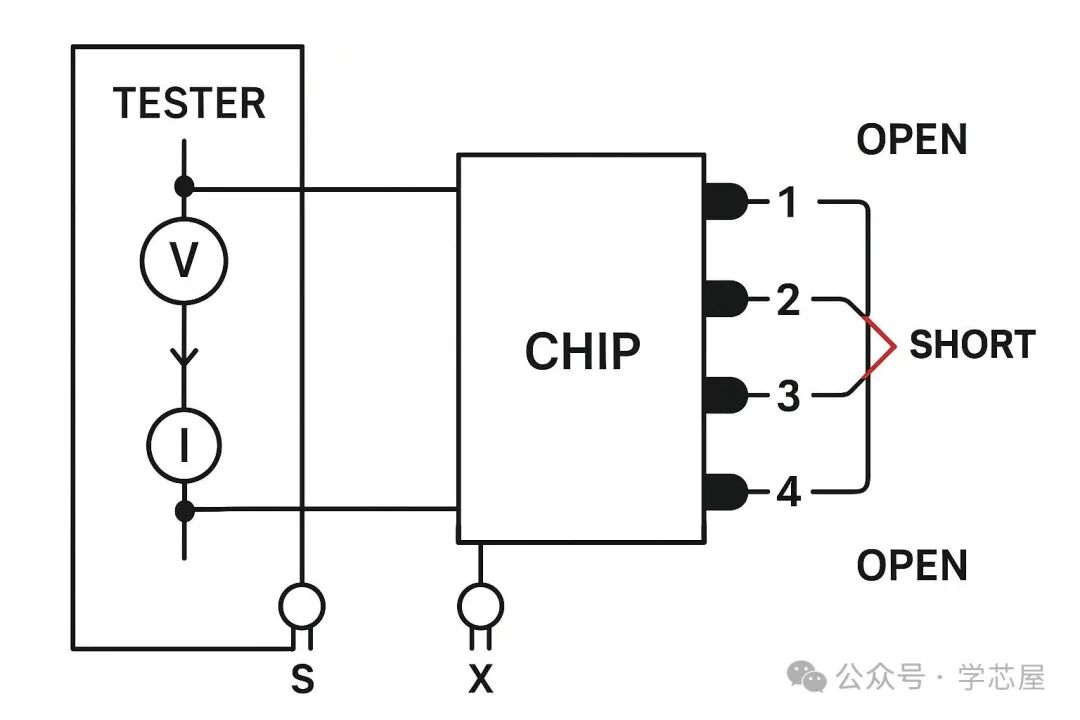

测试方式电压激励 + 电流检测: - 测试仪向芯片某个引脚施加小电压(通常几十 mV 到几百 mV); - 测量该引脚流过的电流; - 若电流太小,说明开路;若电流异常大,可能是短路。 两点之间导通性测试(Two-point continuity test): - 用两针同时触碰不同的Pad; - 测试它们之间的阻抗是否符合预期。 为什么 Continuity 测试很重要?保证后续功能测试有效: -如果芯片本身都没有连接好,那么后续的功能测试结果可能是误判为Fail,而不是功能问题。 屏蔽封装或打线问题: -在FT阶段,封装的焊线断裂/接错非常常见; -Continuity测试可以快速发现问题并分Bin。 初筛不良Die: -在CP阶段,Continuity是最快速的良率筛选方法,避免资源浪费。 Fail 原因常见示例

示例图(描述):假设芯片有5个引脚,Continuity测试逐一确认: 引脚1↔芯片内部连通:✔️ 引脚2↔引脚3出现短路:❌ 引脚4无连接:❌ 引脚5正常:✔️  ✅ 总结:Continuity 测试是芯片测试中的硬件基础验证项,确保芯片从物理连接角度上是“可工作的”。它不测功能,但它决定了功能是否能被“测试到”。 |