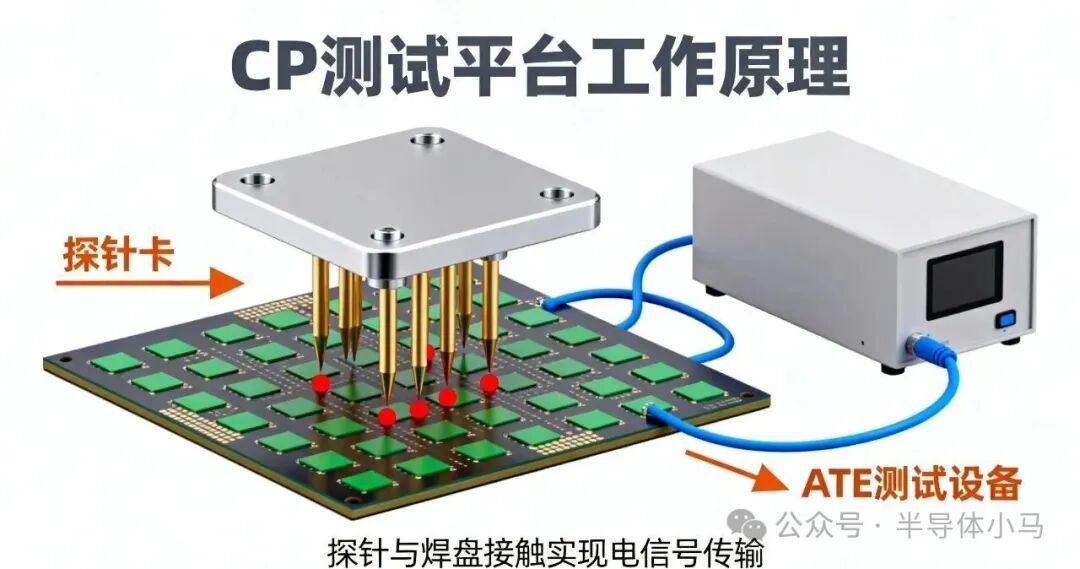

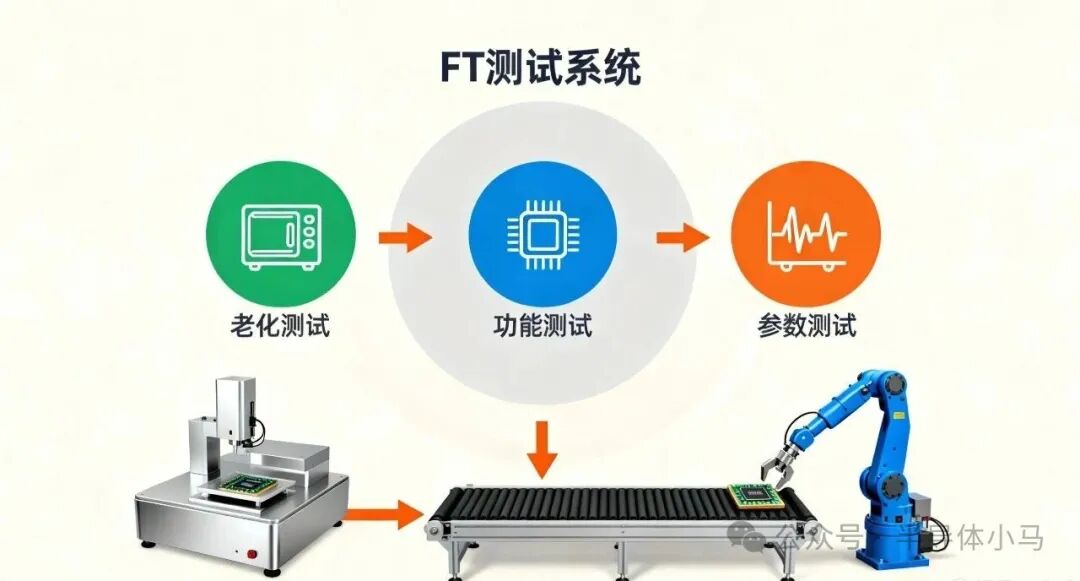

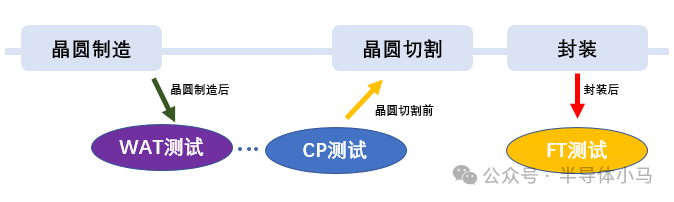

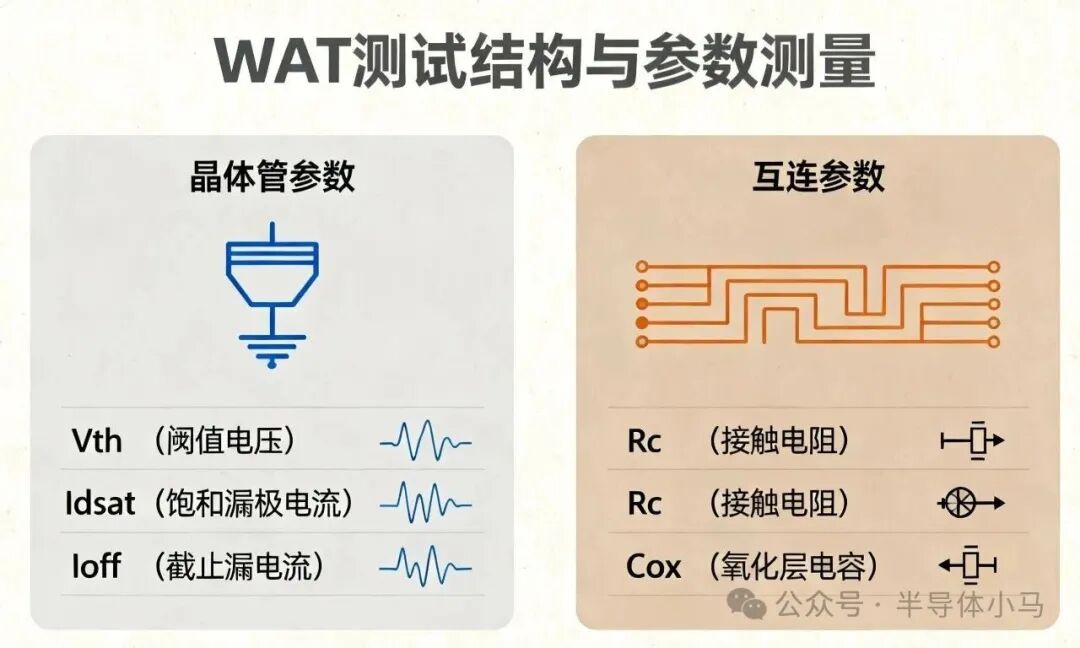

在半导体行业,一颗芯片从设计到量产需要经过数百道工序,而测试环节就像三道严密的质量关卡,守护着每一颗芯片的可靠性。2024年全球半导体测试设备市场规模已达67亿美元,预计2025年将激增30.3%——这个价值数百亿的"隐形战场",正是由WAT、CP和FT三大测试环节构成。今天我们就来揭开这些"芯片质检员"的神秘面纱,看看它们如何联手将良率从50%提升至99.9%。一、芯片测试全流程:三道关卡的协同作战半导体测试绝非简单的"通电检查",而是贯穿芯片制造全流程的质量监控体系。WAT(晶圆接受测试)、CP(芯片探针测试)和FT(最终测试)分别在不同阶段筑起防线,形成"层层筛选、相互印证"的测试网络。  从时间轴看,WAT是晶圆制造完成后的"出厂体检",CP是封装前的"裸片筛选",FT则是封装后的"成品验收"。某Fabless企业案例显示,通过这三道测试的协同,其NOR Flash芯片良率从85%提升至95%,漏电流失效降低82%,直接节省封装成本30%(数据来源:泰治科技YMS系统案例)。 二、WAT:晶圆出厂前的工艺"CT扫描"WAT(Wafer Acceptance Test)就像给晶圆做全身CT,通过检测专门设计在划片槽(Scribe Line)内的"测试键"(Test Key),判断整个晶圆的制造工艺是否稳定。这些测试结构只有微米级别,却能精准反映数百道工艺步骤的质量。 测试结构与参数解析WAT测试结构包含该工艺平台的所有基础器件:MOS晶体管、二极管、电阻、电容以及各种隔离结构。测试参数则涵盖: 晶体管特性:阈值电压(Vth)、饱和电流(Idsat)、漏电流(Ioff) 互连质量:接触电阻(Rc)、互连线电阻(Rwire)、介电层电容(Cox) 工艺监控:薄层电阻(Rs)、氧化层厚度(Tox)  以阈值电压Vth为例,其计算公式为: Vth = Vt0 + γ(2φf – Vt0) 其中, Vt0是零偏电压, γ是斜率系数, φf是费米势, 它们均是与材料本身有关的参数。 详情可参考此前系列文章:半导体制造WAT测试是什么?MOS器件电性参数Vt详解MOS器件中饱和漏极电流Idsat详解MOS器件关态漏电流IDoff详解MOS器件摆幅(Swing)详解MOS器件衬底偏置效应(Body Effect)详解MOS器件漏致势垒降低(DIBL)详解MOS器件中的Isub详解MOS器件中的Ig详解☞下载地址:https://t.zsxq.com/fxbmg

|

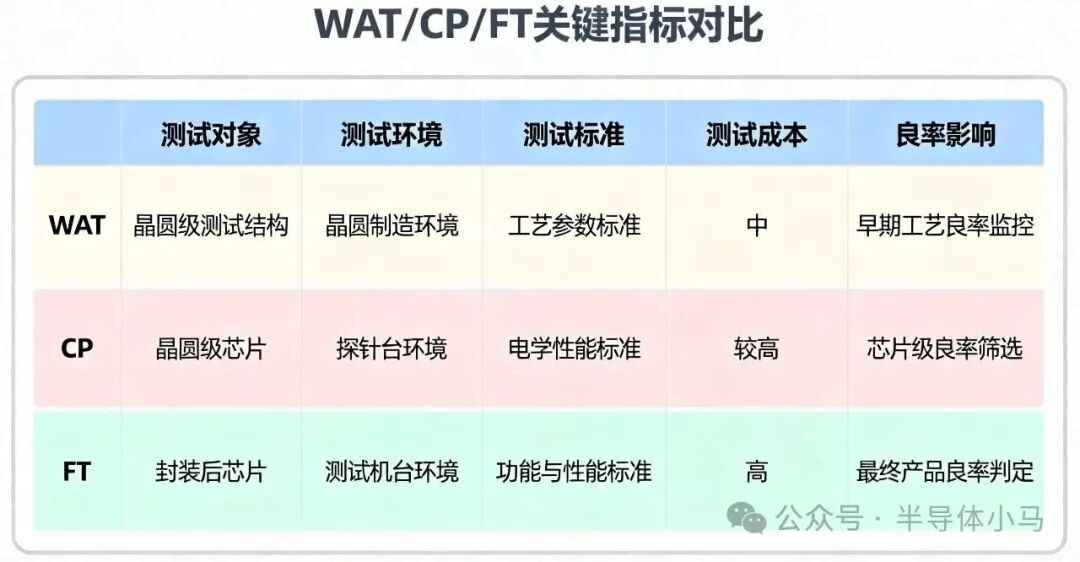

| 对比维度 | WAT测试 | CP测试 | FT测试 |

| 测试对象 | 划片槽内测试结构 | 晶圆上的裸芯片 | 封装完成的成品芯片 |

| 测试环境 | 常温,洁净室Class 100 | 常温为主,部分高低温 | -55℃~175℃,湿度控制 |

| 测试设备 | 参数测试机+探针台 | 功能测试机+精密探针卡 | ATE系统+Handler+温控单元 |

| 成本占比 | 约5% | 约20% | 约35% |

| 良率影响 | 反映工艺良率潜力 | 决定封装芯片数量 | 最终出货质量把关 |

| 标准依据 | SEMI G32/JEDEC JESD47 | JEDEC JESD22 | JEDEC JESD47/ AEC-Q系列 |

从成本结构看,FT测试最为昂贵。某车规MCU厂商数据显示,其FT测试成本占总制造成本的35%,主要源于复杂的环境测试和长测试时间(来源:《半导体测试成本分析报告》)。

六、测试环节对产业的战略意义

芯片测试绝非简单的"质量检查",而是贯穿整个产业链的价值创造过程。对Fabless企业,测试数据是良率提升的关键。通过整合WAT、CP和FT数据,某公司发现WAT中的某个阻值参数与CP漏电流(Iddq)失效强相关,追溯到金属化工艺窗口偏移,调整后良率提升10%(来源:泰治科技YMS系统案例)。

对设备厂商,测试技术创新永无止境。爱德万测试最新推出的V93000 EXA Scale平台,测试密度提升8倍,功耗降低80%,可支持5nm及以下先进制程测试(来源:Advantest 2025产品发布会)。

在半导体产业迈向3nm及后摩尔时代的今天,测试技术正从"被动检测"向"主动良率管理"转变。通过AI算法分析海量测试数据,不仅能预测潜在失效,更能指导工艺优化,实现"从检测到预防"的跨越。正如SEMI标准所言:"测试是半导体产业的眼睛,也是良率的守护神"。

七、结语:看不见的防线,看得见的价值

从WAT的工艺监控,到CP的裸片筛选,再到FT的全面考核,这三道测试关卡构成了芯片质量的"三重防护网"。它们虽然增加了制造成本(通常占总生产成本的20-30%),却能避免有缺陷的芯片流入市场——要知道,一颗失效的汽车芯片可能导致上万美元的召回成本,而医疗设备芯片的失效更关乎生命安全。

随着Chiplet、3D封装等先进技术的普及,测试将面临更复杂的挑战:异质集成芯片的测试访问、高频信号的完整性测试、以及热应力下的可靠性验证。但正是这些挑战,推动着半导体产业不断创新,最终为我们带来更强大、更可靠的芯片产品。

下一次当你使用智能手机或驾驶新能源汽车时,不妨想想那些看不见的测试环节——正是这些"芯片质检员"的默默守护,让我们的数字生活得以可靠运行。

碳中和要求,共同支撑半导体产业向更高集成度、更低功耗、更可持续的方向发展。