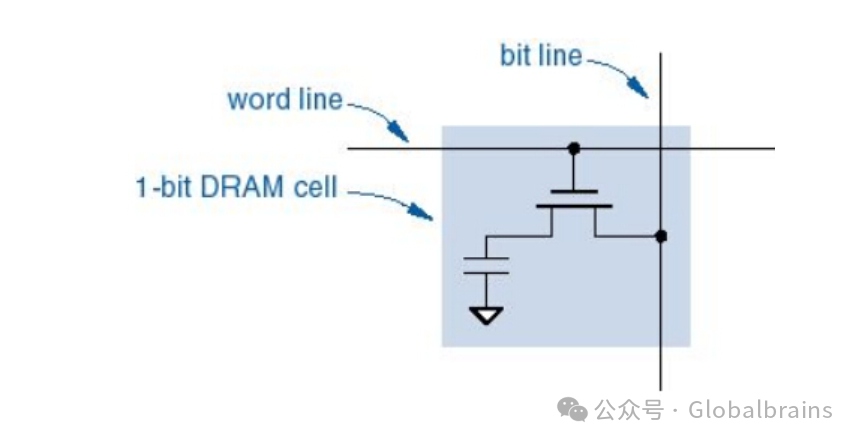

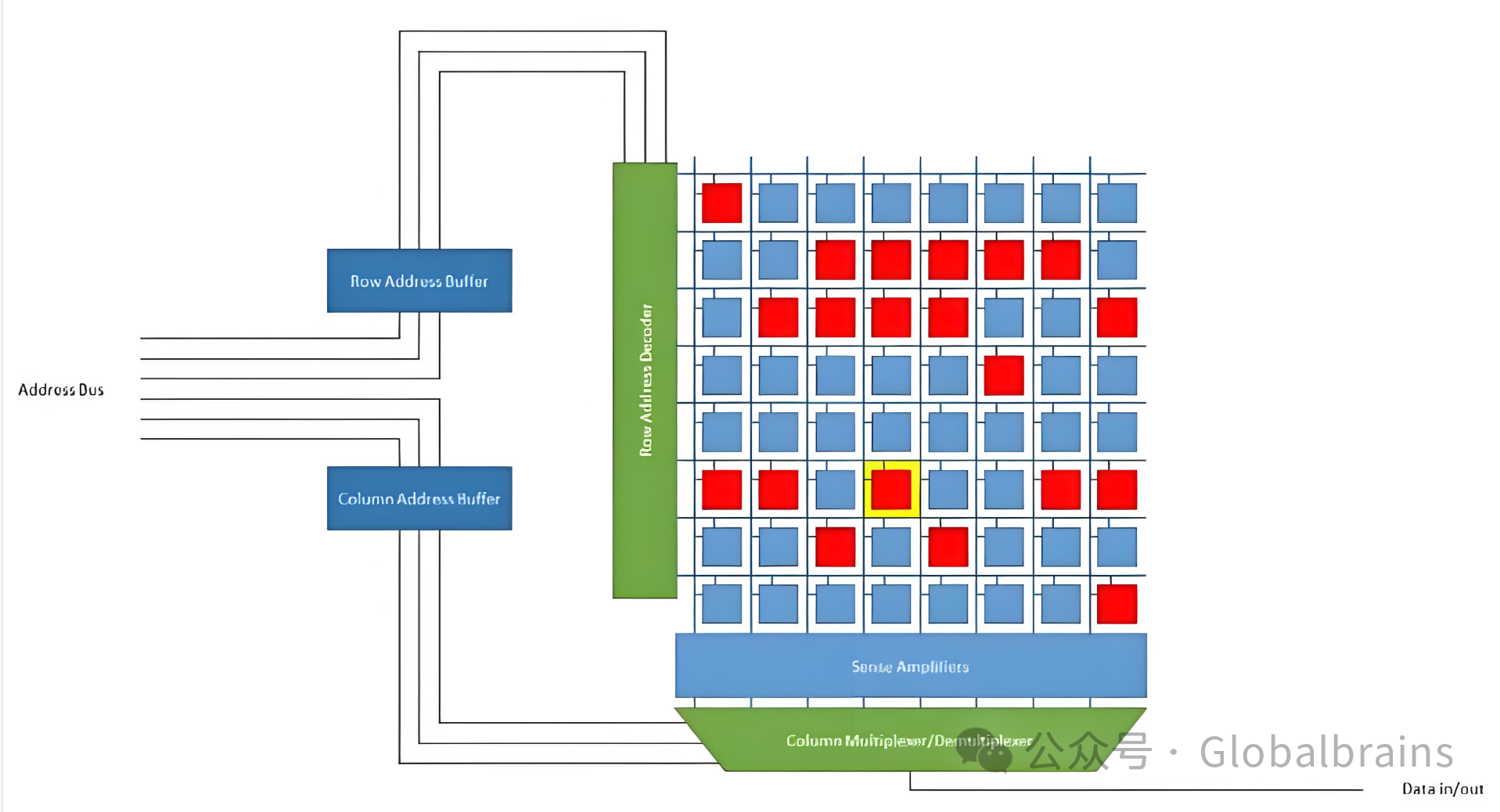

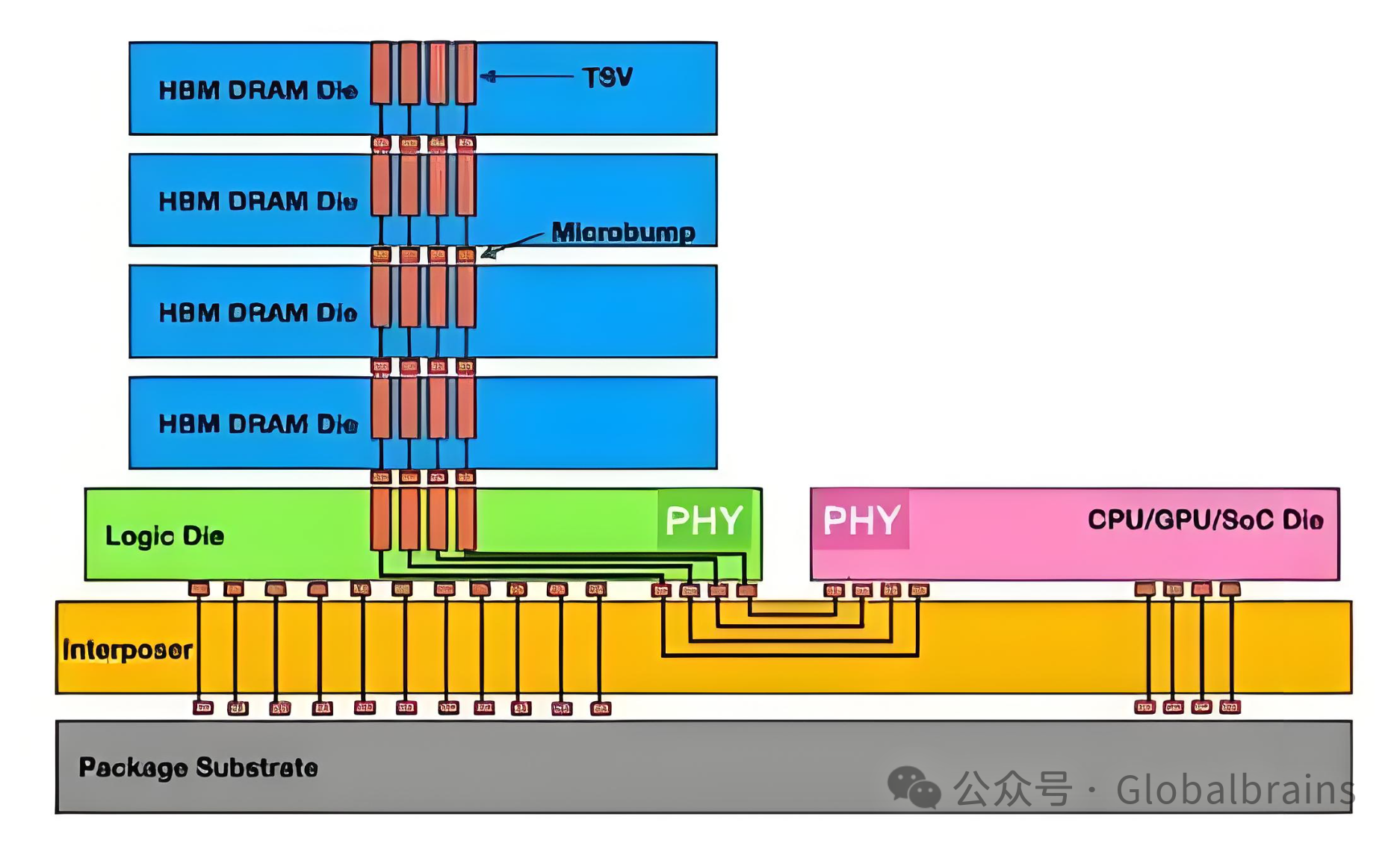

一、存储单元(Cell)结构基础组成 DRAM的最小存储单元由1个晶体管(MOSFET)和1个电容构成。 电容 :存储电荷,电荷状态代表数据(有电荷为“1”,无电荷为“0”)。 晶体管 :作为开关,控制电容与位线/字线的连接。 动态特性 :电容会因漏电逐渐失去电荷,需周期性刷新(一般为64ms)。 物理结构优化 为提升存储密度,电容采用圆柱形设计,晶体管通过纳米级工艺缩小体积。随着制程进步,三维结构(如凹槽栅极、埋入式字线)被引入以缓解漏电问题  二、层级化存储架构DRAM的物理结构从微观到宏观分为多个层级:Cell阵列 :多个存储单元按行列排布,通过位线(BL)和字线(WL)连接。 Bank :多个Cell阵列组成一个Bank,可独立操作 Chip :多个Bank集成于单个芯片中,构成容量更大的存储单元。 Rank与Channel :多个Chip并行组成Rank,多个Rank通过内存通道(Channel)与控制器交互  三、读写操作原理写操作 · 字线激活对应行的晶体管,允许数据线对电容充电(写“1”)或放电(写“0”)。 · 电容充电完成后,晶体管关闭以保持电荷。 读操作 · 字线激活后,电容通过位线放电,电荷变化被读出放大器检测并转换为逻辑信号。 · 破坏性读取:读操作会耗尽电容电荷,需通过放大器重写数据以维持存储。 四、动态刷新机制刷新必要性 电容的自然漏电会导致数据丢失,需周期性刷新(例如每64ms对全部行刷新一次)。 刷新方式 · 自动刷新(Auto-Refresh) :由DRAM内部控制器执行,无需外部干预。 刷新周期 :刷新操作占用存储带宽,影响系统性能。 五、DRAM的演变与类型技术迭代 · 从SDRAM(同步DRAM)到DDR系列(双倍数据速率),速度从66Mbps提升至DDR4的3200Mbps · 电压逐步降低(如DDR4为1.2V),功耗优化显著 高密度方案 采用高介电材料(如氮化硅)提升电容效率,三维堆叠技术(如3D DRAM)突破平面限制 六、与SRAM的对比

总结DRAM通过电容和晶体管的组合实现高密度数据存储,依赖周期性刷新维持数据完整性,其层级化结构和工艺演进支撑了内存容量与性能的持续提升。与SRAM相比,DRAM在成本与容量上更具优势,但速度和功耗存在短板 |