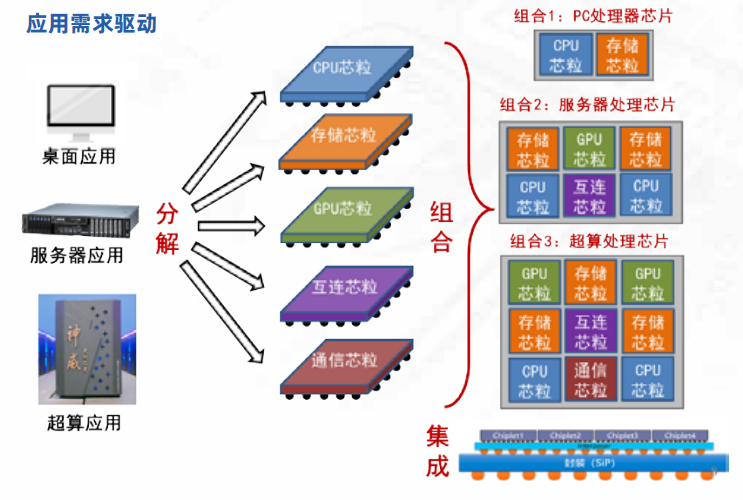

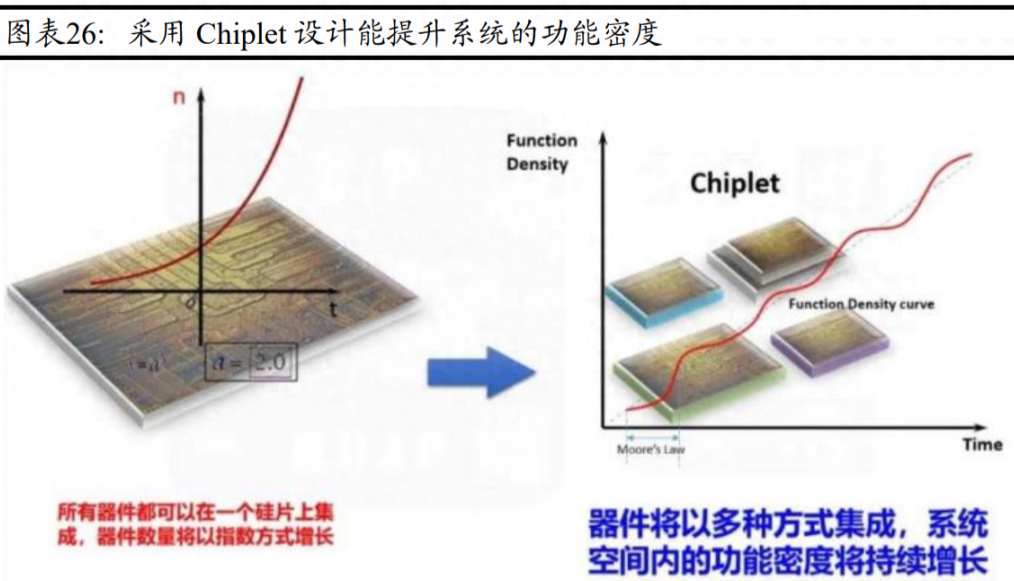

本文约12,000字,建议收藏阅读 随着信息技术的飞速发展,集成芯片和芯粒技术正在引领半导体领域的创新。集成芯片技术通过缩小元器件尺寸和提高集成度,实现了电子产品的微型化和高效能化。与此同时,芯粒技术通过先进的封装工艺,将多个功能芯片紧密集成成系统级封装(SiP),进一步提升了系统的集成度和整体性能。这两者共同推动电子产品朝着更高性能、更低功耗和更小体积的方向不断演进。  #01 引 言 1.1 集成芯片与芯粒技术的背景和重要性 随着半导体技术的发展,电子设备的功能和性能要求不断提升。传统单片集成电路(IC)在电子产品小型化和性能提升中发挥了重要作用,但随着摩尔定律的放缓,其扩展能力受到限制。  在此背景下,集成芯片(IC-Integrated Chip)和芯粒技术(Chiplet Technology)应运而生,成为应对现代半导体设计和制造挑战的关键。 集成芯片通过将多个功能模块整合在单一芯片上,优化了设备的尺寸、功耗和性能。而芯粒技术则通过在一个封装内集成不同工艺节点和功能模块的芯粒,提升了系统性能和设计灵活性,并降低了成本。(*2023《集成芯片与芯粒技术白皮书》中的定义为:集成芯片是芯粒级半导体制造集成技术,通过半导体技术将若干芯粒集成在一起,形成新的高性能、 功能丰富的芯片。集成芯片是指先将晶体管集成制造为特定功能的芯粒(Chiplet),再按照应用需求将芯粒通过半导体技术集成制造为芯片。)  1.2 微电子领域的地位和发展趋势 集成芯片和芯粒技术在微电子领域具有重要影响。集成芯片推动了计算机、通信设备和消费电子的快速发展;而芯粒技术通过模块化和异构集成突破了传统集成电路的限制,成为高性能计算和数据中心芯片的趋势。  未来,随着5G、人工智能(AI)、物联网(IoT)等技术的发展,电子设备对芯片性能、功耗和集成度的要求越来越高。集成芯片和芯粒技术的结合将成为满足这些需求的重要手段,并继续引领微电子领域的发展。 未来,随着5G、人工智能(AI)、物联网(IoT)等技术的发展,电子设备对芯片性能、功耗和集成度的要求越来越高。集成芯片和芯粒技术的结合将成为满足这些需求的重要手段,并继续引领微电子领域的发展。 #02 集成芯片技术概述 集成芯片(Integrated Chip)是一个封装内包含一个或多个集成电路(IC)的电子元件。它作为一个整体组件,提供了将多种功能模块集成在一起的能力。这一术语强调的是实际的芯片组件及其在封装中的实现,而不仅仅是电路本身。  2.1 集成芯片和集成电路的差异 集成芯片(Integrated Chip)和集成电路(Integrated Circuit, IC)虽然相关,但并不完全相同。集成电路(Integrated Circuit, IC)是一种将多个电子元件集成在一块半导体基板上的微型化装置。集成芯片是实际的芯片组件,它可以包含一个或多个集成电路。以下是它们的区分和关系:

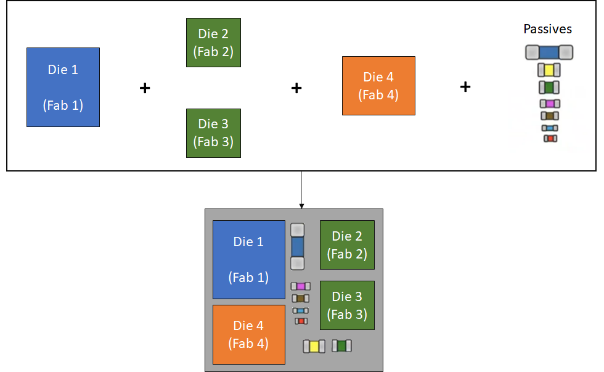

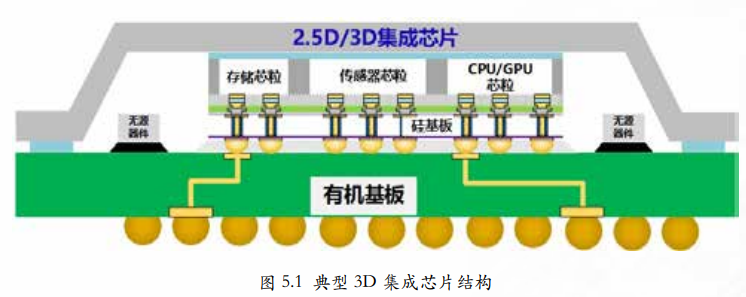

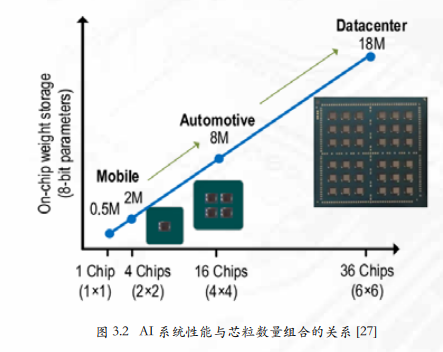

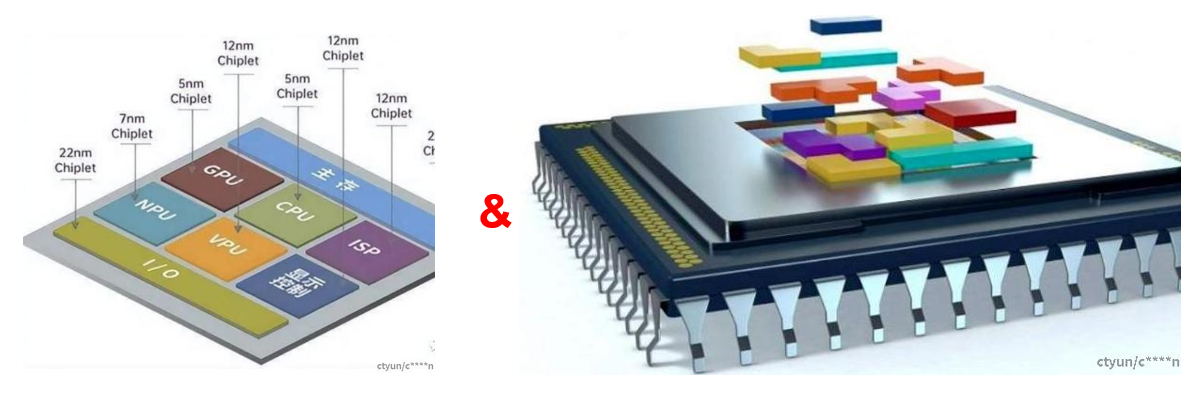

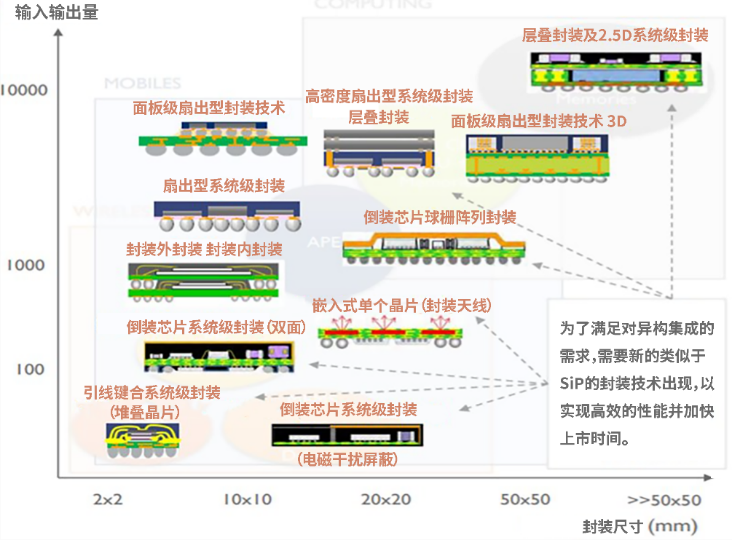

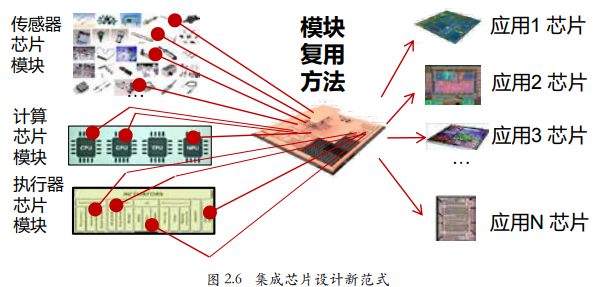

· 集成电路(IC)是构成集成芯片的基础技术,是一个广泛的技术概念。 · 集成芯片可以包括一个或多个集成电路,强调的是实际的芯片组件和封装形式。 · 集成芯片通过在一个封装内集成多个功能模块,以实现以下目的: o 减少物理体积:将传统上分散的电路元件集成在一个芯片上,显著减小了电路的物理体积。 o 提高电路性能:通过内部优化设计和减少信号传输路径,提升了电路的性能和处理速度。 o 提高可靠性:减少了外部连接和焊接点,降低了故障率,增加了整体系统的可靠性。 2.2 技术挑战与未来趋势 技术挑战 1. 设计复杂性 o 多功能集成:在集成芯片设计中,需要将多个功能模块集成到一个封装内,这要求工程师在设计时综合考虑电路兼容性、热管理和功耗控制等问题,增加了设计的复杂性。  o 工艺兼容性:不同功能模块可能采用不同的工艺节点,确保这些模块在同一封装中的兼容性和性能一致性是一个重要挑战。 2. 制造成本 o 高成本:高度集成的芯片涉及复杂的制造工艺和精密的封装技术,导致生产成本较高。降低这些成本而不影响性能和可靠性是关键问题。 o 良率问题:集成芯片中各个功能模块的良率直接影响整个芯片的生产良率。单一模块的缺陷可能会影响整个芯片的质量和生产效率。 未来趋势 1. 技术突破 o 异构集成:未来的集成芯片将更多采用异构集成技术,将不同工艺节点和功能模块有效组合在一个封装中,提升性能和功能,同时降低功耗和成本。  *异构集成是一种先进的半导体设计技术,它允许来自不同制造商和工艺技术的芯片在同一封装内进行集成。这种方法的目的是为了实现更高的性能、更低的功耗和更大的设计灵活性。 o 先进封装技术:如3D封装和2.5D封装技术,将成为集成芯片设计的重要趋势,这些技术能实现更高密度的功能集成和更好的性能。  2. 新兴应用 o 人工智能:集成芯片将在AI计算和机器学习应用中发挥关键作用,尤其在边缘计算和物联网设备中。AI加速器和专用处理器将成为重要的集成芯片类型。  *在不同应用场景下,AI系统的性能与其所需的芯片数量和存储能力之间存在密切关系。随着应用需求的提高,对芯片数量和存储容量的要求也随之提升。 o 量子计算:虽然仍处于研究阶段,量子计算的发展可能引领集成芯片设计的新趋势,包括量子芯片的集成和量子处理器的开发。 3. 标准化与生态系统 o 技术标准化:未来的集成芯片设计将更加依赖标准化的接口和协议,以确保不同模块和系统之间的兼容性和互操作性。集成芯片的高效组合关键在于接口的标准化。2022年3月,由Intel主导的通用高速接口联盟(UCIe)成立,专注于制定芯粒技术的互联标准。与此同时,中国也发布了相关规范,如中国计算机互连技术联盟的《小芯片接口总线技术要求》和中关村高性能芯片互联技术联盟的《芯粒互联接口规范》,以推动国内芯片技术的标准化和兼容性。 o 生态系统建设:集成芯片技术的发展将促进相关产业生态系统的建设,包括设计工具、制造技术和应用平台的全面发展。  #03 芯粒技术详解 3.1 芯粒技术的定义与特征 芯粒技术(Chiplet Technology)是一种将多个具有特定功能的小型芯片(芯粒)通过先进的半导体封装工艺集成在一起的方法,形成一个具有更复杂功能或更高性能的单一封装。这种方法允许不同功能的芯粒在设计和制造上具有更大的灵活性,可以根据不同应用的需求进行选择和组合。  芯粒技术的这种特性使其在现代电子设备制造中扮演了越来越重要的角色,推动了电子技术的进一步发展。

芯粒技术通过其高性能、低功耗和快速开发的特性,展示了在现代电子产品设计中的巨大潜力。随着半导体技术的进步,芯粒技术预计将在未来的芯片设计中发挥关键作用,推动电子设备向小型化、高集成度和高性能发展。 3.2 芯粒技术的结构与设计 芯粒技术(Chiplet Technology)在提升集成度和灵活性方面表现出色。了解芯粒的物理结构和封装形式,以及其设计流程和工具,对于深入掌握这项技术的应用与发展至关重要.  如下,涵盖了芯粒的物理结构和主要封装形式,展示了不同设计方案如何满足性能、功耗和应用需求。 物理结构

*UCIe(Universal Chiplet Interconnect Express) 是一个由Intel主导成立的标准化组织,旨在制定芯粒技术的互联标准。提升芯粒技术的整体性能和系统集成度,推动半导体行业向更高效、更灵活的方向发展。 封装形式

3.3 设计流程和工具 芯粒的设计流程与传统集成电路设计有显著区别,因为芯粒技术涉及多个芯片的集成和互连,需要考虑封装、信号完整性、热管理等多方面因素。以下是芯粒技术的主要设计流程和工具: 设计流程:

设计工具:

3.4 芯粒的制造工艺 芯粒技术(Chiplet Technology)在电子产品的性能和功能集成方面提供了巨大的优势。其制造工艺较传统集成电路更加复杂,因为它不仅涉及到芯片本身的制造,还包括多个芯片组件之间的互连、封装和测试等过程。以下内容将深入探讨芯粒技术的生产流程和关键技术。

综上所述,芯粒技术的制造工艺从晶圆制造到封装测试,涉及多项关键技术和复杂流程。通过不断优化互连、封装和测试技术,芯粒技术能够在未来进一步提高芯片集成度和性能,为微电子领域的持续创新提供强大支撑。 芯粒技术凭借其高度的集成能力、优异的功耗控制、显著的成本优势以及灵活的定制化和可扩展性,展现出广阔的应用前景和发展潜力。随着技术的不断进步和市场需求的持续增长,芯粒技术将在未来的电子产品领域中发挥越来越重要的作用,为下一代电子设备的创新提供强有力的技术支持。 3.5 应用场景与实际效果 芯粒技术凭借其高效的异构集成和灵活的模块化设计,已经在多个领域得到了广泛应用,并取得了显著的实际效果。以下是芯粒技术在主要应用场景中的表现及其带来的价值。

综上所述,芯粒技术在消费电子、物联网、汽车电子和航空航天等领域展现了广泛的应用前景和巨大潜力。其模块化设计、高集成度和异构集成能力,为各类电子系统提供了优化的性能、功耗和可靠性解决方案,满足了不同行业的特定需求。 3.6 未来发展趋势与挑战 在未来的发展中,芯粒技术将继续在多个方面推进,面临新的技术挑战和商业化障碍。以下是芯粒技术未来发展的主要趋势和挑战。

综上所述,芯粒技术未来的趋势和挑战在于技术创新、标准化和生态系统建设、成本控制、以及与新兴技术的融合。通过不断突破技术瓶颈、建立健康的产业生态、优化成本结构和探索多技术融合,芯粒技术有望在未来继续发挥其重要作用,推动电子产业的持续创新和发展。 #04 集成芯片与芯粒技术的融合应用 4.1 融合技术的基本原理 融合技术的基本原理是将不同功能和特性的芯片单元(即芯粒)集成到一个封装内,从而在不依赖单一制造工艺节点的前提下,实现更高的性能、更低的功耗和更紧凑的设计。这种方法打破了传统集成电路制造的工艺瓶颈,通过不同工艺节点和架构的灵活组合,充分发挥每个芯粒的特性和优势,实现多功能集成和系统级优化。  芯粒技术的核心要素:

融合技术的优势:

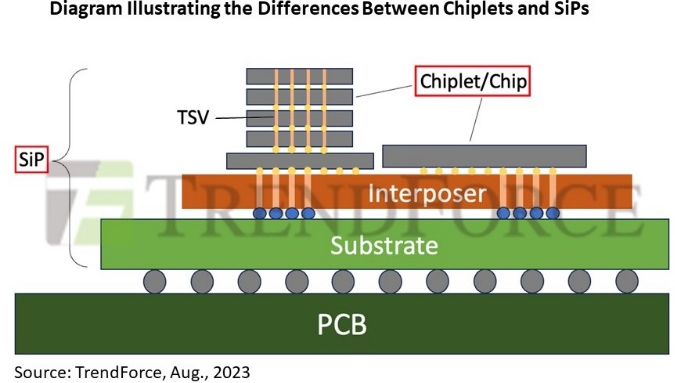

综上所述,集成芯片与芯粒技术的融合应用通过结合异构集成、标准化互连和先进封装技术,实现了性能提升、功耗优化和灵活设计。它不仅在技术上突破了摩尔定律的瓶颈,还为未来电子系统的多功能、高性能和低功耗发展开辟了新路径。这种融合不仅为设计师提供了更多的灵活性,也为最终用户带来了更高效、更智能的电子产品。推动了许多领域的发展,如消费电子、汽车电子、物联网和高性能计算等。 4.2 不同融合方式的比较:系统级封装(SiP) vs 系统级芯片(SoC)中的芯粒应用 系统级封装(SiP)和系统级芯片(SoC)代表了两种不同的芯粒应用方法。系统级封装(SiP)通过将多个芯粒(如处理器、存储器、传感器等)集成在同一封装内,并利用先进的封装技术实现芯片之间的互连和协同工作。这种方法能够在一个封装内部形成一个功能丰富的系统,适合需要高度集成和多功能模块的应用场景。  与此不同,系统级芯片(SoC-system on chip)则将多个功能模块(如CPU、GPU、存储器、I/O接口等)集成在单一芯片上,形成一个完整的系统解决方案。这种集成方式能够在一个芯片上实现全部所需的功能,通常用于对体积、功耗和性能有严格要求的场合。SoC的优势在于其高集成度和优化的系统性能,但其设计和制造的复杂性较高。  系统级封装(SiP)与系统级芯片(SoC)的芯粒应用比较

#05 结 论 集成芯片和芯粒技术的快速发展,已成为半导体行业的核心趋势。芯粒技术通过异构集成和模块化设计,优化了性能和功耗,提升了系统集成度和功能多样性,为突破传统集成电路瓶颈提供了新的解决方案。  这种技术通过在同一封装内集成不同功能的芯粒,实现了性能、功耗和成本的最佳平衡,满足了高性能计算、人工智能和物联网等领域的需求,显著缩短了开发周期,降低了成本,并提升了系统的可扩展性和定制能力。  芯粒技术还推动了半导体行业的转型升级,促进了芯片从单一功能向多功能、可重构系统的演进,推动了电子产品的智能化和多样化发展。 展望未来,芯粒技术将在高性能计算、人工智能、物联网和汽车电子等领域继续引领创新和市场扩展,随着技术的成熟和生态系统的完善,其应用将进一步扩大,推动行业进入新的增长周期。 |

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||