|

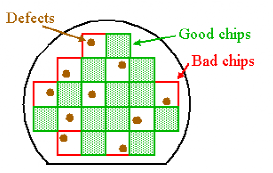

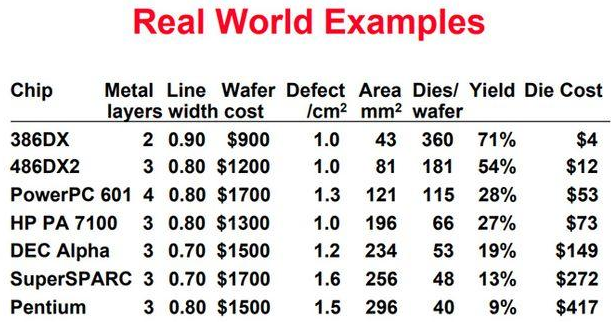

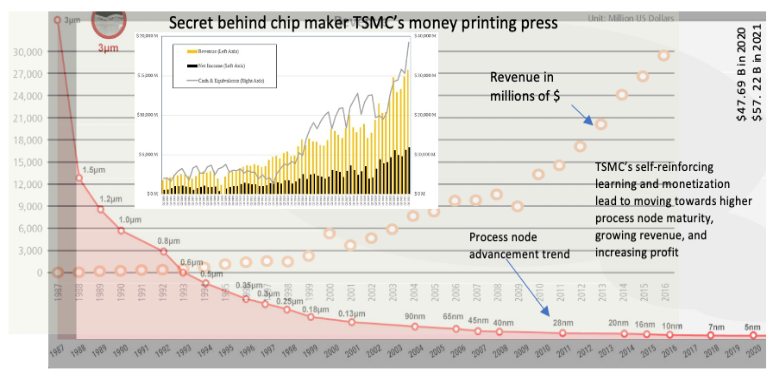

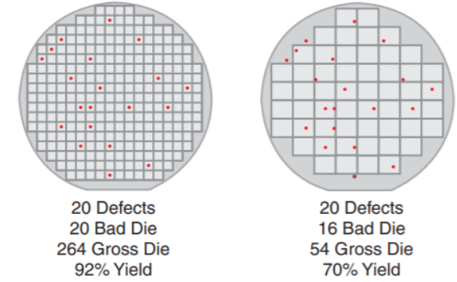

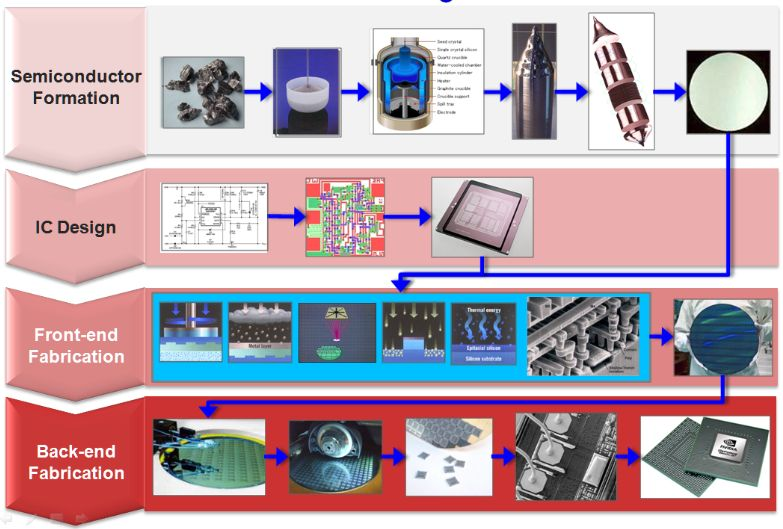

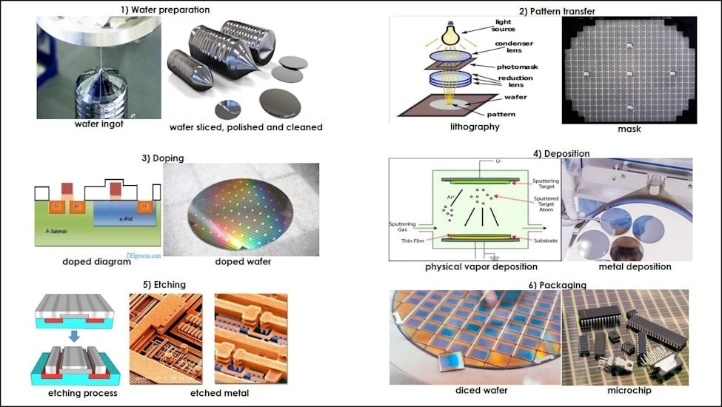

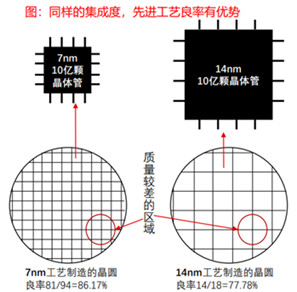

芯片技术与工艺. 分享芯片产业链技术干货  作者 | 北湾南巷 出品 | 芯片技术与工艺 芯片良率(或成品率)是指在芯片制造过程中,从一片晶圆上生产出的芯片中,能正常工作的比例,即合格芯片数量与总芯片数量的比率。良率的高低反映了生产工艺的成熟度、设备的精度和稳定性、材料质量以及设计合理性。  #01良率的背景介绍 1.1 良率在半导体制造中的重要性 1. 生产效率和资源利用:高良率意味着更少的废弃芯片,更高的资源利用率。固定成本的晶圆如果能生产更多合格芯片,就能提升生产效率,减少浪费。  2. 质量和可靠性:高良率通常意味着缺陷较少,芯片质量和可靠性更高,确保电子产品的性能稳定和长寿命,尤其在需要高性能的设备中(如服务器、智能手机、汽车电子)。 3. 工艺改进和创新能力:提高良率体现了制造商在工艺改进和技术创新上的能力,通常伴随着新材料、新设备的应用和新工艺的研发,是技术进步的标志。 1.2 良率对成本与市场竞争的影响 在半导体行业,成本控制是决定企业竞争力的关键,而良率直接影响生产成本。以下是良率对成本和市场竞争力的具体影响: 1. 降低生产成本:低良率意味着需要更多的晶圆和生产时间来制造同样数量的合格芯片,增加材料、人工、能源等成本。高良率则能在相同投入下生产更多合格芯片,降低每个芯片的平均成本,尤其是在昂贵的先进工艺节点上。 2. 提升市场竞争力:高良率降低了生产成本,使制造商能够以更具竞争力的价格出售芯片,同时维持合理利润率。低良率则导致高成本,影响产品定价和市场份额,削弱企业的竞争力和长期生存能力。 3. 加速产品上市:高良率减少了生产过程中的问题,缩短了测试和质量控制时间,提高了生产效率,能更快地响应市场需求和技术变化,加速产品上市。 4. 增强品牌声誉:高良率意味着更高的产品质量和稳定性,赢得客户信任,提升品牌声誉,特别在汽车电子、医疗设备等关键领域,高良率保障了产品的安全性和可靠性。  因此,良率不仅是衡量制造过程效率和质量的关键指标,也是影响企业成本、竞争力和品牌的重要因素,提升良率是所有半导体制造商的核心目标。 #02 芯片良率的基本概念 在半导体制造中,良率(Yield)是衡量制造工艺和质量控制水平的重要指标。它指的是在生产过程中,能够正常工作的合格芯片数量占总生产芯片数量的比率,通常以百分比表示。良率高低直接影响生产效率、成本和产品质量,因此是芯片制造企业的关键关注点。  良率的计算方法可以简单地表示为: 良率=(合格芯片数量/总生产芯片数量)×100% 例如,如果在一片晶圆上制造了1000个芯片,其中950个是合格的,那么良率就是: 良率=(950/1000)×100%=95% 良率通常需要在整个生产过程中进行多个阶段的测量和计算,因为每个生产步骤都有可能引入缺陷,影响最终的良率。 2.1 芯片良率的分类 在芯片制造过程中,良率可以根据不同的阶段和测量方式进行分类,以帮助更精确地分析和优化各个生产环节。  2.1.1 基于制造流程的分类 这种分类方法按照芯片生产过程中不同阶段的良率来划分,重点关注每个阶段的生产效率和产品质量。 · 工艺良率(Process Yield):指在前端制造过程中(如光刻、蚀刻、沉积等)没有出现缺陷的晶圆或芯片的比例。工艺良率反映了前端制造过程的控制和稳定性。 工艺良率(Process Yield)=没有缺陷的晶圆或芯片数量/总制造的晶圆或芯片数量×100%  · 测试良率(Test Yield):指在后端测试阶段通过电学和功能测试的芯片数量与总测试芯片数量的比率。测试良率评估了芯片在后续测试中的表现,反映了芯片的功能完整性和电性能。 · 测试良率(Test Yield)=通过测试的芯片数量/总测试的芯片数量×100% 成品良率(Final Yield):指在所有制造和测试步骤完成后,达到出厂标准并可以投入市场的合格芯片数量与总生产芯片数量的比率。成品良率是对整个制造流程的综合评价,涵盖了从前端制造到后端封装和测试的所有步骤。 成品良率(Final Yield)=合格芯片数量/总生产的芯片数量×100% 2.1.2 基于生产结果的分类 这种分类方法基于良率的具体定义和应用场景,更多地关注最终产品的质量和生产效率。 · 初始良率(First-pass Yield):指一次通过所有制造和测试步骤的合格芯片数量与总生产芯片数量的比率。初始良率不考虑任何返工或重新测试的芯片,是衡量制造过程初次成功率的重要指标。 初始良率(First-pass Yield)=一次通过的合格芯片数量/总生产的芯片数量×100% · 最终良率(Final Yield):指在完成所有必要的返工和重新测试后,最终达到合格标准的芯片数量与总生产芯片数量的比率。最终良率是产品交付前的最后质量控制标准,反映了生产过程中的修正能力。 最终良率(Final Yield)=最终合格的芯片数量/总生产的芯片数量×100% · 各阶段良率(Yield per Stage):指芯片在不同制造阶段(如前端制造和后端封装测试)中通过特定步骤或测试的比例。 各阶段良率(Yield per Stage)=通过该阶段的合格芯片数量/进入该阶段的芯片数量×100% · 例如,前端良率通常指晶圆制造过程中没有重大缺陷的比例,而后端良率则指在封装和最终测试中合格的芯片比例。 前端良率(通常指晶圆制造阶段): 前端良率=没有重大缺陷的晶圆数量/进入前端制造的晶圆数量×100% 后端良率(通常指封装和最终测试阶段): 后端良率=封装和测试合格的芯片数量/进入后端加工的芯片数量×100% 2.1.3 比较与应用场景 · 工艺良率、测试良率和成品良率:这种分类方式适用于对整个制造过程的控制和优化。例如,工艺良率可以帮助识别前端制造过程中的问题,而测试良率则侧重于后端的产品检测和质量控制。 · 初始良率、最终良率和各阶段良率:这种分类方式更侧重于结果的评估和改进,适用于在整个生产过程中进行多次测试和返工的情境。初始良率能够快速反馈生产线的效率,而最终良率则更关注产品交付质量。 通过分析不同阶段的良率数据,制造商可以识别和定位在生产过程中的薄弱环节,采取针对性的优化措施。比如,如果前端制造良率较低,可能需要改进光刻或蚀刻工艺;如果后端封装测试良率低,则可能需要改善封装技术或测试方法。  综上所述,芯片良率不仅是衡量生产效率和产品质量的重要指标,也是优化生产工艺、降低成本和提高市场竞争力的关键因素。理解和提升不同阶段的良率,是实现高效、低成本半导体制造的核心目标之一。 2.2 影响芯片良率的因素及改进方案 芯片良率受到多个因素的影响,包括制造工艺、材料、设备和设计等。这些因素相互作用,共同决定了最终的生产效率和产品质量。理解这些因素有助于识别和解决良率问题,提高半导体制造的整体效率。 2.2.1 制造工艺因素 制造工艺是芯片良率的核心因素,涉及从原材料到成品的每一个加工步骤。以下是几个关键影响因素:

2.2.2 材料因素 材料质量在芯片制造中至关重要,尤其在纳米级工艺中,材料的纯度和均匀性对良率有深远的影响:

2.2.3 设备因素 设备在芯片制造中不可或缺,其性能和稳定性对良率有直接影响:

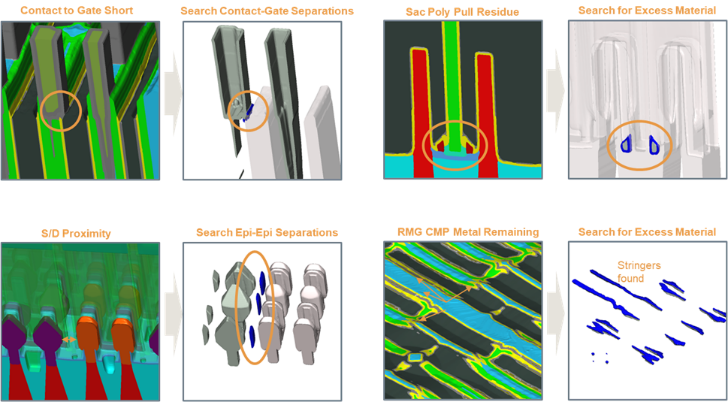

2.2.4 设计因素 芯片设计质量对制造过程中的良率有直接影响。设计不仅决定芯片的功能和性能,还影响制造过程的复杂度和可制造性。

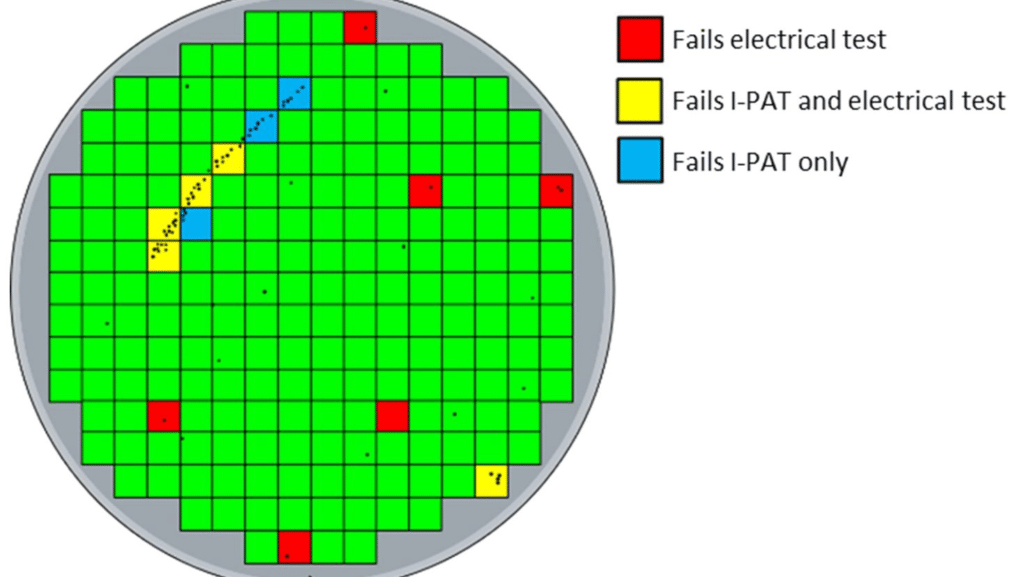

2.3 芯片良率的测量与分析 芯片良率的测量与分析是半导体制造中的关键环节,直接影响生产效率和产品质量。通过科学的测量方法和数据分析工具,制造商能及时发现并解决生产问题,提高良率和整体效率。以下是主要的测量方法和分析工具: 2.3.1 测量方法 良率的测量依赖于精确的测试方法,主要包括电学测试和物理测试。这些方法帮助制造商快速识别和定位芯片中的缺陷和故障。 电学测试 电学测试通过检测芯片的电气性能来判断其是否合格,是最常用的良率测量方法之一,具体包括:

电学测试能够快速准确地发现芯片中的电路缺陷和功能失效,为后续的修复和工艺优化提供数据支持。 物理测试 物理测试通过观察或测量芯片的物理特性来评估其质量,常用的方法包括:

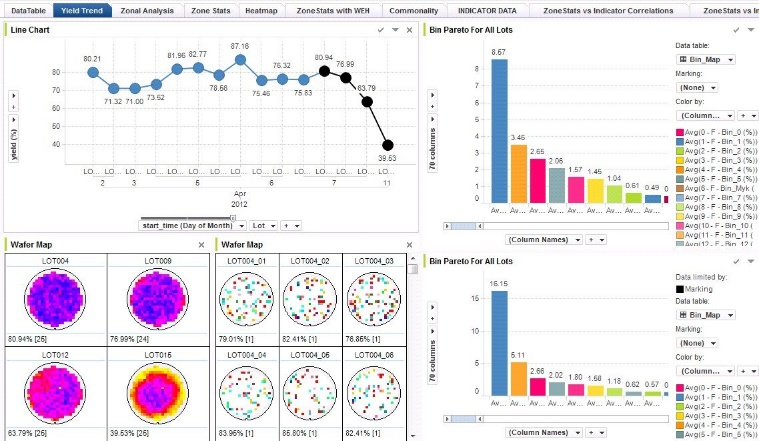

2.3.2 数据分析工具 测量只是芯片良率管理的第一步,接下来通过数据分析工具来识别趋势、找到问题并制定改进措施至关重要。以下是两种常见的数据分析工具: 统计过程控制(SPC) o 用途:利用统计方法监控和控制生产过程的质量。  o 关键工具:

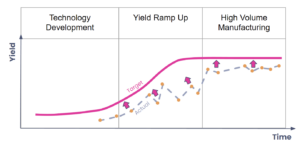

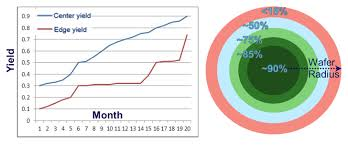

SPC工具帮助制造商持续监控生产过程,识别潜在问题,保持工艺稳定,从而提高芯片良率。 良率曲线(Yield Curve)分析 良率曲线用于反映芯片生产过程中良率的变化趋势,通常显示良率与时间或批次的关系。通过分析良率曲线,制造商可以直观地观察良率的变化情况,识别问题并优化工艺。

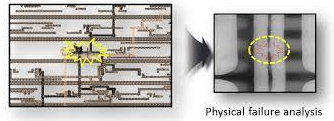

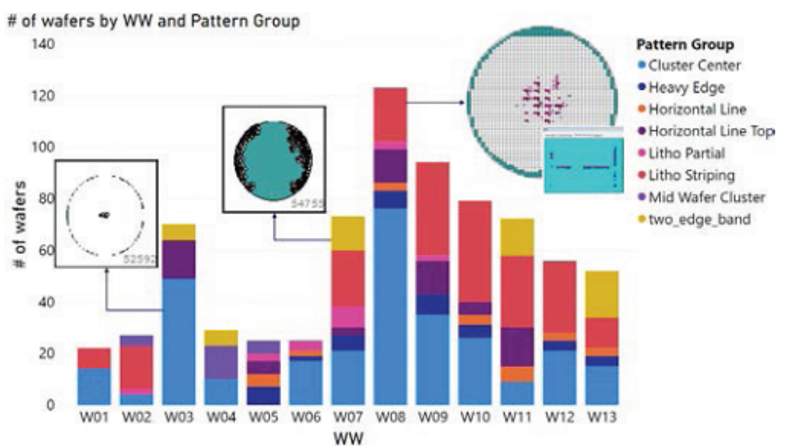

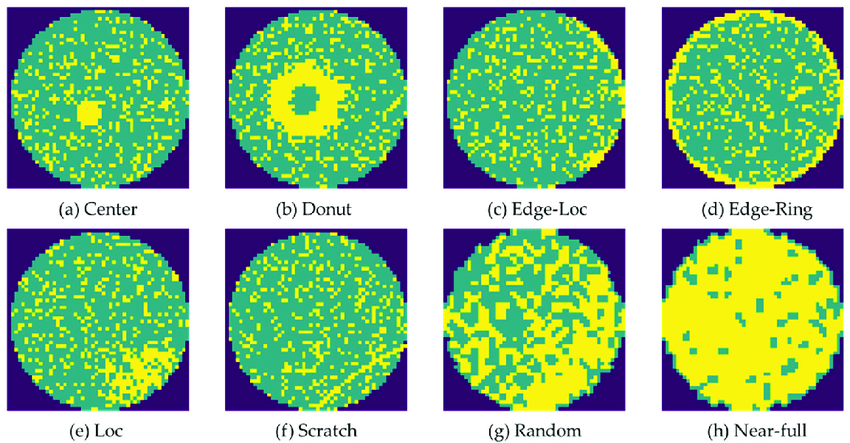

良率曲线分析帮助制造商全面了解生产过程中良率的动态变化,为工艺优化和生产改进提供重要依据。 缺陷密度分布与失效分析 缺陷密度分布是指单位面积上缺陷的数量,通过分析这些分布,可以识别工艺问题和材料缺陷。主要分析方法包括:

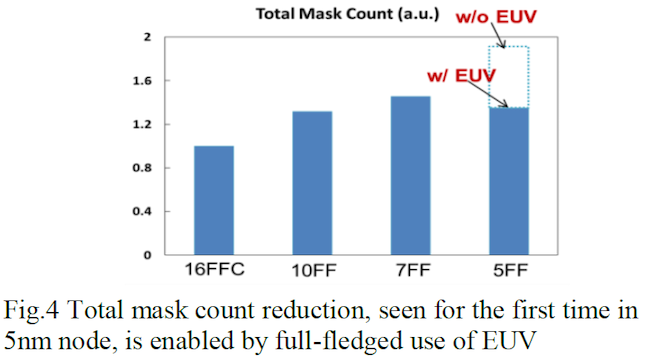

通过分析缺陷密度分布和失效情况,制造商可以深入了解制造过程中的缺陷特征,实施有效的质量控制措施,提高芯片良率,优化生产效率,降低成本,提升市场竞争力。 2.4 先进技术对良率的影响 2.4.1 极紫外光刻(EUV) 极紫外光刻(EUV)是一种使用13.5纳米波长的光来曝光芯片图案的光刻技术。与传统的深紫外(DUV)光刻技术相比,EUV能够实现更高的图形分辨率,是制造高节点芯片(如5纳米及以下)的关键技术。  EUV技术对良率的影响

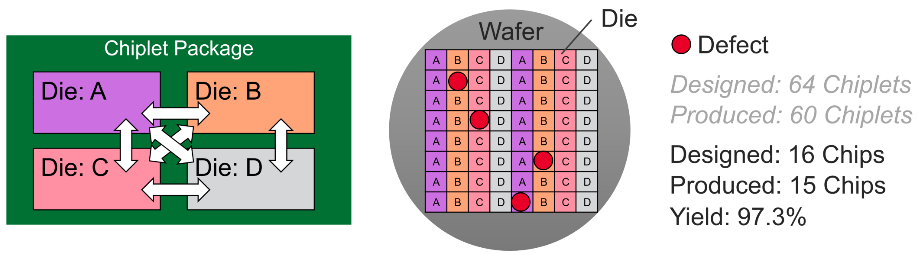

2.4.2 芯粒技术(Chiplet) 芯粒技术(Chiplet)是一种将多个独立制造的芯片模块集成在一个封装中的设计架构。每个芯粒可以是不同功能模块(如CPU、GPU、内存控制器等),通过高速互连技术组合成一个完整的系统级芯片(SoC)。  芯粒技术对良率的影响

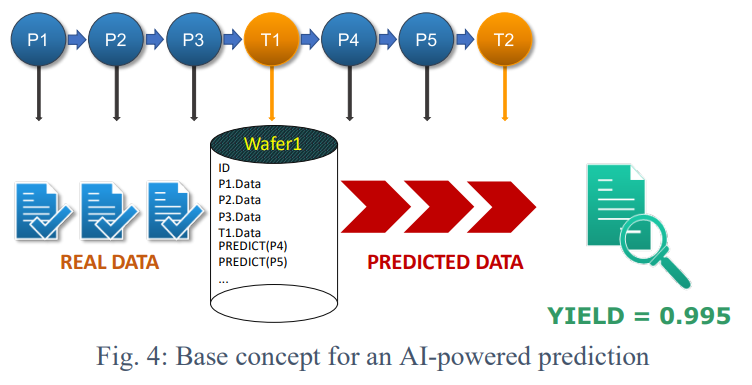

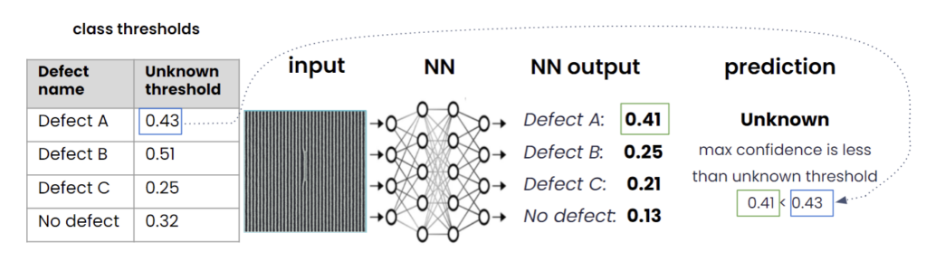

2.4.3 人工智能(AI)与机器学习 人工智能(AI)和机器学习(ML)已经在半导体制造中得到了广泛应用,尤其是在缺陷检测、工艺优化和良率预测等方面。 AI与机器学习对良率的影响

AI与机器学习通过实时缺陷检测、工艺优化、预测性维护和良率预测,大幅提升了芯片制造良率,是现代制造的关键工具。 综上所述,极紫外光刻(EUV)、芯粒技术(Chiplet)以及人工智能(AI)与机器学习等先进技术,通过提高工艺精度、优化设计架构和智能化生产管理,显著提升了芯片的良率。这些技术推动了半导体行业的进步,为未来复杂和高性能芯片的设计与制造奠定了坚实基础。 #03 行业案例分析 在半导体行业中,不同制造商在提高芯片良率方面采用了各种策略,并取得了不同的成果。通过分析成功和挑战案例,我们可以更好地理解良率对企业的影响以及如何应对良率问题。 案例1:某知名芯片厂——先进制程良率提升 背景:某知名芯片厂作为全球半导体制造领导者,以其先进制程和高良率闻名。随着技术节点从7纳米逐步缩小到3纳米,提升良率变得至关重要。 策略与实践: 1. 引入EUV光刻技术:在5纳米制程中,某知名芯片厂广泛采用极紫外光刻(EUV),提高图形精度,减少多重图形化工艺的需求,从而降低光刻误差引发的缺陷。EUV的应用减少了掩模层数,提高了分辨率和制造精度,进而提升了良率。 2. 智能制造与数据分析:通过人工智能和大数据分析,某知名芯片厂实时监控生产线,利用机器学习模型预测缺陷和生产异常,实现预测性维护和工艺优化,减少生产波动和良率损失。  3. 严格的质量控制与持续改进:某知名芯片厂在制造的各阶段实施严苛的质量控制,包括优化CMP、电性测试和缺陷检测,确保每个制程节点的高良率。 结果:通过这些策略,某知名芯片厂在3纳米及更先进节点上保持了高良率,增强了竞争力,满足了市场对高性能、高可靠性芯片的需求。 案例2:某知名芯片厂——10纳米制程良率挑战与克服 背景:某知名芯片厂在推进10纳米制程时面临显著的良率挑战,导致产品发布延迟,影响了公司声誉和财务表现。 挑战与应对: 1. 初期良率问题:某知名芯片厂在10纳米早期生产中遇到光刻对准误差和CMP不均匀性问题,导致晶圆缺陷密度增加,初始良率低。 2. 工艺优化与设备升级:某知名芯片厂通过多次工艺优化,包括重新设计光刻图案、改进CMP工艺、调整蚀刻过程,并引入高精度设备,加强设备控制和校准,减少良率波动。 3. 数据驱动的良率提升:通过强化数据分析,某知名芯片厂识别并改进影响良率的关键因素,实施良率预测模型和SPC,实现实时监控和动态调整。  结果:尽管面临初期挑战,某知名芯片厂通过持续优化和数据驱动的策略,成功提高了10纳米制程的良率,逐步恢复了市场信心。 芯片良率是半导体制造的关键指标,直接关系到企业的成本结构、产品质量和市场地位。通过新材料、新工艺的应用以及智能制造的普及,未来芯片良率将有望进一步提升。与此同时,良率管理将继续面临新的挑战和机遇,推动整个行业向更高效、更智能的方向发展。在这个不断变化和创新的领域,掌握良率管理的核心技术和方法,将是半导体企业保持竞争优势的关键所在。 |

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||