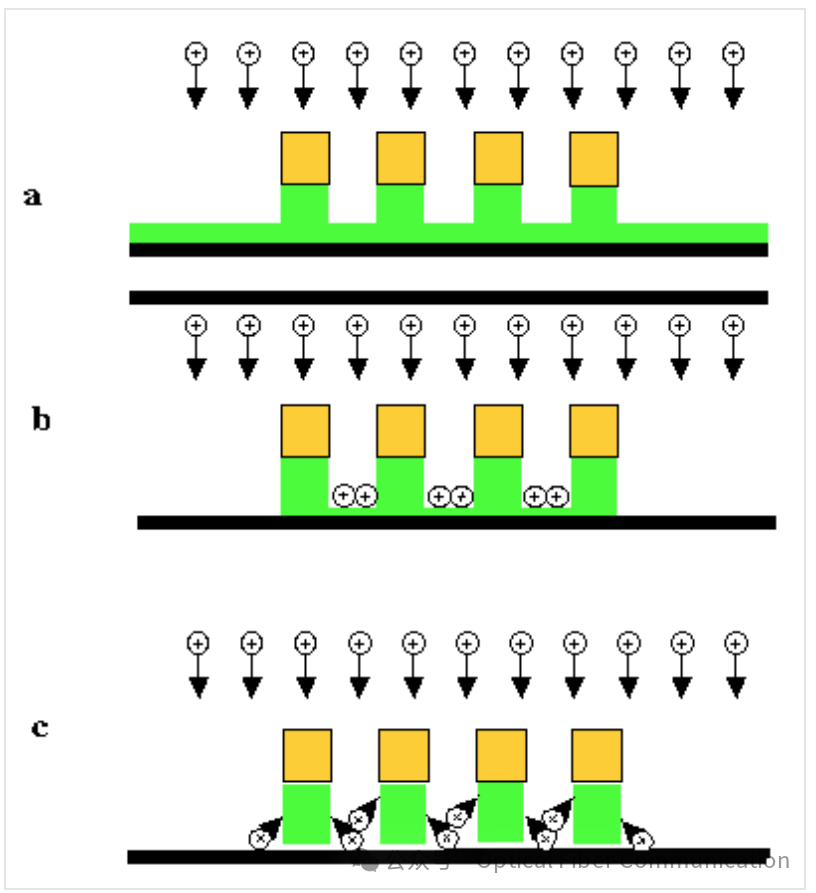

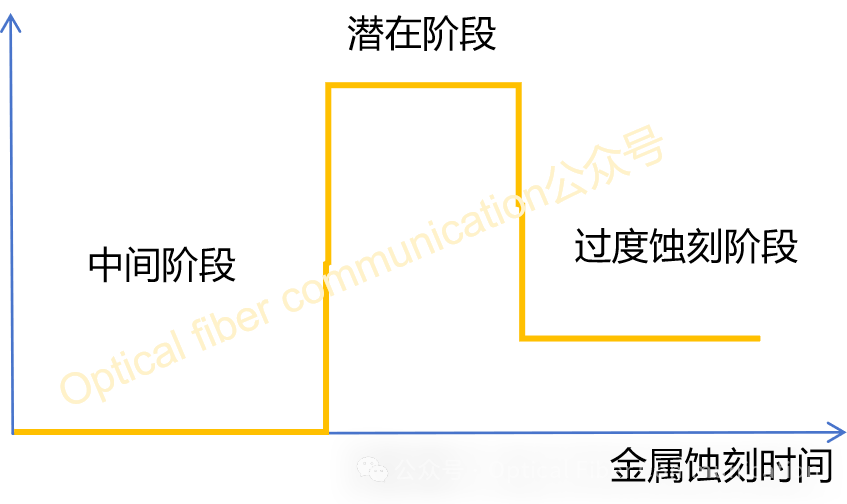

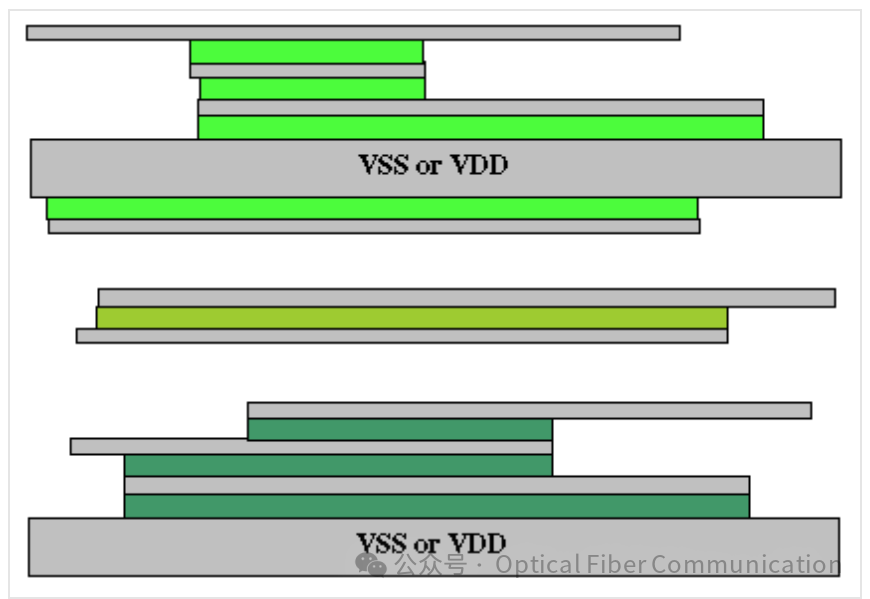

"天线效应"是集成电路在加工过程中孤立节点电荷积累效应的通称。这种效应有时也被称为“等离子体诱导损伤”、“工艺诱导损伤(PID)” 或“充电效应”。在孤立节点通过晶体管的薄栅氧化物放电的情况下,可能会导致晶体管损坏并降低其性能。PID退化效应 在集成电路(IC)的制造过程中,如果电荷在电气隔离节点上积聚,可能会引发一系列问题,这些问题的范围从容易识别的明显故障到更隐蔽、难以检测的问题。 如果积累的电荷能量在栅氧化层的单一点上耗散,这将导致晶体管永久性失效。这是最极端的情况,但大多数时候损害不会以硬故障的形式出现,而是表现为性能下降。这种性能下降可能是由以下任何一种效应引起的: § 栅氧化物漏电流增加; § 晶体管的阈值电压及其变化增加; § 栅氧化物寿命降低; § 晶体管的跨导降低; § 设备产生的噪声增加。 § 热电子效应增加。 虽然这些效应在数字电路中都不受欢迎,但PID对模拟电路的影响更大,可能会导致设备间的额外不匹配、内部噪声增加以及放大和带宽降低。在这种情况下,PID的影响不会仅仅是微小的变化,而是表现为无法满足规格要求的失败。 PID的原因 有几个工艺步骤,在这些步骤中,电荷可以在孤立节点上积累。合理地说,这些步骤都涉及以某种方式用离子淹没晶片表面。在潜在损伤方面占主导地位的步骤是金属和多晶硅的蚀刻,特别是用于铝金属化的蚀刻工艺。这是我们将在本文的其余部分中更详细研究的步骤。但需要注意的是,在金属或多晶硅蚀刻后通过等离子体进行光刻胶灰化、在形成MOS器件时进行离子注入以及在导体上方增强等离子体沉积介质时,也可能发生损伤。 在蚀刻过程之前,整个晶片被一层导电金属覆盖,这使得所有设备短路,因此任何节点上都不会积累电荷。 中间阶段:在离子化粒子蚀刻过程中也是如此(图1a); 潜在阶段:直到蚀刻深入到金属中,使得图案变得孤立,使得每个节点上可以单独积累电荷(图1b),在蚀刻过程的这个阶段,称为“潜在阶段”,狭窄空间被断开,而狭窄空间尚未完全蚀刻掉。在这个阶段,狭窄空间底部的残余金属吸收了大部分离子电流,因此电荷积累速率很高。  图1:金属蚀刻步骤——(a)中间阶段;(b)潜在阶段;(c)过度蚀刻阶段 过度蚀刻阶段:随着蚀刻的进展,狭窄空间的蚀刻完成。现在电荷在金属图案的侧壁上积累(图1c)。在这个阶段,电荷积累速率远低于潜在阶段。 图2显示了简化蚀刻过程中电荷积累速率与时间的关系。  图 2:金属蚀刻过程中的电荷积累速率 实际上,蚀刻过程更为复杂,包括在蚀刻过程中用电子淹没晶片表面。电子淹没应该中和蚀刻中使用的正电荷离子,从而减少电荷的总积累。然而,在潜在阶段,狭窄空间存在“遮蔽”效应,降低了电子淹没的有效性。因此,这些狭窄空间中仍然有电荷积累。 PID相关的设计规则 为了防止这种残余积累损坏电路,IC制造商定义了几种类型的设计规则。最常见的规则称为“天线比”。这条规则适用于连接到晶体管栅的任何金属图案。它为金属的面积(或周边长度)与金属连接的栅氧化物面积之间的比例设定了限制。如果有一个二极管连接到该节点,则对天线比的限制会放宽。这条规则倾向于限制可能对受害者栅氧化物造成压力的电荷量。目前使用的大多数EDA工具,用于检查拓扑设计规则,也可以检查天线比规则。 然而,关于这些规则的有效性存在相当大的疑问。一些领先的制造商已经进行了PID实验,并在类似图3中描述的结构上进行了测量。  图 3:用于监测 PID 的三种拓扑结构,它们具有相似的灵敏度 模式3a的形状像梳子,其手指之间有狭窄的空间——产生大的面积和周边长度用于天线效应。它连接到MOS晶体管的小栅结构。在模式3b中,梳子的手指被分开,导致“天线比”要小得多。在模式3c中,梳子结构完全与受害者晶体管分离,有狭窄的金属间隙和最小空间。同样,计算出的天线比会非常小,因为几乎没有东西直接连接到栅上。 但实际测量显示,这些结构之间的PID差异非常小,尽管在“天线比”之间存在数量级的差异。 这种现象的原因可能与金属蚀刻的“潜在阶段”期间的“遮蔽”效应有关。在蚀刻的后期阶段,模式3b和3c中金属岛之间的狭窄空间就像保险丝。也就是说,它们保持导电桥接,积累电荷,并且只有在潜在阶段结束时才断开,此时已经积累了大部分电荷。 因此,即使这些金属结构在蚀刻过程结束时彼此隔离和从栅上分离,但在天线规则分析期间将它们视为隔离是不正确的。实验表明,现有的设计规则没有考虑到那些由宽阔空间与其他模式分离的相邻模式簇的情况。 对设计的影响 图4展示了任何自动布线软件都可以生成的常见模式,其中金属导体在同一布线方向上随机放置。  图 4:应用于计算“潜在天线比”的阴影空间簇的描述 其中,灰色线条是金属图案,绿色线条是在金属蚀刻的潜在阶段被遮蔽的狭窄空间。这样的遮蔽区域集群可以由一组专门的DRC(设计规则检查)命令选择。这些结构的有效天线分析面积是每个集群的所有遮蔽区域的总和,有效的栅面积是连接到该集群的所有栅的总和。如果这些集群连接到任何二极管,也应该考虑它们。新的“潜在天线比”是遮蔽空间与每个集群的栅面积总和之间的比例。这个比例比普通的天线比更好地代表了实际情况。 在天线效应规则检查中真的需要包括这个级别的估计吗?不幸的是,不仅仅是这里引用的实验,还有实际的设计经验表明,这是必要的。天线效应已经导致一些新产品开发的失败,包括一些领先的IC供应商的设计。其中一些失败影响了通过现有设计规则检查的所有产品。事实上,由于潜在效应导致的失败概率很低,但芯片越大,风险越高。此外,为什么我们要冒可以避免的风险呢? 事实上,有理由相信,随着我们转向更密集和更高频率的电路,问题会变得更糟。可能加剧潜在效应的一个具体实现是添加与噪声敏感信号平行的屏蔽迹线。这样的拓扑结构可能会减少噪声,但它创建了正是容易受到这种潜在阶段效应的结构。因此,使用屏蔽迹线而不加强设计规则可能会增强PID效应,例如,导致放大器的偏移电压增加,这些信号正是设计师首先想要保护的信号。 总结 PID是可能降低IC性能、可靠性和产量的工艺因素之一。有几个拓扑设计规则倾向于限制这些效应。然而,现有的设计规则没有解决一个关键问题,因此没有完全消除PID。关键问题是金属蚀刻的潜在阶段的遮蔽效应。需要额外的设计规则,如这里提出的,以完全消除这种效应。 |