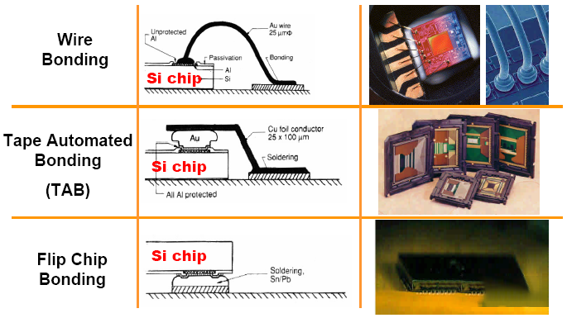

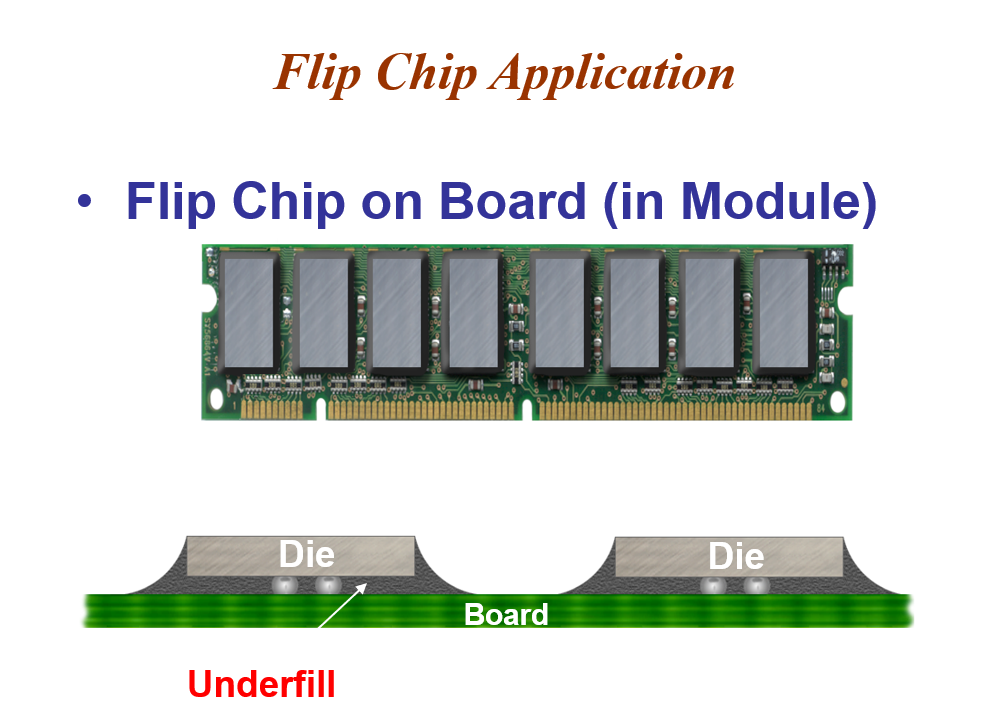

一、什么是芯片封装?芯片封装作为设计和制造电子产品开发过程中的关键技术之一日益受到半导体行业的关注和重视。封装的作用主要有保护电路免受外界环境的影响、避免噪声信号的污染,屏蔽外场的串扰,支撑封装体内机械机构、电气互连,缓解封装体内部的机械应力,提供从封装体内功率器件到外界环境的热传递路径,使芯片间的引线从封装体牢固地引出而非直接装配在基片上等功能。封装技术的优劣直接关系到芯片自身性能的发挥以及与芯片连接的PCB(印制电路板)的设计和制备,因此封装是至关重要的。 高密度封装应半导体技术的发展,实现电子器件由二维(2D)平面堆集到沿Z方向的高密度集成,以缓解、延续或超越摩尔定律的发展。 二、摩尔定律及后摩尔时代 1965年,美国仙童半导体公司的Gordon Moore博士提出了著名的Moore定律:当价格不变时,集成电路上可容纳的元器件数目,每隔18-24个月就会增加一倍。 这一定律准确预测了过去五十年半导体行业的发展。随着电子信息产业的不断升级,半导体集成电路正在向超大规模、超高速、高密度、大功率方向发展,当晶体管特征尺寸达到纳米级后,进一步减小晶体管尺寸无疑是困难且昂贵的,这也意味着摩尔定律接近尾声。基于这种情况,业界提出了超越摩尔定律(More-Than-Moore,MTM),试图从其它的一些途径来延续摩尔定律的发展趋势,并且从摩尔定律的“更多更快”,发展到MTM的“更好更全面”。如通过优化晶体管的设计,寻找硅的替代品和发展先进封装技术等,使一块集成电路芯片能够同时具有多种功能,这不仅可以降低芯片的生产成本还能提高电路的等效集成度。其中先进封装技术的应用无疑是后摩尔时代集成电路发展最有效的解决方法之一,特别是电子封装维度从二维(2D)向三维(3D)发展,通过三维片上集成、硅通孔(TSV)芯片互连和三维封装堆叠的形式,在晶体管特征尺寸不变的情况下,可以成倍的增加集成电路密度,从而更好的延续摩尔定律。 封装的结构方式包括引线键合(wire bonding,WB)、载带自动键合(Tape Automated Bonding)、倒装芯片(flip chip,FC)、硅通孔技术(Through Silicon Via)等。   三、倒装芯片(FC)底部填充的原因 电子封装结构也由双列直插式封装(Dualin-line package, DIP)、小外型封装(Small out-line package, SOP)、四侧引脚扁平封装(Quad flat package, QFP)等传统封装形式向倒装芯片(Flip-chip, FC)、倒装芯片-球栅阵列(FC-BGA)、扇入型晶圆级封装(Fan-inwafer level package, FIWLP)、扇出型晶圆级封装(Fan-out wafer level package, FOWLP)、嵌入式芯片封装(Embedded chip package, ECP)等先进封装形式发展。其中由FC与BGA技术融合而产生的FC-BGA封装已成为广泛采用的主流封装技术之一。   但FC封装中硅基芯片与高分子基封装基板之间热膨胀系数(Coefficient of Thermal Expansion, CTE)不匹配产生的热应力易造成焊点在热载荷作用下过早产生疲劳断裂乃至失效。1987年日本日立(Hitachi)公司Nakano首次提出在环氧树脂中加入SiO2并将其填充在芯片与基板之间来提高焊点的疲劳寿命,这种填充树脂后来逐渐发展成为底部填充胶(Underfill),也称为底部填充剂或底填胶等。  |