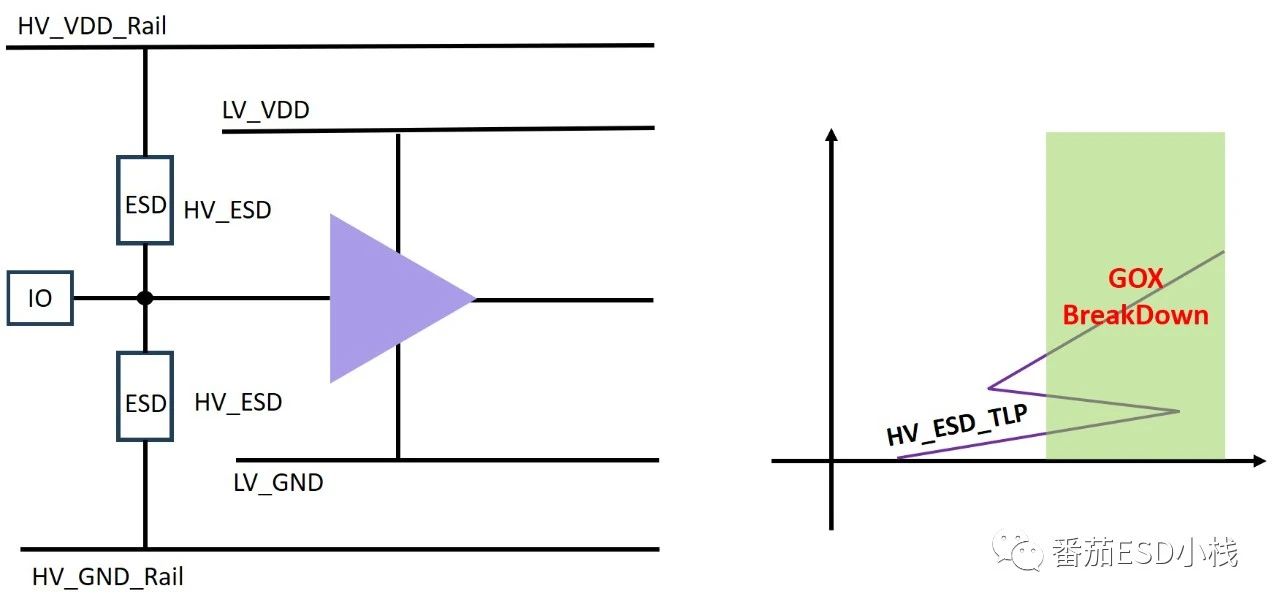

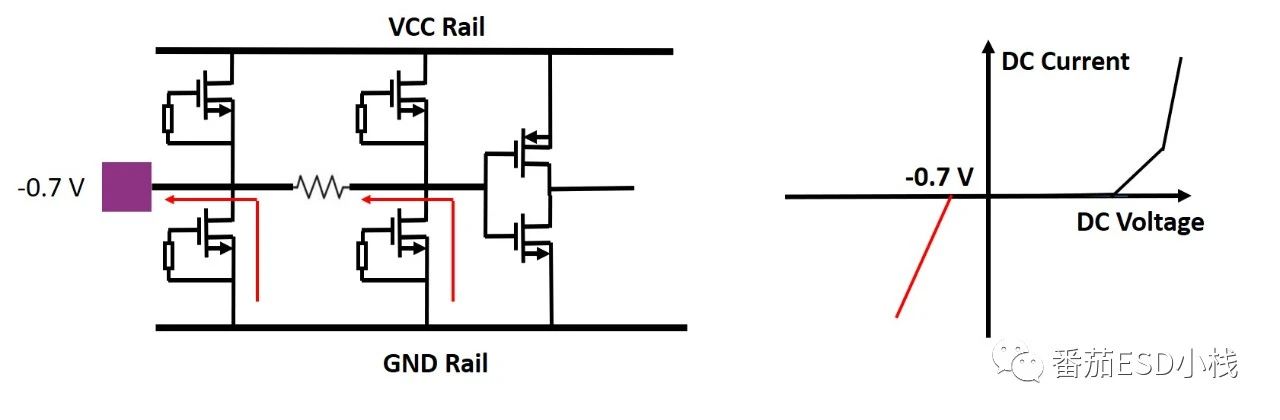

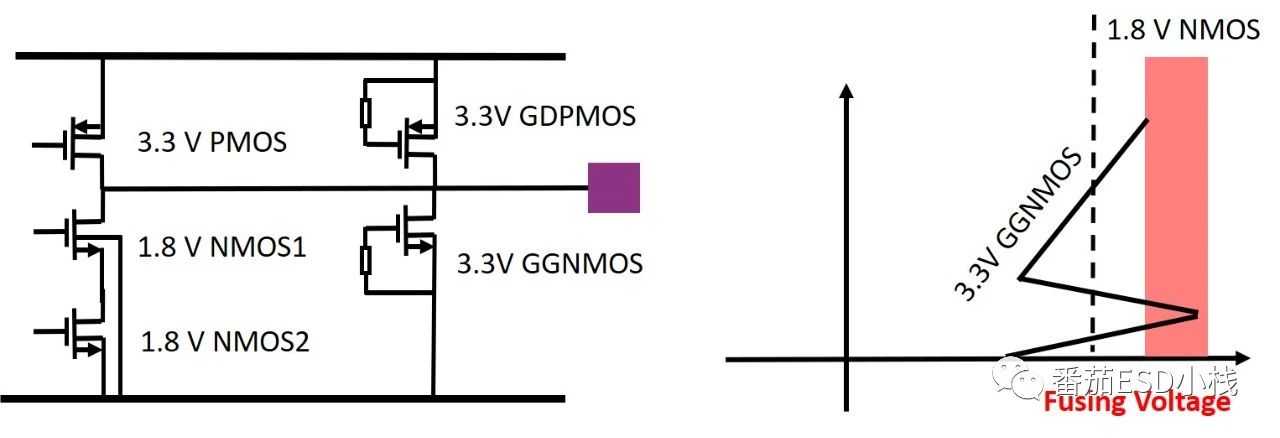

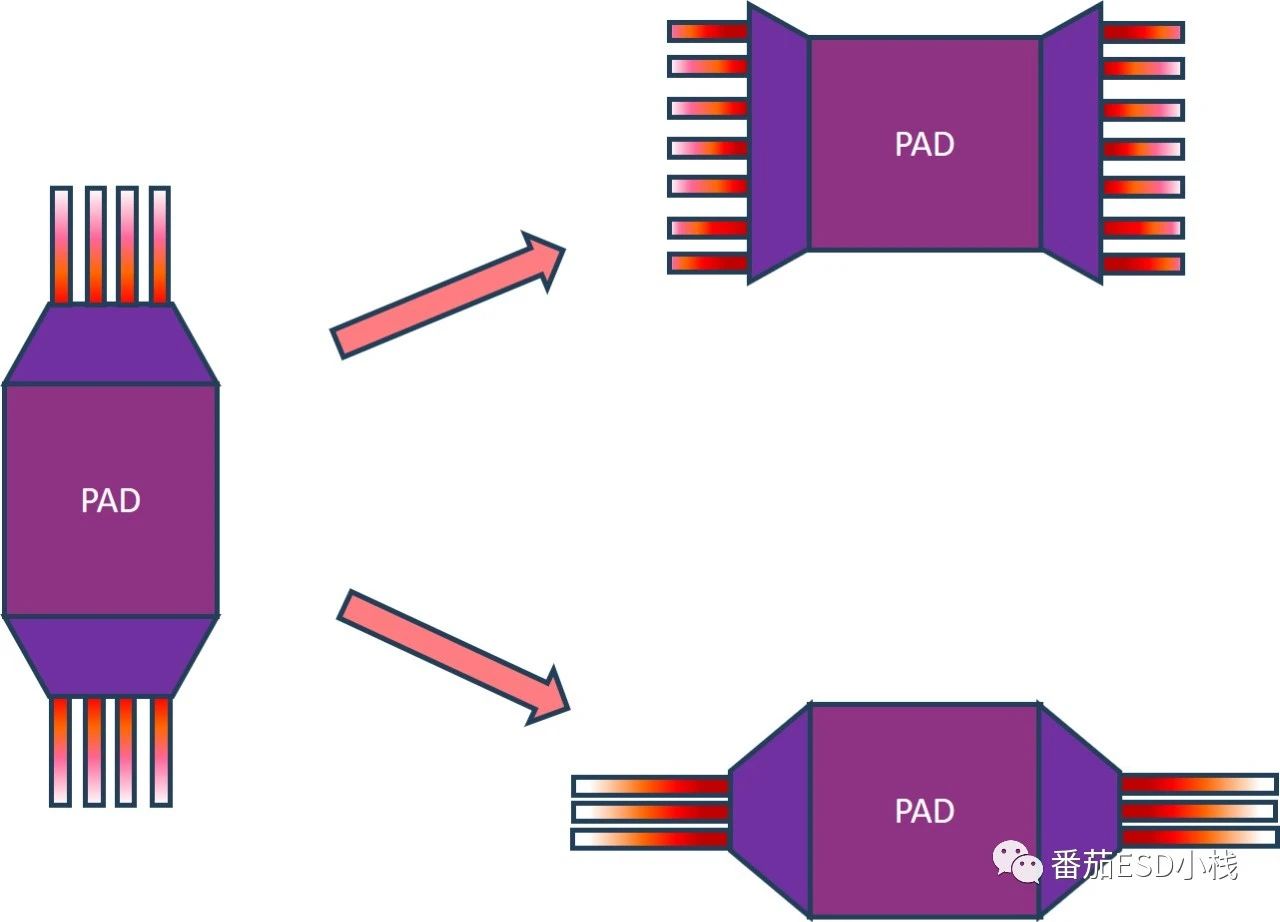

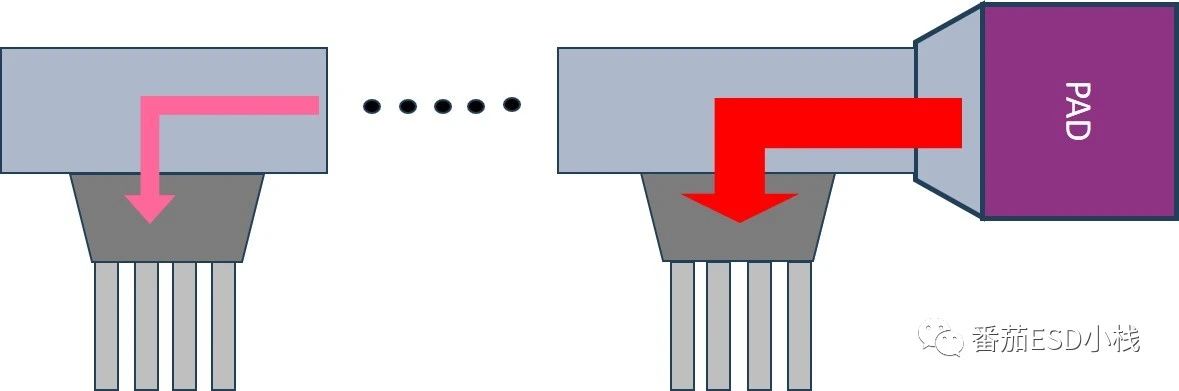

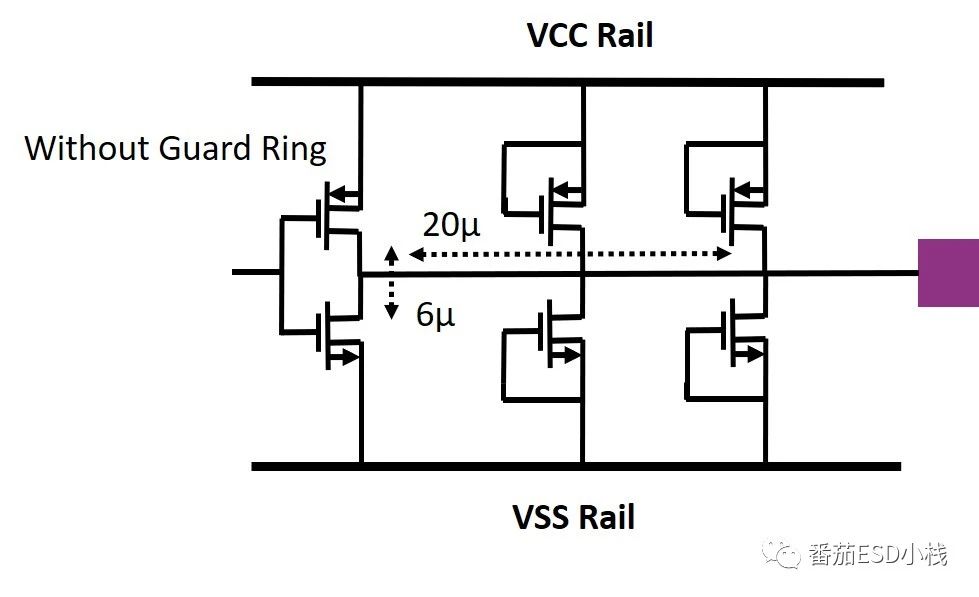

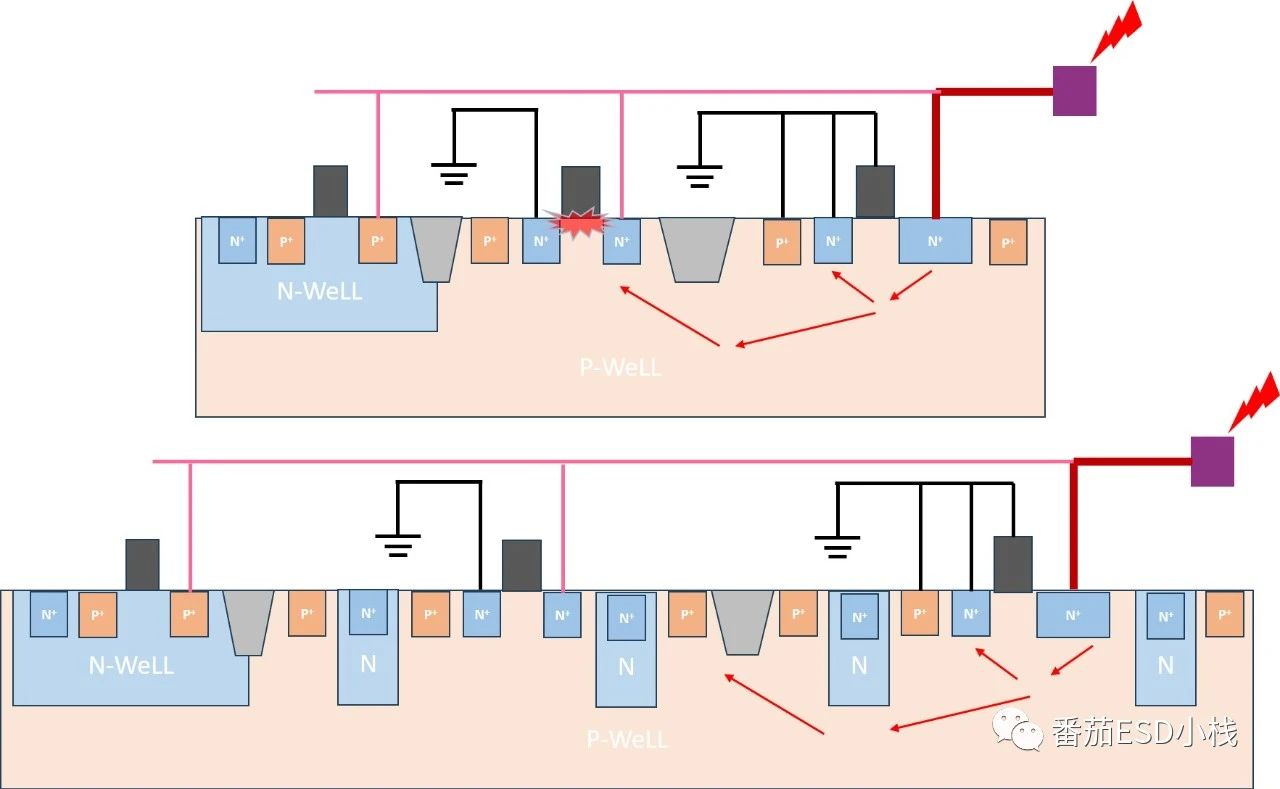

一. Design Window 设计不合理。Design Window是ESD设计的核心概念之一,关于Design Window之前一期已经叙述过了,这里列举几个Design Window不当造成的ESD失效案例。浅谈ESD防护—Design Window的确立 案例一 如图一所示,该芯片存在高低两个电压域,其中低压VDD是由内部LDO产生。IO是低压信号,其Input buffer是由低压MOS构成,属于低压域。但是端口ESD器件却连接HV_Rail,采用高压ESD器件。整个端口的TLP曲线如图所示,IO Input buffer的器件已经损坏,而HV_ESD器件尚未开启,这种属于Design Window上限选取错误。整个端口的Design Window 设计不合理。  图一.案例一电路与TLP曲线。 案例二 该案例来源于早年间的一款芯片,该芯片的IO电平范围是-1.5V到VCC,采用GGNMOS作为ESD防护器件。流片回来后有效输入最低只能到-0.7V左右。如图二所示,GGNMOS如果面对低于-0.7V的输入其内部寄生二极管便会导通,形成对地通路。该芯片就属于Design Window下限选取错误。针对负电压IO端口的ESD需要进行特殊设计。  图二.案例二电路与DC曲线。 案例三 如图三所示,该案例为了降低阈值采取Stack 1.8V NMOS的设计方法。但是NMOS1的衬底与GND相连,Design Window的上限是1.8V NMOS的对地失效电压,但是端口又采用3.3V GGNMOS,这就导致输出Buffer NMOS已经失效,而ESD器件还未开启。GGNMOS的TLP曲线会超过Fusing Voltage从而造成ESD失效。  图三.案例三电路与TLP曲线。 二.ESD设计不合理 不合理的ESD器件也会大幅度增加ESD失效风险。 案例四 如图四所示,该芯片采用GGNMOS作为ESD防护器件,当布局时受到面积约束,便对GGNMOS进行调整,在保证Total Width不变的情况下,改变Finger Width,使其满足约束。但是Finger Width是有安全范围的,Finger Width不能过低,否则会降低器件的热电性能,导致器件容易失效,且Finger数目过于密集也会带来开启不均匀的问题。但是Finger Width过高又会降低器件利用率,降低ESD防护性能。该案例便是Finger Width改的过低,导致GGNMOS在触发之后无法泄放大电流,造成ESD防护性能未达标。  图四.案例四版图与ESD电场分布示意图。 案例五 该案例采用SCR作为ESD防护器件,SCR属于Snap-Back型器件,ESD造成雪崩击穿后,器件会表现出负微分电阻特性。但是该案例不合理的设计导致SCR击穿即失效,造成这种现象的原因是N-WeLL中P+与P-WeLL中N+距离太近,N-WeLL/P-WeLL反偏时,空间势垒区进入P+/N+中,造成有源区短路,具体详见: 浅谈ESD防护设计—版图设计(二) 同理,SCR中有源区Width过低也会造成这种现象,因为有源区宽度过低导致电场过于集中,无法承受大电流。 案例六 如图五所示,该案例是将一个ESD器件拆开并分开放置,与二级防护不同的是该案例中两个被分开的ESD器件都是针对HBM防护。两个分立ESD器件的防护能力会大打折扣,大部分ESD电流只会通过第一个ESD器件泄放,第二个ESD器件的作用微乎其微。即便Total Width相同,两个分立ESD器件的泄放能力远不及一个整体器件。  图五.案例五版图示意图。 该案例会引入下一个案例:单纯增加ESD防护单元的数目对ESD防护性能的提升是有限的,而且边际效应会很显著。芯片端口的ESD性能受很多因素的影响,单纯增加防护单元的数量可能并不是一个行之有效的方案。 三.内部电路设计不合理 芯片整体的ESD防护能力除了与ESD器件相关外还会与内部电路相关,尤其是版图的布局布线。 案例七 很多Fab会在Design Rule中要求与Pad相连的Buffer采用多子隔离环与少子隔离环以提高器件鲁棒性。尤其是输出buffer,如果既没有采用隔离环,且距离ESD器件过近,输出Buffer可能会受到衬底漏电流的冲击。如图六所示,该案例中端口输出Buffer距离ESD器件仅有20μ,输出线宽为6μ,没有采用隔离环设计,该输出级Buffer发生了ESD失效。  图六.案例七电路示意图。 如图七所示,该输出级失效的主因在于距离PAD过近,且没有增加多子/少子隔离环,NMOS因衬底漏电流发生失效。GGNMOS与Output Buffer NMOS都是处于同一P-WeLL中,当GGNMOS面对ESD时大量电流会注入衬底,只要GGNMOS完全被触发后才会形成泄放通路,而触发之前大量电流会累积在衬底当中,这会对Output Buffer NMOS造成冲击,有可能Output Buffer NMOS的源漏在GGNMOS导通前便击穿失效。  图七.少子/多子隔离环示意图。 案例八 LDO的驱动管是芯片内部发生ESD失效的高风险器件,LDO的VDD最好不要从ESD Rail上走线。该案例中LDO直接从ESD_VDD_Rail上抽头,该设计一方面会造成LDO的输出不理想,另一方面会造成LDO驱动管面对ESD失效。 案例九 数字IC一般会集成很多IP,尤其是总线类IP,会频繁和不同模块间进行通信,针对这类IP都需要添加CDM防护单元。该案例就是IP与核心电路之间没有插入CDM防护单元,从而造成CDM失效。不过随着CDM造成的失效日益严重,现在很多IP也会在内部设计CDM防护单元,并在IP外要求插入CDM防护单元。但是芯片作为一个整体,芯片内最脆弱的地方决定了整个芯片的CDM等级,即便所有IP都能实现CDM 500V,但凡一个IP或电路没达到要求,整个芯片就无法达到既定的CDM防护目标,这就导致集成的IP越多,芯片越复杂,CDM设计难度越高。 |