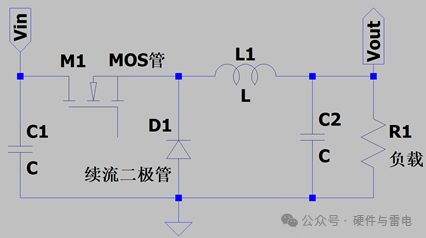

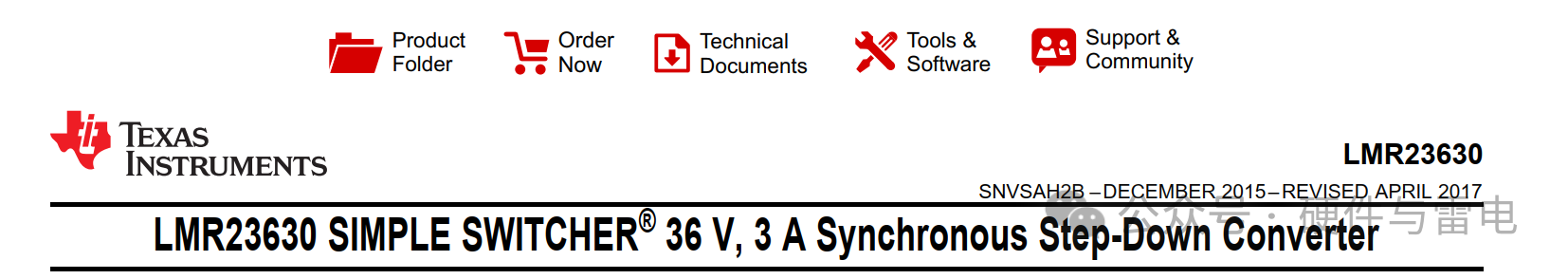

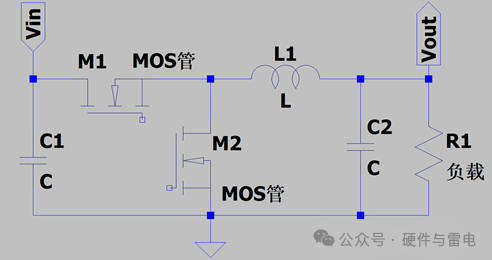

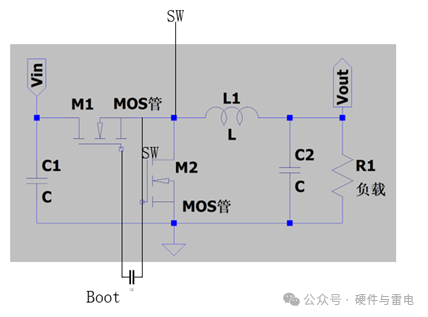

通过前面几篇文章,学习了基础元器件:电阻、电容、电感、二极管、三极管以及MOS管,下面就用这几个基础元器件,介绍一下BUCK电路的基本拓扑结构,以及在布局BUCK电路时的注意事项。开关电源基本拓扑有三种,Buck、Boost、Buck-Boost。英文看起来比较高端,其实中文翻译过来就是降压、升压和升降压电路。Buck电路是应用最广的,其基本拓扑图如下图所示。 拓扑图中MOS管作为开关,电感和电容作为能量存储,二极管作为续流通路。就这四个基本元器件就能组成最基本的Buck电路拓扑图。由于Mos管需要根据负载用电大小来不停地开和关,所以会产生高频震荡电压和电流信号,如果用数学语言来说就是dv/dt,和di/dt。因为EMI问题的根本目标就是要抑制dv/dt,di/dt,就Buck电路本身的原理来说,肯定要产生dv/dt,di/dt,所以作为电路设计师只能从PCB布局上,尽量减小Buck电路对其他电路的影响。那么具体电路中,应该如何进行Buck电路布局呢? 电路上大多用的是集成Buck电源芯片,而不是用上面几个分离元器件,外加一大堆分离元器件搭建的控制电路、反馈环路以及保护电路,那就直接分析集成Buck电源芯片应该如何布局布线。我们一起打开Buck电源的数据手册。  1、什么是同步buck,什么是异步buck? 开篇就说自己是同步buck,那什么叫同步buck呢?先说异步buck就是刚才图1那种拓扑图,也就是用二极管作为续流通路。但由于二极管的续流时功耗也不小。所以,后来有牛人就提出来,把那二极管也换成MOS管岂不更好?于是,就出现如下图的同步buck电路。  但这种同步buck电路需要另外的电路来控制M2的通断,保证M1开通时,M2关断,M1关断时,M2开通。这种高频率配合需要很精准,如果一旦出现M1、M2同时导通,那么就相当于电源对地短路,是绝不允许的。下面就把同步、异步buck电路的优缺点进行对比。

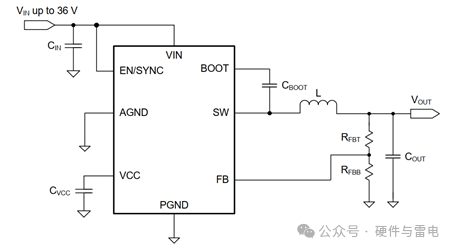

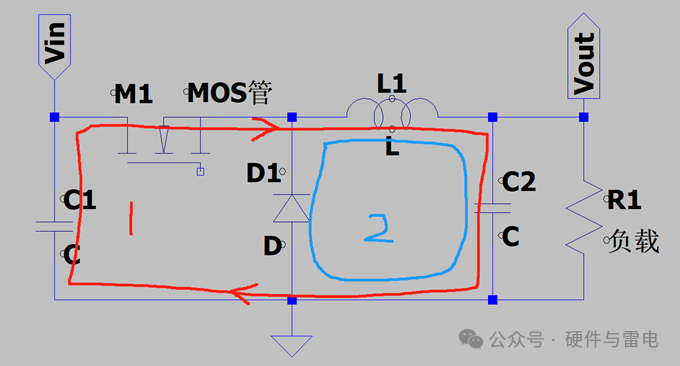

它的典型电路图如下,其中Vin是电源输入,SW定义为开关输出控制引脚,内部接的是MOS管,外部需连接电感。Boot为启动管脚,连接自举电容,自举电容连接在CB和SW引脚之间;用于驱动高侧MOS管的栅极,如果没有这个自举电容,当Mos管开通后,由于源级S电位抬高,导致Vgs小于导通门限Vth,导致Mos管没法继续开通。  如果把SW和Boot画在拓扑图中,那么就像下图一样。FB脚是电压反馈,用于监测外部Vout是否为想要的电压值。En是使能控制脚。  2、Buck电路PCB布局应该注意些什么? PCB布局设计的关键就是要找到电路系统的关键回路和关键节点,那么什么是电路系统的关键回路和关键节点?通常,电流变化率di/dt大的环路以及电压变化率dV/dt大的节点,就是关键回路和关键节点,在PCB布局设计的时候,要优先考虑和布局。  关键回路有两个,一个开通回路,上图红色回路,另外一个为续流回路,上图的蓝色回路。关键节点就是电感L与二极管、MOS管的交点,也就是buck芯片的SW引脚。 我们要让这两个环路的面积越小越好,因为每一个电流环都可以看成是一个环路天线,会产生辐射,会引起EMI问题,也会干扰板上其它的电路,而辐射的大小与环路面积呈正比。其中首要保证第一个环路越小越好。其次保证输出第二个环路越小越好。 其实每个芯片手册中都会有推荐的布局,以及需要注意的地方。 1、输入端口的滤波电容和旁路电容尽可能地靠近输入管脚; 2、电感,输出电容以及二极管形成的回路越小越好,输出电容尽量靠近电感; 3、反馈电阻尽量靠近反馈引脚,反馈网络取电压时,从输出电容后侧取电压,且走线远离电感和二极管。 4、主回路下面不要走弱信号; 5、一般不建议电感下面铺铜,接地层出现的涡流会导致电感的感量变小; 当然这一点与使用的电感类型也有关系,比如带屏蔽一体成型的屏蔽电感即使下面铺铜关系也不大。 当然,这些注意事项说起来很抽象,下期我们将以几个实际布局布线的案例来分析应该如何进行Buck电路的布局布线。下期见! |