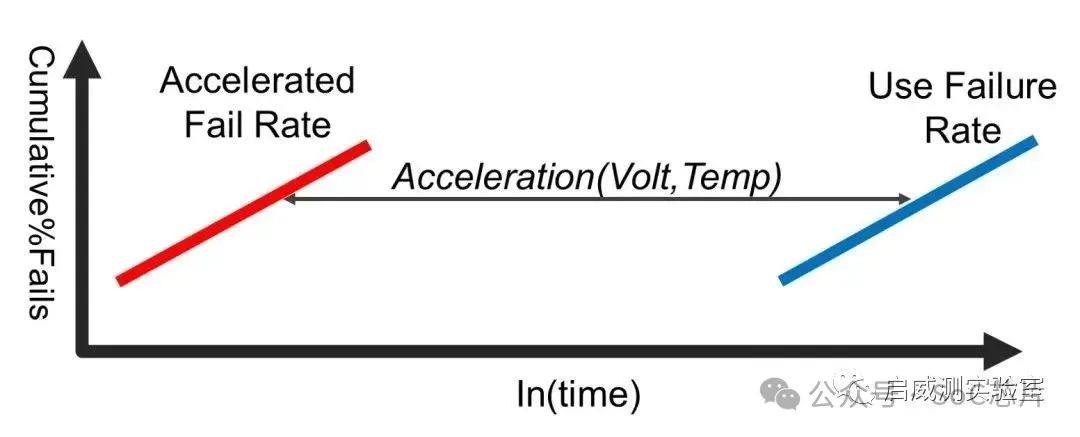

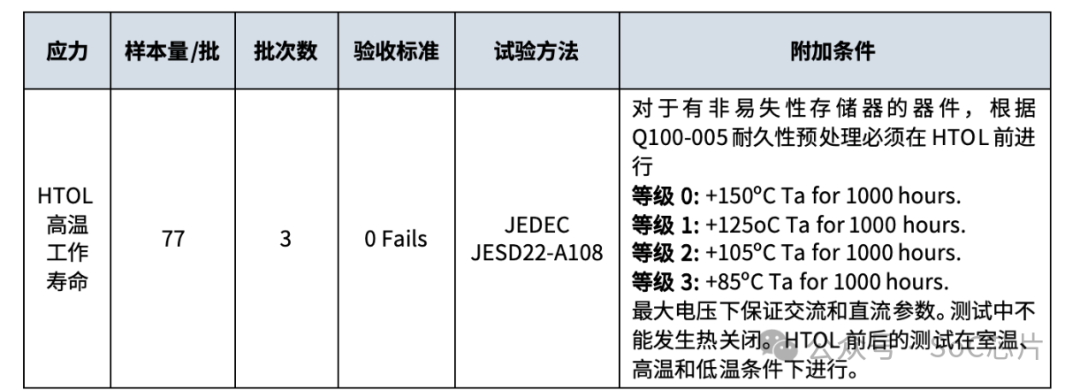

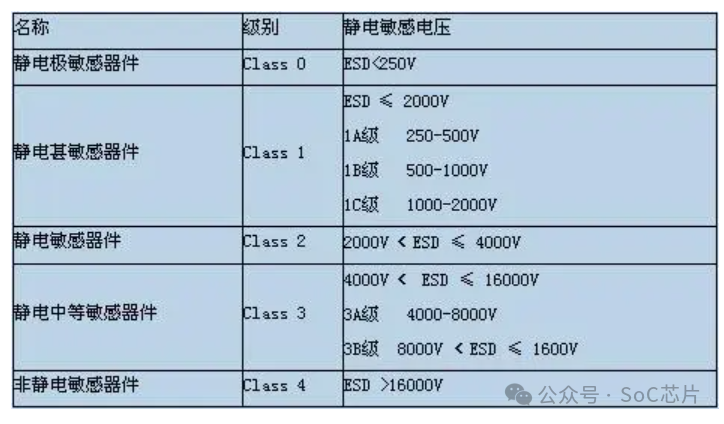

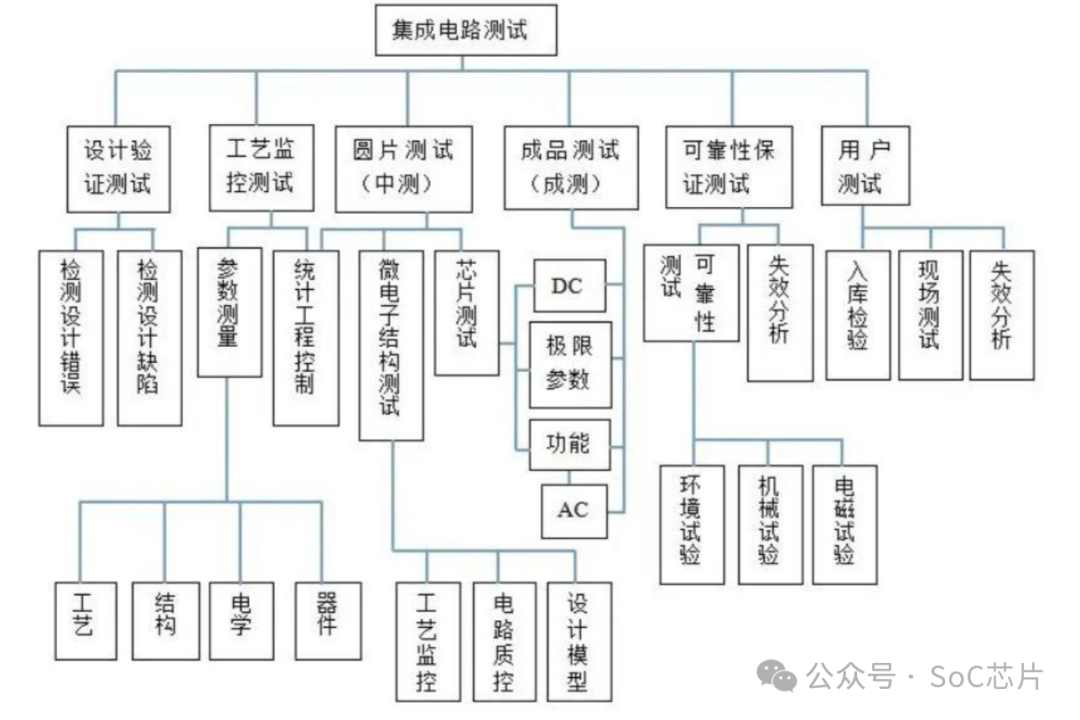

1概述芯片可靠性测试是一种系统性的评估方法,用于确保集成电路(IC)或芯片在其预期的使用寿命内,在各种工作条件下能够持续稳定运行。可靠性测试涵盖了一系列严格的实验程序,旨在模拟芯片可能遭遇的极端环境和应力条件,以识别潜在的失效模式,并评估芯片在这些条件下的性能和耐用性。  可靠性测试的定义主要包括以下几个方面: (一)目的:可靠性测试的首要目的是验证芯片在设计寿命期内的稳定性和耐用性。它帮助识别设计中的弱点和潜在故障点,确保芯片在各种工作环境和条件下能够可靠地工作。 (二)测试条件:测试通常在比正常操作条件更为严苛的环境下进行,包括但不限于极端温度、湿度、电压波动、辐射、物理应力等,以加速老化过程,快速识别可能的问题。 (三)测试类型:可靠性测试包括多种类型,如温度测试(高温、低温、温度循环)、电压测试、功能测试、寿命测试、环境测试、封装测试、功率和热测试、材料测试等。 (四)统计分析:测试通常基于一定的样本量进行,结果需要通过统计分析来评估整个批次或型号的可靠性。常用的统计方法包括平均失效时间(MTTF)、平均无故障时间(MTBF)等。 (五)标准遵循:可靠性测试往往遵循国际或行业标准,如JEDEC(Joint Electron Device Engineering Council)标准,确保测试方法和结果的统一性和可比性 。 (六)结果应用:测试结果用于指导设计改进、材料选择、制造工艺优化和质量控制,以提高芯片的可靠性,减少后期的故障率和维护成本。 通过全面的可靠性测试,芯片制造商能够确保产品满足特定的性能规格,符合行业标准和法规要求,同时也为客户提供质量保证,增强市场竞争力。

|