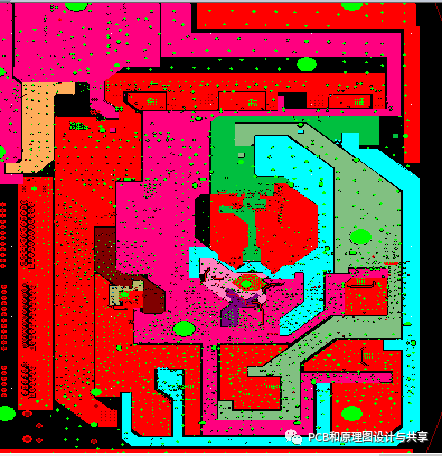

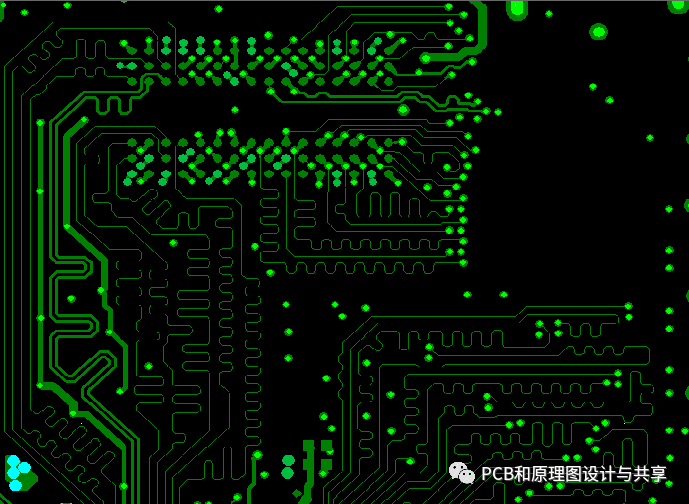

一,从电源完整性来考虑PCB的设计1,去耦电容的布局 高速PCB设计中,去耦电容起着重要的作用,它的放置位置也很重要。这是因为在电源向负载短时间供电中,电容中的存储电荷可防止电压下降,如电容放置位置不恰当可使线阻抗过大,影响供电。同时电容在器件的高速切换时可滤除高频噪声。对于去耦电容的放置,我们知道,如果位置不当的话会增大线路阻抗,降低其谐振频率同时影响供电。小容值电容去耦路径短,所以一般摆放靠近IC,否则起不到去耦效果;大容值电容去耦路径长,摆放位置相对宽松一些。所以输入电源,一般是先经过大电容,再经过小电容,再进入IC芯片。  2,电源回路的设计 电源回路的设计要保证电源完整性,我们知道,良好的电源分配网络是必不可少的。首先对电源线和地线的设计,我们要保证线宽加粗,这样才能尽可能地减少其阻抗值。随着芯片的速度越来越高,我们越来越多地使用多层板,通过专用的电源层做电源平面分割供电和专用的地层构成回路,这样就减少了线路的电感。  二.从信号完整性来考虑PCB的设计 PCB的信号完整性问题主要包括信号反射、串扰、信号延迟和时序错误。 1、反射:信号在传输线上传输时,当高速PCB上传输线的特征阻抗与信号的源端阻抗 或负载阻抗不匹配时,信号会发生反射,使信号波形出现过冲、下冲和由此导致的振铃现象。PCB设计时一般是通过做阻抗匹配来防止反射的产生。 单端50 ohm  差分100 ohm  2、 串扰:在PCB中,串扰是指当信号在传输线上传播时,因电磁能量通过互容和互感耦合 对相邻的传输线产生的不期望的噪声干扰,它是由不同结构引起的电磁场在同一区域里的相互作用而产生的。互容引发耦合 电流,称为容性串扰;而互感引发耦合电压,称为感性串扰。在PCB上,串扰与走线长度、信号线间距,以及参考地平面的状况等有关。PCB设计时一般是通过3W原则或者是包地防止串扰的产生。  3、信号延迟和时序错误:信号在PCB的导线上以有限的速度传输,信号从驱动端发出到达接收端,其间存在一个传输延迟。过多的信号延迟或者信号延迟不匹配可能导致时序错误和逻辑器件功能混乱。这种情况,一般是DDR产生,所以PCB设计时一般是做等防止信号延迟和时序错误的产生。  三.从EMC角度来考虑PCB的设计 EMC三大要素,干扰源,传播途径和敏感器件。所以设计时从消除干扰源,切断传播途径和蔽屏敏感器件入手,以下的方法就是居于这些思路来考虑的。 1,合理布局 在器件布置方面,原则上应将相互有关的器件尽量靠近,将数字电路、模拟电路及电源电路分别放置,将高频电路与低频电路分开。易产生噪声的器件、小电流电路、大电流电路等应尽量远离逻辑电路。对时钟电路和高频电路等主要干扰和辐射源应单独安排,远离敏感电路。  2,屏蔽设计 屏蔽是解决电磁兼容问题的关键技术。电磁屏蔽的方法就是以金属或者磁性材料来隔离电磁干扰由一个区域向另一个区域感应或辐射传播。一般分为两种类型:一种是静电屏蔽,主要是防止静电场和恒定磁场的影响。另一种是用于防止交变电场、交变磁场、交变电磁场的影响。  3,叠层设计 总的来说叠层设计主要要遵从两个规矩:1. 每个走线层都必须有一个邻近的参考层(电源或地层);2. 邻近的主电源层和地层要保持最小间距,以提供较大的耦合电容。  |