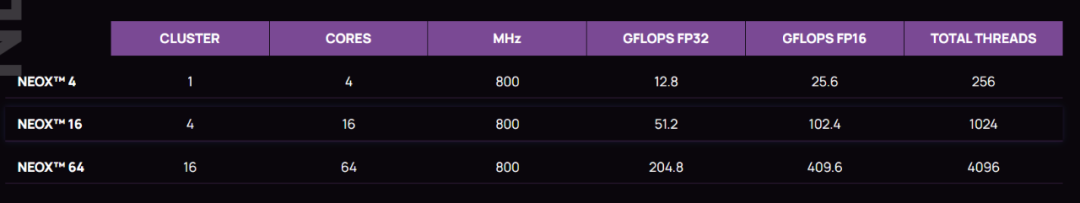

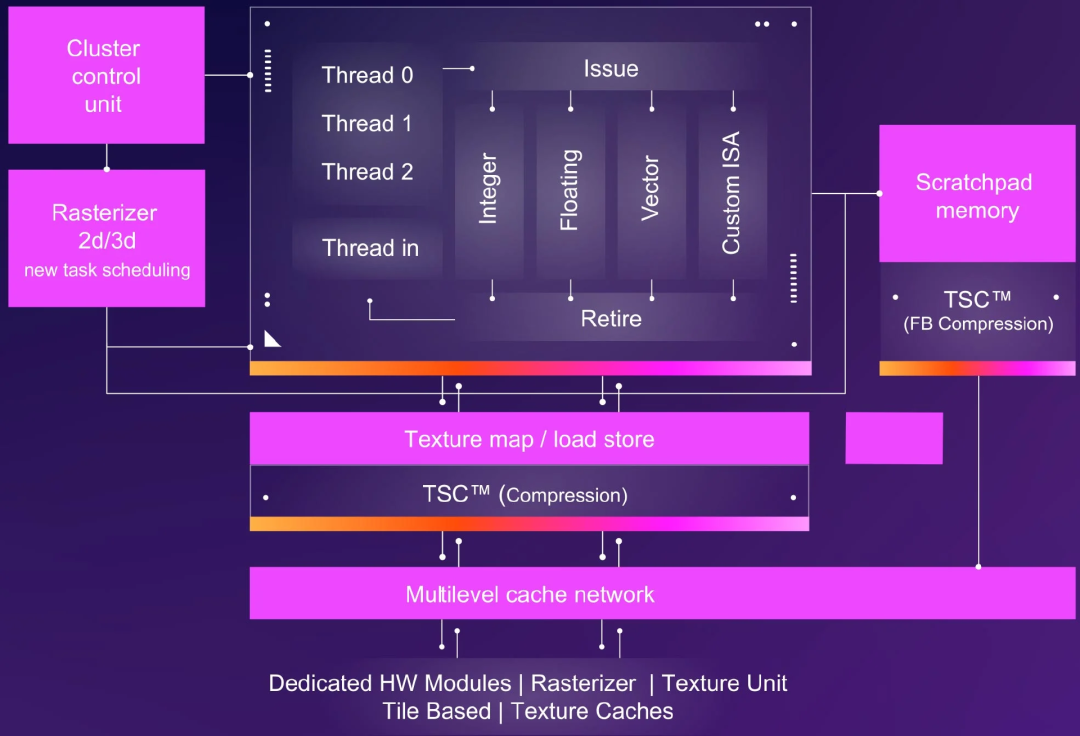

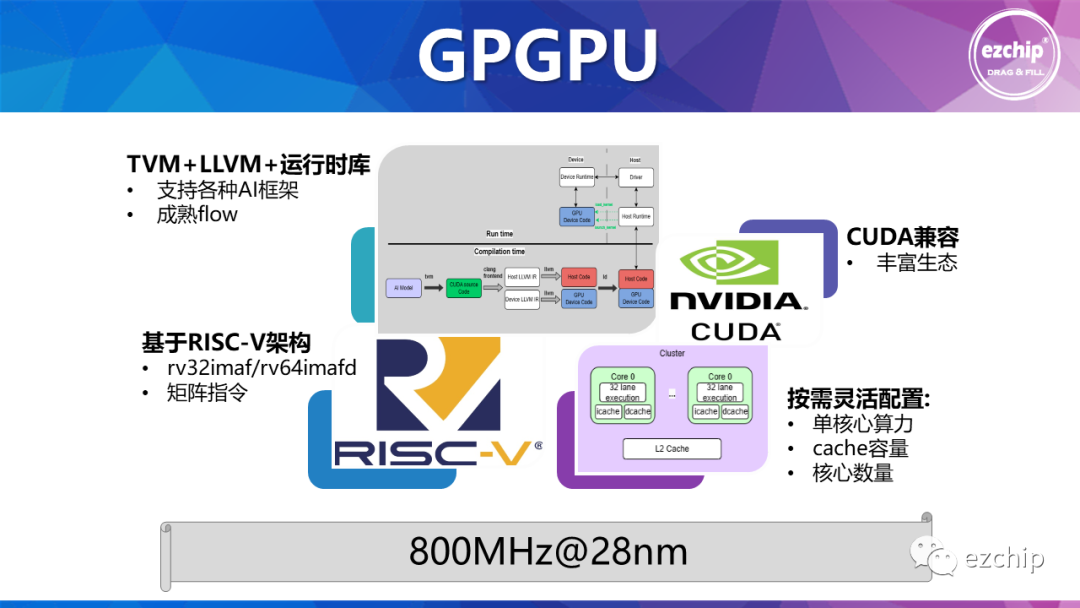

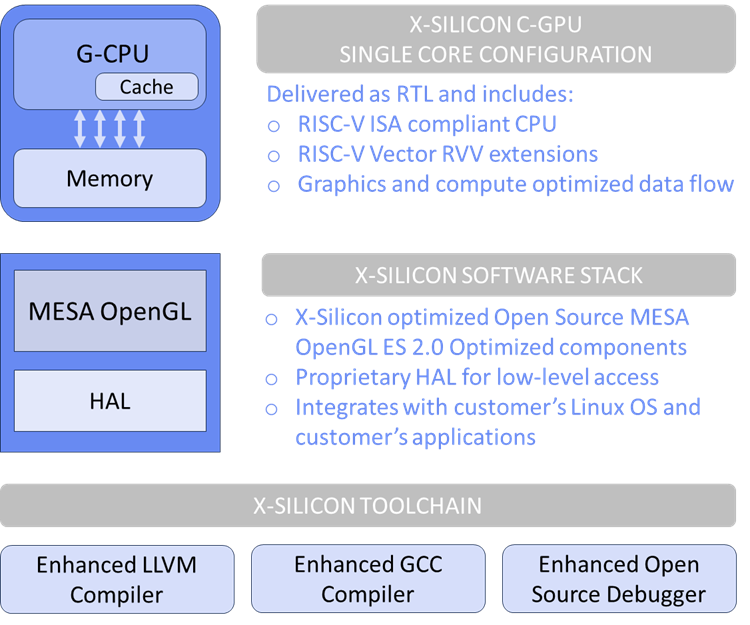

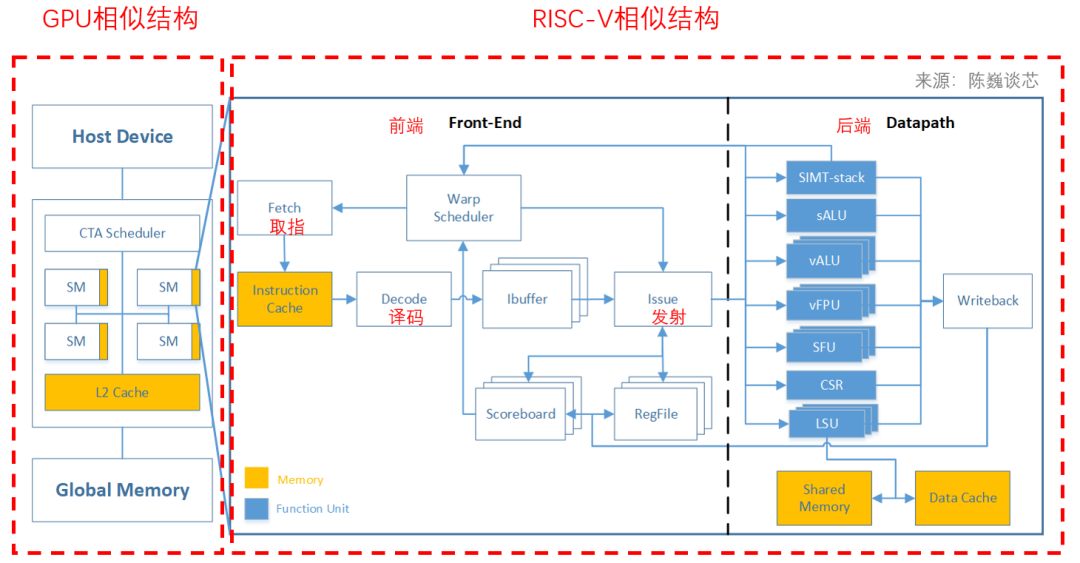

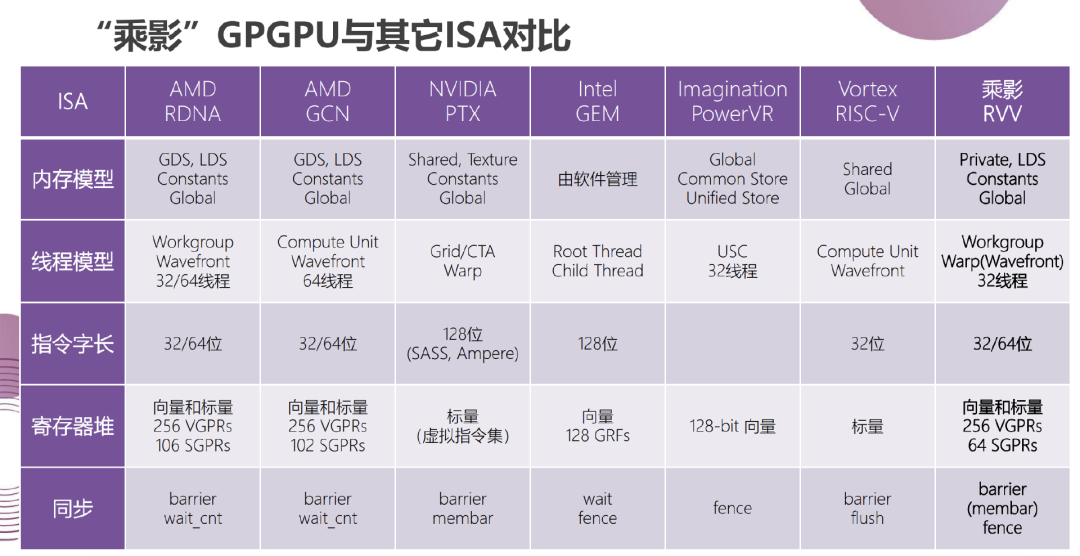

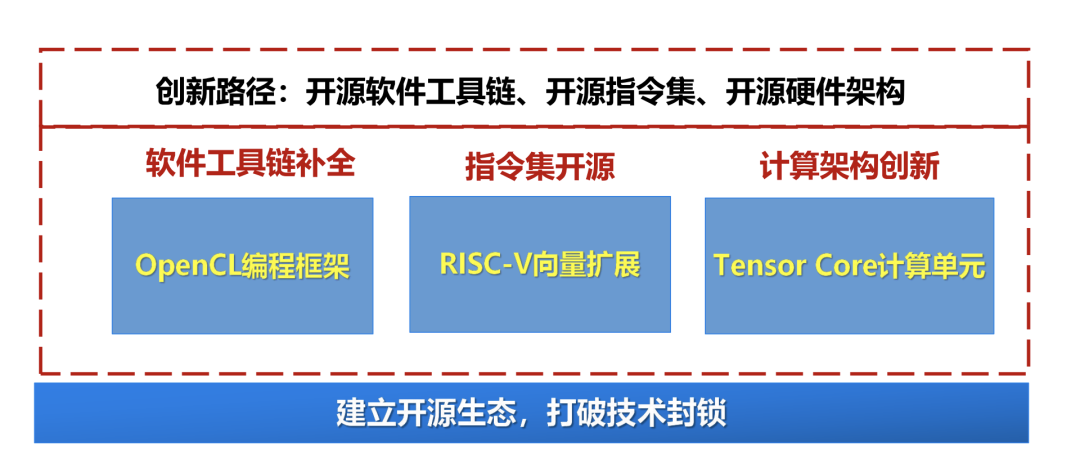

RISC-V一直以其开源特性而备受业界关注。不过,一直以来,RISC-V相关IP主要集中在CPU领域,而事实上,它也可以用在GPU领域。你我都知道,GPU领域几乎被一两家企业所统治,这是因为GPU领域生态是最大的壁垒。加之专利门槛极高,GPGPU(通用GPU)IP在图形处理领域一直不温不火。 最近几年,业界开始探索通过扩展和改写RISC-V CPU指令集,来制造GPU。 付斌|作者电子工程世界(ID:EEWorldbbs)|出品 RISC-V GPU,有产品了 对于RISC-V来说,GPU IP一直是一个痛。虽说Imagination曾经宣布其GPU IP将会支持RISC-V CPU,但真正将RISC-V做成GPU的却屈指可数。 真正使用RISC-V设计制造GPU的产品出现在2019年,那一年,一家成立于2007年的希腊IP厂商——Think Silicon推出业界首款基于RISC-V ISA的3D GPU NEOX V。 这家公司对于RISC-V GPU赛道极为执着,紧接着在2022年的Embedded World上,展出业界首款基于RISC-V的GPU,命名为NEOX G系列和A系列。  今年Embedded World,Think Silicon又展示了用在MCU上的GPGPU方案NEOX-GA100,也是业界首个基于RISC-V的GPGPU架构,同时该公司拥有RISC-V RV64架构的全部权利。 根据官网显示,作为轻量级3D图形系统,整个3D、VG和2.5D API需要不到150KB的内存和10mW的功率,非常适合从低功耗裸机到RTOS和基于Linux的高性能系统。此外,该产品也可以在不增加芯片成本的情况下实现AI应用。  NEOX-GA100架构,图源|Think Silicon 国内方面,也有相关产品发布。2023年11月,上海逸集晟(ezchip)发布了一款GPGPU核心IP——RVG-1。RVG-1是一个基于RISC-V架构,并且完整支持CUDA源码编译的软硬件一体解决方案。 官方信息显示,RVG-1在硬件上充分利用了RISC-V架构扩展指令的灵活性。基于RV32IMAF/RV64IMAFD基础指令集,增加了进程调度/管理指令和矩阵存取/计算指令的支持,并引入了多级缓存和存储控制,构建了一个可灵活配置核心算力/数量和缓存容量的GPGPU核心。目前在28纳米工艺下,该核心可以运行在800MHz,并且仍在持续优化中。  目前来看,RISC-V GPU IP厂商们的野心的目标都很大,一方面布局边缘端的低功耗GPGPU,另一方面布局科学计算、AI的大型GPGPU。 全世界都在研究RISC-V GPU架构 事实上,全世界都不想看一两家厂商垄断市场,都在想办法做各种开源GPU架构,这其中既包含较老的指令集或是中间语言进行实现,有些则基于RISC-V CPU指令集进行改进和扩展来实现GPGPU的功能。  开源GPU汇总,图源|陈巍谈芯 2021年,乔治亚理工研究了一种支持CUDA的RISC-V GPU架构——Vortex。  前几日,一个成立于2022年的美国公司X-Silicon发布了其开放标准、低功耗的C-GPU架构。 根据介绍,C-GPU架构将打造成为开源、统一的RISC-V 矢量 CPU-with-GPU ISA 架构,C-GPU采用NanoTile架构,X-Silicon将这种CPU/GPU混合处理器称为“万能处理器”。其处理器专为动态内容最佳管理和渲染而设计,并超越传统GPU限制。 翻译翻译就是把基于RISC-V架构的CPU和GPU放在同一个核内。  X-Silicon的单核概念,图源|X-Silicon 国内方面,上海清华国际创新中心集成电路研究平台推出的首款基于RISC-V向量扩展(RVV)的GPGPU“Ventus(乘影)”,是国内首个开源GPGPU,也为后续协同企业开发国产全自主GPU商用产品的路上迈出关键一步。 根据官方信息显示,RVV GPGPU参考RISC-V CPU开发思路,在满足SIMT基础功能同时,汲取RISC-V向量扩展在功能定义和指令设计上优势,将二者有机结合,使乘影同时具备向量处理器工具链兼容性和GPGPU编程灵活性。  乘影架构解读,图源|陈巍谈芯 陈巍博士解读,乘影主体大框架借鉴GPGPU的结构,每个流多处理器(Streaming Multiprocessor,SM)主体结构接近于RISC-V。后端执行则直接使用处理器中常用ALU、FPU、LSU。为了让SM能够完成GPGPU工作,乘影里添加了SIMT-stack和SFU这类GPU中的常见功能模块。   2024年2月,芯瞳成功开源了一款基于RISC-V指令集的GPU处理器模型RVGPU,这是芯瞳在RISC-V + GPU方向持续研究取得的重要突破。 根据官方介绍,RVGPU采用SIMT(单指令多线程)技术,现已成功实现对CUDA(Compute Unified Device Architecture)的兼容支持,包括CUDA编译器和运行时环境。除此以外,RVGPU的架构指令CModel仿真模型允许开发者在模拟环境中模拟GPU的各种指令和行为。  RVGPU软件栈,图源|芯瞳半导体 综合来看,上述产品均基于LLVM开源工具链完成GPGPU编译器的开发,支持OpenCL开源并行编程框架。  可见,所有厂商都有着一个共同的目标,那就是建设一个开源GPU生态。 不过,总的来说,GPU是一个非常复杂的产品,绝不仅仅只是一个开源GPU就能够与现有玩家五五开的,未来还依赖大量的研发与投入。 用RISC-V做GPU,有好也有坏 用RISC-V做GPU,有人拍手叫好,也有人觉得多此一举。 觉得它好的人,认为RISC-V可以直接套用RISC-V的生态,不需要完全自建GPU生态,规避了与CUDA的专利对决。毕竟这是个开源的GPU IP,大家都加入到开源建设的大家庭,就能够弥补GPU生态不足,也不容易踩到知识产权的坑。 与此同时,每个SM核的独立性更好,可以执行比常规GPU CUDA核更复杂的计算。如果加上MMU,未来甚至可以在每个SM核上跑操作系统,非常有利于虚拟化。 觉得它不好的人,认为目前的RISC-V GPU产品,都是目前NVIDIA的GPU的形似物,设计没有什么太大差别,而HBM这样的器件八成是用不起的,其它诸如Nvidia GPU里面的Texture Unit也是缺失的。 更何况,CUDA这样的生态是很难跨越的鸿沟。有大佬曾言:“如果你看一下GPU的生态系统,就会发现工具链是由NVIDIA控制的,包括AMD在内的其他竞争对手都试图打破垄断,但失败了。通过扩展RISC-V标准指令集,几乎不可能与不断更新的NVIDIA生态系统兼容。另一方面,也很难重新开始,因为英伟达拥有先发优势。” 所以,对于大部分RISC-V GPU来说,支持CUDA生态至关重要,我们也看到许多厂商确实也是这样做的。因为虽然通过LLVM可能只需要重构compiler后端,但性能好不好就是另外一回事了。 还有比较激进的观点,认为从RISC-V开始做GPU,不如直接从白纸开始做。他们认为,要使基本的RISC-V指令集适应GPU任务,需要大量投资来定义自定义ISA扩展,构建高度复杂的微架构更改,并对开源工具进行大手术,使它们几乎与原始工具相似。这样一来,使用RISC-V的几乎所有潜在价值,都被定制架构比下去了。 就连上海交大也曾经说过,“我们想做的是一个独立完整的GPGPU架构和指令设计,而不依赖于现有RISC-V CPU开源指令,这样才能更完备地打造和融入原生的GPGPU生态 ,从而与现有的各种CPU系统无缝衔接。”所以因此,他们做了“青花瓷”这样一个定制的开源GPGPU架构。 但多一条路线,总归是好事。毕竟RISC-V CPU发展迅速,如果RISC-V CPU发展好,RISC-V GPU就能跟着“发财致富”。这条路好不好,就全看RISC-V能发展成什么样子了。 |