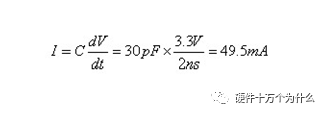

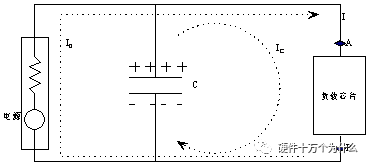

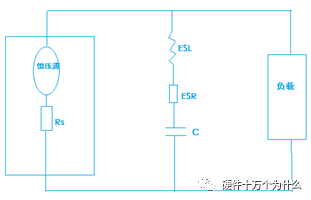

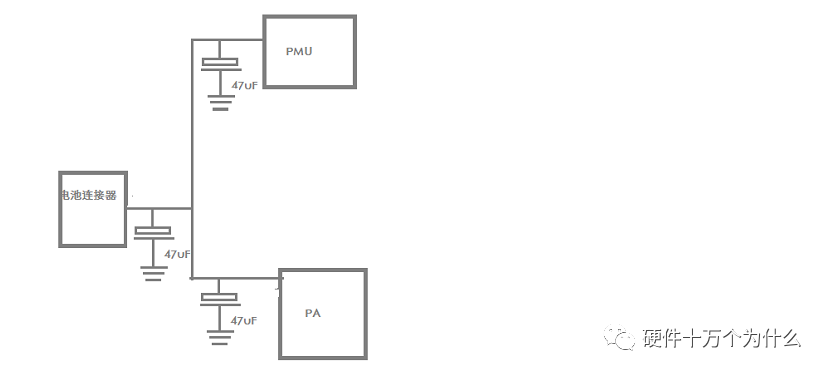

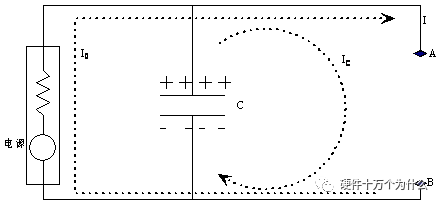

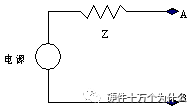

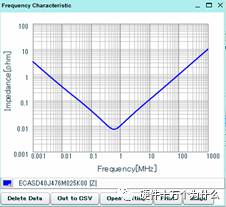

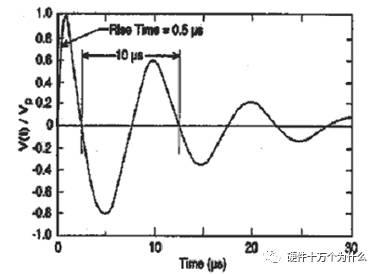

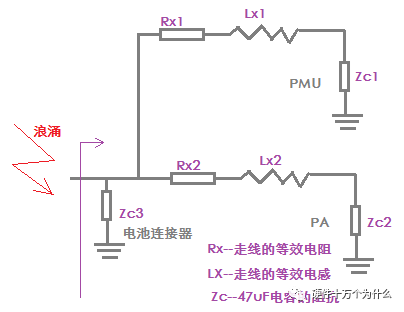

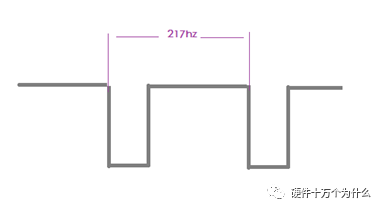

采用电容去耦是解决电源噪声问题的主要方法。这种方法对提高瞬态电流的响应速度,降低电源分配系统的阻抗都非常有效。对于电容去耦,很多资料中都有涉及,但是阐述的角度不同。有些是从局部电荷存储(即储能)的角度来说明,有些是从电源分配系统的阻抗的角度来说明,还有些资料的说明更为混乱,一会提储能,一会提阻抗,因此很多人在看资料的时候感到有些迷惑。其实,这两种提法,本质上是相同的,只不过看待问题的视角不同而已。 1. 从储能的角度来说明电容退耦原理。在制作电路板时,通常会在负载芯片周围放置很多电容,这些电容就起到电源退耦作用。其原理可用图1说明。   (公式1) (公式1)只要电容量C足够大,只需很小的电压变化,电容就可以提供足够大的电流,满足负载瞬态电流的要求。这样就保证了负载芯片电压的变化在容许的范围内。这里,相当于电容预先存储了一部分电能,在负载需要的时候释放出来,即电容是储能元件。储能电容的存在使负载消耗的能量得到快速补充,因此保证了负载两端电压不至于有太大变化,此时电容担负的是局部电源的角色。 从储能角度理解电容容易造成一种错觉,认为电容越大越好。而且容易误导大家认为储能作用发生在低频段,不容易向高频扩展。实际上,从储能角度理解,可以解释任何电容的功能。下面举例。  图2 电容储能作用向高频扩展 如上图所示,假设在低频段,比如几十khz,由于低频信号在电感上产生的感抗可以忽略,所以在低频段电容的ESL可以近似等于0。当负载瞬间(几十khz)需要大电流的时候,电容可以通过ESR向负载供电,供电的实时性很高,eSR只是消耗了一部分电量,但不影响供电的实时性。由于频率比较低,所以放电时间也比较长(频率的倒数),所以需要电容的容量较大一些,可以长时间放电。所以低频段储能好理解。 同样大的电容,假设负载突变的频率较高(几十Mhz或者更高),那么当负载顺么变化的时候(几十Mhz或者更高),ESL上形成的感抗不容忽视,这个感抗会产生一个反向电动势去阻止电容向负载供电,所以负载上实际获得的电流的瞬态性能比较差,即,电容的电流无法供应瞬间的电流突变,尽管电容容量很大,但由于ESL较大,此时的大容量储能发挥不了作用。实际上,频率较高,电容给负载供电的时间缩短(频率的倒数),也不需要电容有那么大的储能。对于高频,关键的因素是ESL,要降低电容的ESL,选择小封装的小电容,ESL显著降低,这就是为什么我们高频选择小电容的原因,另外走线长度引入的电感也会折算到ESL参数里,所以小电容一定要靠近pin。 从储能的这个角度理解甚至可以扩展到pF级电容。理论上假设不存在ESR,ESL以及传输阻抗为0,则一颗大电容完全胜任所有频率。但这种假设并不存在。所以电路中需要大小电容合理搭配去应对不同频率下的负载的能力供给。而且电容越靠近负载,传输线的等效电感,电阻的影响就越小。  图3 手机Vbat电源电容分配图 举例,在手机设计中,给vbat供电支路的几个分支上都挂47uf电容,如上图所示,连接器附近,PMU附近,PA附近都挂47uf电容,认为只有PA旁边的47uf对PA有效果,连接器旁边的,PMU旁边的对PA没有效果,实际不是这样的,当PA需要瞬间电流的时候,三颗钽电容都会向PA供电,供电过程完全取决于瞬间压差,哪颗电容与PA的瞬间压差最大,哪颗供电越积极。远离PA的电容需要考虑传输线的阻抗和感抗。对于低频,这点寄生感抗可以忽略。对于217HZ来说,PA所需的电流三颗电容加起来都远远不够用,故在GSM大功率的时候,PA从三颗电容上均取电流。 对于低频,寄生电感的作用可以忽略,这些大电容距离芯片的远近只要体现在走线电阻上,一般电源线走线电阻压降在100毫欧以内,对电容充放电影响非常小,故可以认为大电容在主板上可以不必追求距离芯片非常近。 从储能的角度来理解电源退耦,非常直观易懂,但是对电路设计帮助不大。因为不好从量化角度去考量,适合定性分析。从阻抗的角度理解电容退耦,能让我们设计电路时有章可循。实际上,在决定电源分配系统的去耦电容量的时候,用的就是阻抗的概念。

|

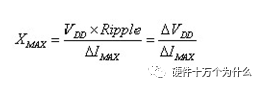

(公式2)

(公式2)

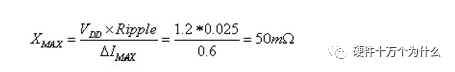

为要进行去耦的电源电压等级,常见的有5V、3.3V、1.8V、1.26V、1.2V 等。

为要进行去耦的电源电压等级,常见的有5V、3.3V、1.8V、1.26V、1.2V 等。 为允许的电压波动,在电源噪声余量一节中我们已经阐述过了,典型值为2.5%。

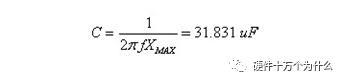

为允许的电压波动,在电源噪声余量一节中我们已经阐述过了,典型值为2.5%。 为负载芯片的最大瞬态电流变化量。该定义可解释为:能满足负载最大瞬态电流供应,且电压变化不超过最大容许波动范围的情况下,电源系统自身阻抗的最大值。超过这一阻抗值,电源波动将超过容许范围。

为负载芯片的最大瞬态电流变化量。该定义可解释为:能满足负载最大瞬态电流供应,且电压变化不超过最大容许波动范围的情况下,电源系统自身阻抗的最大值。超过这一阻抗值,电源波动将超过容许范围。