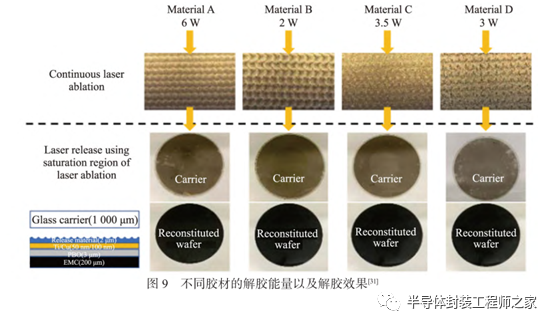

摘要:随着摩尔定律逐步达到极限,大量行业巨头暂停了 7 nm 以下工艺的研发,转而将目光投向先进封装领域。其中再布线先行( RDL-first ) 工艺作为先进封装技术的重要组成部分,因其具备高良率、高密度布线的优势吸引了大量研究者的目光。总结了 RDL-first 工艺的技术路线及优势,详细介绍其工艺进展,模拟其在程序中的应用,并对 RDL-first 工艺的发展方向进行展望,为 RDL-first 技术的进一步优化提供参考。1 引言 随着芯片重构工艺的不断迭代,封装技术已经成为了半导体产业的关键核心,而超高密度的先进扇出(Fan-out)技术也在其中起到了更加重要的作用。该封装手段主要分为以下类别:安装芯片后布线 / 芯片凸点向下(Chip-first/Face-down)、安装芯片后布线 / 芯片凸 点 向 上 (Chip-first/Face-up) 以 及 再 布 线 先 行(RDL-first)。前两种封装工艺需要在芯片表面完成布线,而 RDL-first 工艺是在载片上完成布线后进行芯片倒装,可以实现更小的线宽线距和更高的封装良率。封装厂商如果要做出更加精良的扇出型封装,RDL-first 工艺具有明显优势。自从 NEC Electronics Corporation(现在的 Renesas Electronics Corporation)开发出 RDL-first 工艺以来 [1-2] ,这一技术飞速发展并实现了大量应用,例如 Amkor 公司在 2015 年和 2017 年 [3]开发的 SWIFT TM 和 SLIM TM 工艺。随后,台积电和三星电机先后推出了 RDL-first 封装方案,并且向着板级和2 μm 线宽线距工艺进发。长电科技于 2021 年 7 月在国内率先推出了使用 RDL-first 形式的高密度扇出式封装(XDFOITM-FcBGA-H),目前正处于快速追赶阶段。由于具有更高的封装良率和布线密度,RDL-first工艺更加适用于多芯片、大尺寸的高密度扇出封装,例如处理器、存储芯片的封装等,随着 5G、人工智能等技术的发展,其应用也更加广泛。本文对 RDL-first 工艺进行了详细的介绍,包括其工艺路线、应用、仿真以及未来发展趋势。 2 RDL-first 工艺的介绍 2.1 RDL-first 工艺路线 常见的 RDL-first 工艺路线共有三种,分别为:1)使用物理气相沉积(PVD)制备介质层和 Cu 布线层,并通过机械研磨除去载片;2)以玻璃载板为介质层,通过电镀 + 刻蚀完成再布线层(RDL)布线,然后通过激光解键合去除载片;3)将前两种方法混合使用,这种方法更适用于较为复杂的芯片结构。 使用 PVD 进行 RDL-first 扇出的过程如图 1 所示。首先使用 PVD 在 Si 片上形成 SiO 2 (或 SiN)薄层,然后使用离子刻蚀(RIE)完成图形化,随后进行 Ti、Cu溅射以及 Cu 沉积,接着通过化学机械抛光(CMP)工艺得到第一层与 Si 片相连的 RDL,重复以上步骤可以得到更多的 RDL。当所有 RDL 制备完成后,通过底部凸块金属化(UBM)结构连接芯片,使用 PVD 完成的 RDL-first 工艺样品的切片扫描电子显微镜(SEM)结果如图 2 所示。该方法使用的载板是 Si 片,在上述步骤完成后还需通过机械研磨去除载板并在磨出的焊盘上完成植球。这一工艺目前已较为成熟,但是对设备要求较高且造价高昂,因此已逐渐被第二种方案取代。   在玻璃载板上完成 RDL-first 工艺的关键步骤如图 3 所示。首先在玻璃载板上涂抹一层牺牲层(通常使用激光释放材料),然后在牺牲层上完成 UBM 结构和 RDL 的制备,接着在顶层进行芯片倒装、底填以及塑封等工艺,最后完成激光解键合和植球。这种方法较为简单,但是玻璃载板的引入提高了对封装过程中翘曲控制的要求。  第三种方法混合使用了前两种制备工艺。首先使用第二种工艺,在玻璃载板上完成布线、UBM 结构制备,随后将其键合到 Si 片上,去除玻璃载板后使用第一种工艺的 PVD 和电镀技术继续布线,最后再进行芯片倒装和塑封,通常可以实现六层以上的高密度布线。混合 RDL-first 工艺的关键步骤如图 4 所示,这一工艺更适用于复杂的芯片结构,SPIL 和 Amkor 公司都推出过使用这一工艺生产的产品。这种方案成本较高,目前主要应用于研发领域。  上述三种制备方法各有利弊,设计者通常会根据实际情况选择最为合适的工艺路线完成芯片封装。尽管出现较晚,但是 RDL-first 工艺由于其独特优势已在先进封装领域占据越来越重要的位置。 2.2 RDL-first 工艺的特点 RDL-first 工艺最大的优势在于对良率的显著提升。对于传统的 Chip-first 工艺来说,由于已知合格芯片(KGD)已经嵌入,后续加工过程中的各种缺陷都将导致芯片失效,特别是在金属层较为复杂且层数较多的情况下,最终良率往往不能满足要求。而 RDL-first工艺可以首先完成线路排布,通过测试手段选择合适的区域进行芯片倒装,从而实现大幅度提高产品良率的目的,这一工艺对于部分价格昂贵的芯片尤为适用。LUJAN [4] 对 RDL-first 和 Chip-first 工艺进行价格比较,结果表明,在当前的技术条件下,当封装芯片种类大于等于三种时,RDL-first 技术成本更低,因此,RDL-first 工艺目前主要应用于复杂的多芯片封装场景下,随着后续芯片价格的进一步上升以及 RDL-first工艺的不断优化,这一工艺必将获得更大范围的应用。需要指出的是,当单个封装体的芯片数目较少时,RDL-first 工艺以外的键合和解键合步骤将会增加封装成本。此外,RDL-first 工艺多用于来料芯片带球的情况,否则芯片倒装时对位难度较大。 3 RDL-first 工艺的进展 尽管 RDL-first 工艺的开发仅有十余年的历史,但是研究者已经对这一技术进行了大量的探索。 2018 年,ZHU 等人 [5-7] 探究了 RDL-first 工艺中的关键步骤,包括金属层的制备、芯片倒装工艺以及激光解键合的参数等,并通过增加玻璃载片厚度的方式避免晶圆翘曲对布线层产生影响,最终该团队成功制备出线宽线距为 10 μm 的两层 RDL 扇出封装样品并完成可靠性测试。玻璃载片上的布线情况如图 5 所示。  2019 年,HO 等人 [8-9,16] 通过 RDL-first 工艺实现了单边八层金属层的超高密度扇出封装,接触通孔的横截面如图 6 所示。这八层金属层包括七层 RDL 和一层UBM 结构,最细的线宽线距仅为 2 μm。为了实现该方案,HO 等人将介质层厚度从 7 μm 降低到 3 μm,显著改善了翘曲问题。在该工艺条件下,随着加工层数的增加,晶圆翘曲随之增大,最终翘曲仅为 1.33 mm。团队对芯片的电性能进行了测试,相邻信号线之间的最大串扰为-20.5 dB,这表明 RDL-first 工艺在实现超高密度扇出封装中具有优势。  2020 年,LAU 等人 [10,14-16] 在复杂异构集成中使用了 RDL-first 工艺,对方案的设计、材料、工艺、可靠性进行了系统性研究,针对回流过程中的芯片脱落、焊点疲劳寿命较短等问题提出了解决方案,最终通过三层 RDL 和两层 UBM 结构成功实现了三颗不同尺寸芯片的互联与封装,相较于使用 Chip-first 工艺的方案,良率得到了显著提升。 RDL-first 工艺降低成本的关键是选择合适的位置倒装 KGD,因此需要通过电性能测试等手段区分RDL 部分是否存在异常。2018 年,GUNJI 等人 [11-14] 开发出一种通过电容法测试单面开 / 短路的新手段,与常规的四线测试法相比成本降低了 30%,并且可以用于更精细的线路(线宽线距为 2 μm),预计这一测试手段将会助力 RDL-first 工艺进一步应用于超高密度布线方案。 从 2018 年至今,RDL-first 工艺路线快速迭代,良率得到显著优化,生产成本大幅降低,工艺能力稳步提升,可以实现的异构集成尺寸和芯片颗数也大幅增加。目前,优化工艺的常规方法为:1)在作业能力范围内增加载片厚度以显著降低翘曲,从而实现布线层数的增加;2)使用热膨胀系数(CTE)更加匹配的玻璃载片;3)设计布线层的线宽线距不大于 5 μm,通过增加单层布线密度的方式减少总布线层数,从而避免较大的介质层总厚度导致作业困难。但是,由于玻璃是一种非晶材料,其 CTE 往往无法像 Si 片一样与金属层匹配良好,随着金属层复杂性的飞速提升,翘曲问题越来越制约着 RDL-first 工艺的进一步发展。针对这一问题,研究者们通过仿真结合实验不断尝试新的翘曲控制方法。 4 RDL-first 工艺中的翘曲问题 在先进封装制程中,晶圆经历固化、回流等阶段后会积累较大的内应力,主要表现为晶圆的翘曲变形,这不仅影响了封装精度,也会增加工艺难度,带来焊点断裂、裂片等诸多良率损失,这一问题也严重制约了 RDL-first 工艺的应用。国内外研究者使用有限元分析法,通过各种方式减轻 RDL-first 工艺过程中产生的翘曲,从而进一步提升RDL-first工艺的实用价值 [14-20] 。 2017 年,LIN 等人 [21] 通过有限元模拟结合样品制备的方式探究了 RDL-first 工艺中影响翘曲水平的基本因素,包括金属层层数、钝化层与金属层的厚度、芯片布局、塑封温度等。根据仿真结果,LIN 等人优选参数,成功制备出了包含三层金属层的 RDL-first 扇出结构,最小线宽线距为 8 μm,封装体的整体翘曲仅为283 μm,远低于常规水平,这一研究结果为更多金属层的 RDL-first 结构提供了指导。 2018 年,ONOZEKI 等人 [22] 通过有限元分析研究了底部填充体和塑封料对 RDL-first 工艺中晶圆翘曲的影响。结果表明,选择低模量的底部填充体和塑封料可以显著改善翘曲情况。该团队根据计算结果选择了合适的底部填充体和塑封料搭配,成功制备了包含四层金属层的 RDL-first 结构,翘曲水平相较于优化前大幅降低。 2018 年,LIN 等人 [23] 研究了 RDL-first 工艺中倒装芯片的体积对晶圆翘曲的影响。通过实验结合仿真,作者得到了芯片体积 / 塑封料体积与晶圆翘曲的关系函数,如图 7 所示。当比值增大时,晶圆翘曲形式从“笑脸”转变为“哭脸”,这一结果有助于 RDL-first 工艺路 线优化,后续研究者可以通过计算定性判断晶圆翘曲的状态,避免无法实际作业的情况。  2020 年,CHE 等人 [24] 详细探究了 RDL-first 工艺中的激光释放材料、玻璃载片以及塑封料选择对翘曲情况的影响,并对所有影响因素进行整合。通过有限元分析结合实验数据的方法,CHE 得出结论:1) 增加玻璃载片的厚度可以显著降低翘曲;2)当玻璃载片与钝化层、塑封料的 CTE 匹配时翘曲较小;3)通过增大玻璃载片尺寸可以缓解翘曲问题。不同工艺条件下晶圆的翘曲结果如图 8 所示,其中实验条件选择见参考文献[24]。  5 RDL-first 工艺的发展方向 由于工艺成熟度的逐步提升,RDL-first 工艺的应用空间正在进一步拓展。除了金属层层数的增加、线宽线距的进一步缩小等先进扇出封装发展方向外,RDL-first 工艺还有几项较为重要的研究方向,以下主要介绍激光释放材料的优化、面板级工艺、优化载片三个方面 [25-28] 。 5.1 激光释放材料的优化 RDL-first工艺目前常用的激光缓释材料的主要成分为聚酰亚胺,其固化温度在 400 ℃左右 [29] ,并且需要配合黏合剂使用,这一特性显著提高了成本。2018年,ZHANG 等人 [30] 开发出两种新型激光释放材料,这两种材料具有更低的玻璃化转变温度,不需要额外加入黏合剂,适用于当前主流的载片材料。这两种激光释放材料的固化条件如表 1 所示,在 150 ℃和 100 ℃下,A、B 材料仅需 2 min 就可以完成固化,并且具有出色的耐化性和可靠性。这一结果对RDL-first 工艺应用空间的拓展有积极意义。  2022 年,LEE 等人 [31] 通过研究激光烧蚀后激光释放材料的表面性状,评估了四种激光释放材料的最优解胶工艺,并且实现了玻璃晶圆的循环使用,极大地降低了 RDL-first 工艺的成本。不同胶材的解胶能量以及解胶效果如图 9 所示,可以看出,所有样品的解胶效果完好,载片与塑封片均未出现明显的污染情况,载片经过清洗后可以再次使用。  5.2 面板级工艺 先进封装工艺中降低成本尤为重要。通常情况下,晶圆级封装的面积使用率远小于面板级封装,使用面板完成先进封装工艺可以大幅降低成本 [32-35] 。因此,研究者们在对 RDL-first 工艺路线的探索中不断尝试使用玻璃面板替代玻璃晶圆,另一方面,玻璃面板的尺寸也在不断增加,玻璃面板尺寸的变化如图10所示 [24] 。  2017 年,KO 等人 [36] 使用聚合物薄膜作为临时键合层,在玻璃面板上实现了芯片与 UBM 结构的Cu-Cu 键合,并且通过低能量的激光(功率为 5 W)照射键合层,成功将薄膜与玻璃载体分离,玻璃面板激光解键合前后的效果如图 11 所示。可以看出,玻璃面板的引入显著增加了面积使用率,最终解胶效果良好,低能量激光避免了对芯片的损伤。  2019 年,YANG 等人 [37] 在玻璃面板上通过 RDL-first 工艺进行布线并完成了低温 Cu-Cu 焊接,芯片与玻璃面板的结构如图 12 所示,其焊接温度仅为220 ℃,显著降低了工艺成本并提高了可靠性。  5.3 优化载片 在前文的介绍中,几乎所有的实验都使用玻璃作为载片完成 RDL-first 工艺,然而,CTE 的不匹配以及激光烧蚀的过程严重限制了玻璃晶圆材料的选择。因此,部分研究者尝试使用其他材料替换玻璃晶圆作为载片 [38-39] 。 2017 年,TANG 等人 [40] 通过喷射气流完成解胶,成功在 Si 片上完成了 RDL-first 工艺全流程。与激光烧蚀的过程不同,气流解胶是在载片与布线层之间引入气流,从而驱使两者发生分离的解键合手段,图 13为气流解胶过程示意图,整个解胶过程在室温下完成。由于 Si 片的 CTE 与金属层更加匹配,这一工艺在降低成本的同时显著减轻了翘曲。解胶完成后,TANG等人对封装体进行了功能测试,结果表明,钝化层、金属层以及塑封料均保持外形完整,无明显缺陷,电路功能未出现异常。  随着现代医学的飞速发展,需要部分芯片具备可穿戴甚至是可植入的功能,因此柔性芯片也是当前研究的热点 [41-46] 。在 RDL-first 工艺路线中,研究者们开始尝试使用柔性载片完成封装过程,最终实现了异质芯片的同步柔性。2020 年,TAKAHASHI 等人 [47] 开发出一种基于水凝胶载片的 RDL-first 工艺,金属层使用Au 以确保良好的柔韧性,图 14 是柔性 RDL-first 工艺示意图。最终完成的封装体在弯曲半径为 40 mm 时仍可以实现完整功能,该弯曲半径已经可以满足绝大多数穿戴或植入式芯片的要求。该团队还对芯片的生物兼容性、物质渗透性以及疲劳寿命进行了测试,结果表明,该封装手段可以应用于生物医学嵌入式电路的制备。  6 结束语 随着芯片成本以及封装难度的增加,RDL-first 工艺路线在先进封装中的优势愈发明显,主要表现为:1)可以实现多层超高密度布线;2)具有更高的良率和更低的成本,更加适用于当前的多芯片集成场景;3)可以实现柔性封装。因此,尽管 RDL-first 工艺的开发仅有十余年历史,但研究者们在工艺路线优化、材料选择、翘曲控制等方面已经进行了大量的实验并取得了一系列成果。然而,对 RDL-first 工艺在可靠性和稳定性方面的研究目前还不充分,亟待研究者们进一步深入探索。可以预见,随着摩尔定律逐步达到极限,当芯片的刻蚀尺度难以进一步缩小时,使用 RDL-first 等先进封装手段实现芯片互连将成为系统级集成的重要解决方案。 |