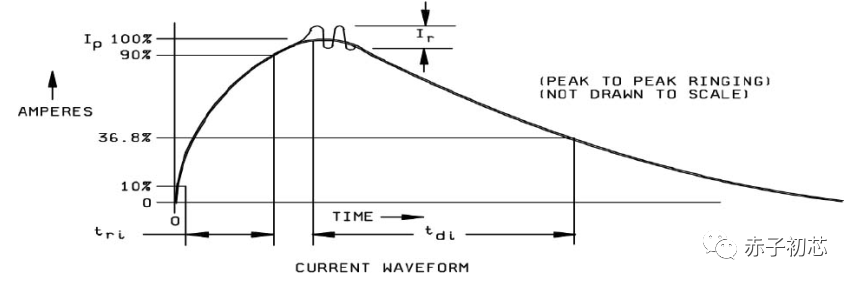

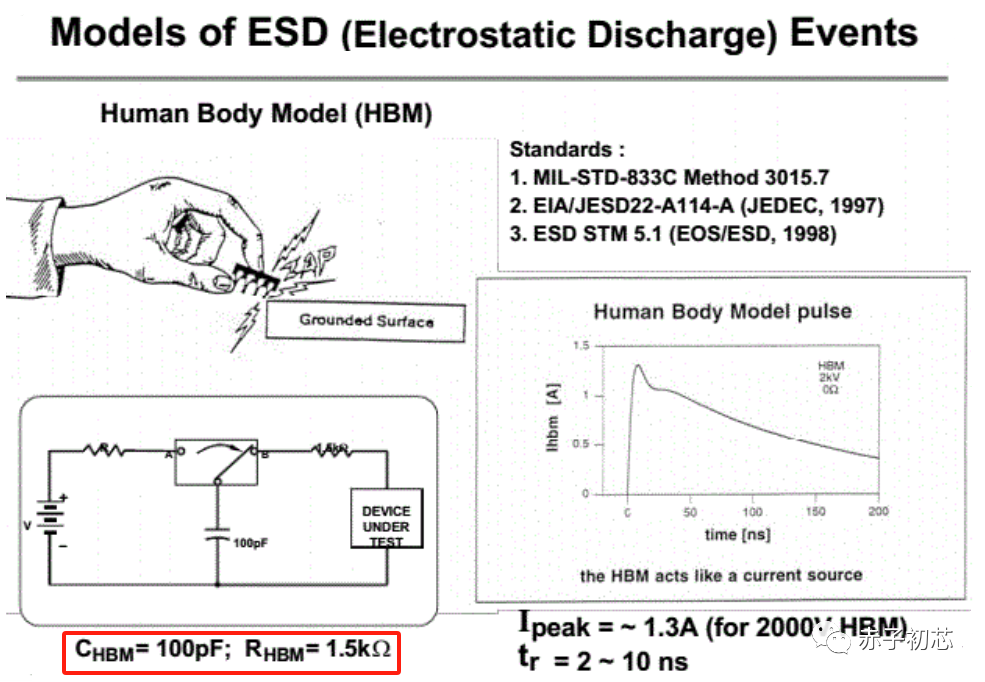

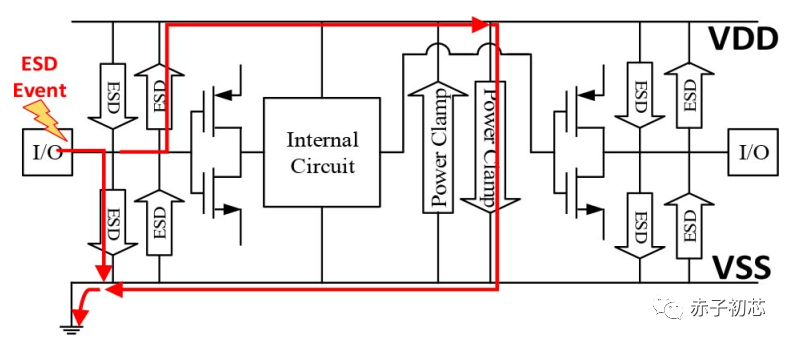

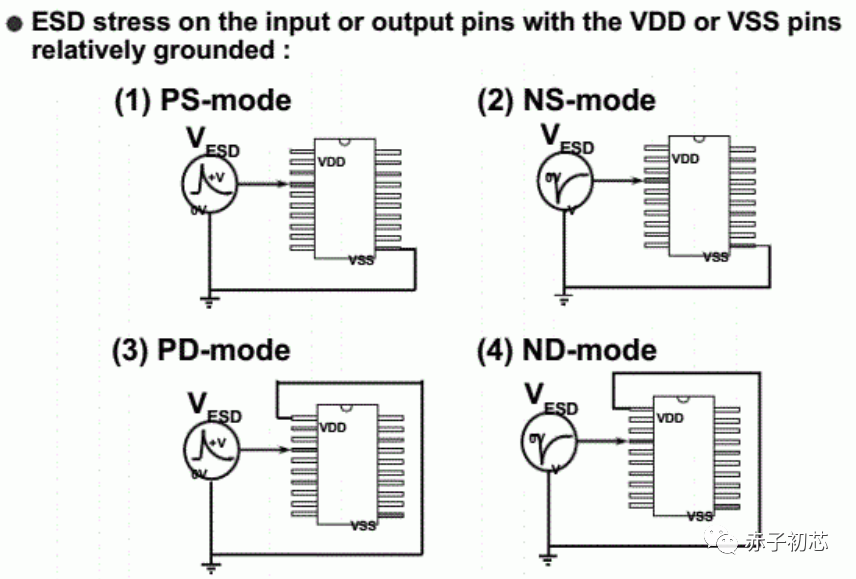

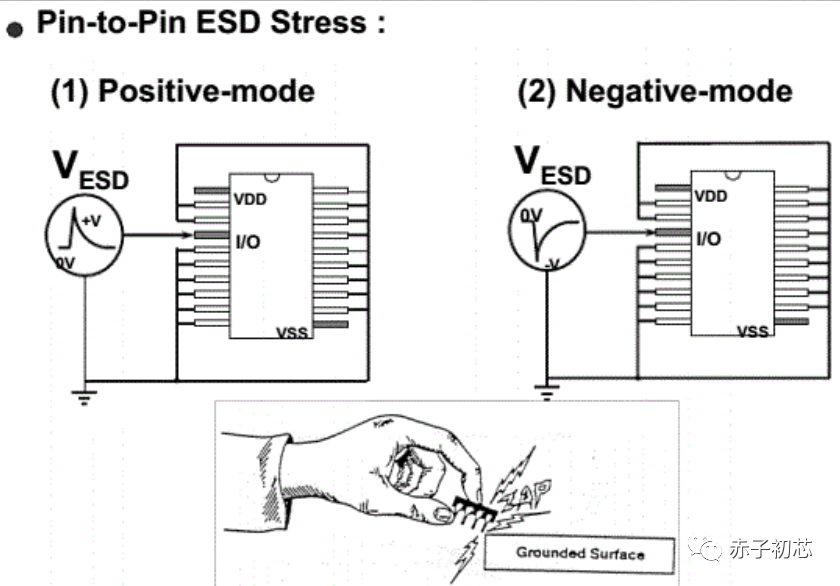

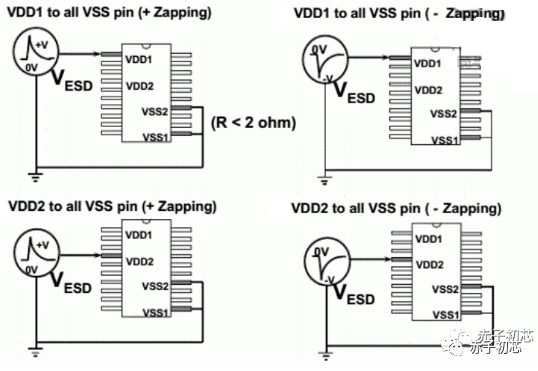

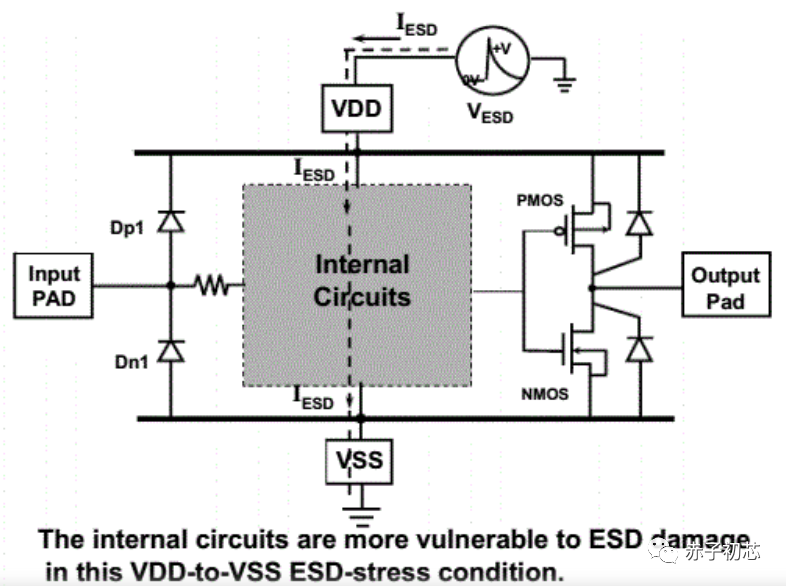

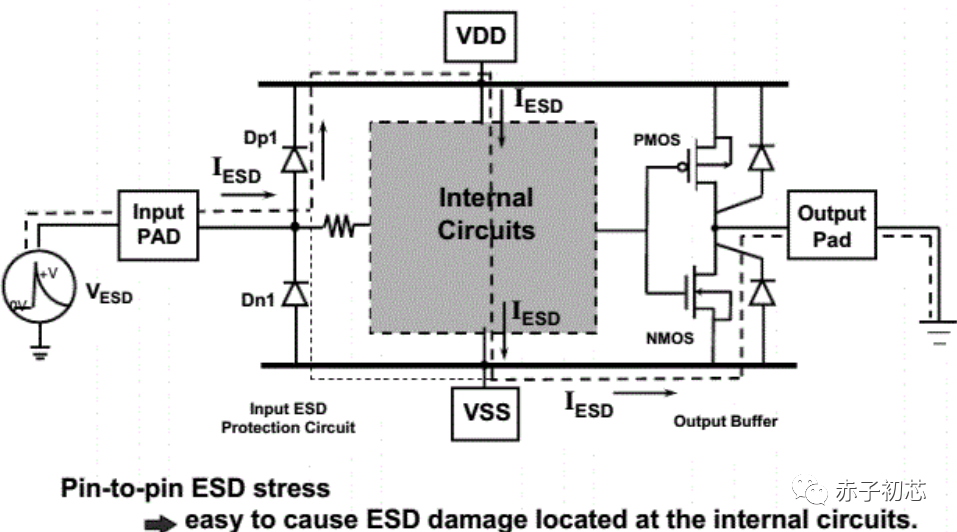

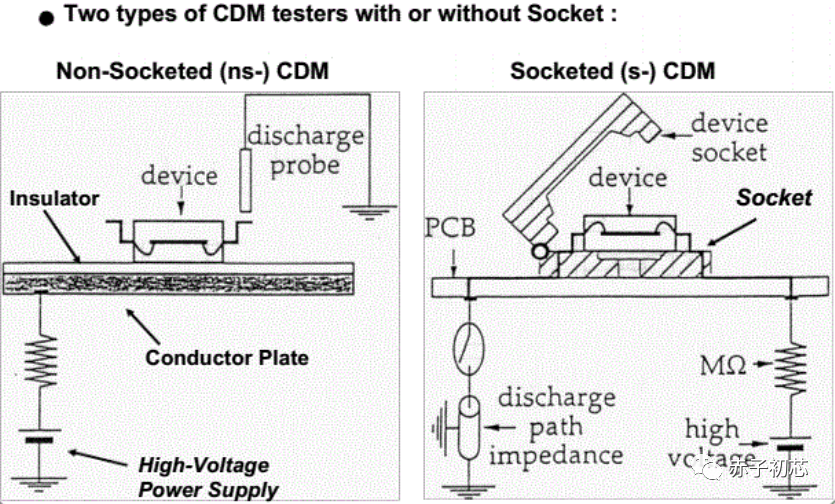

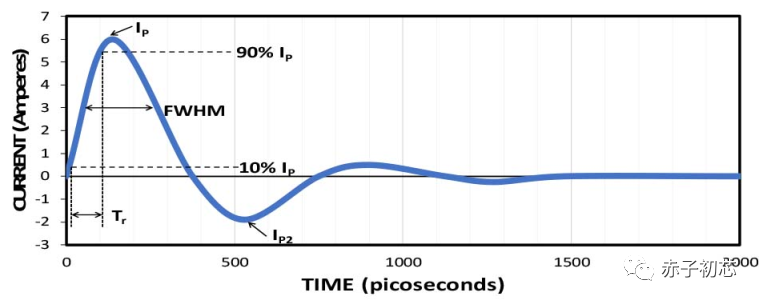

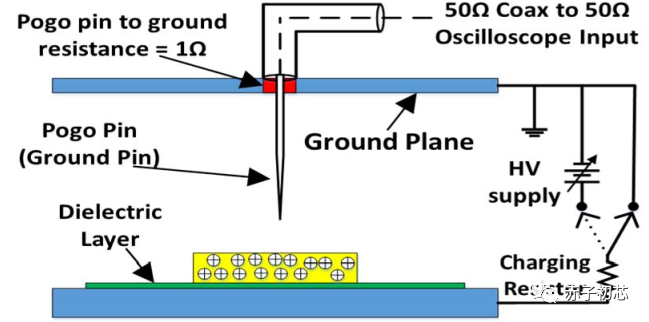

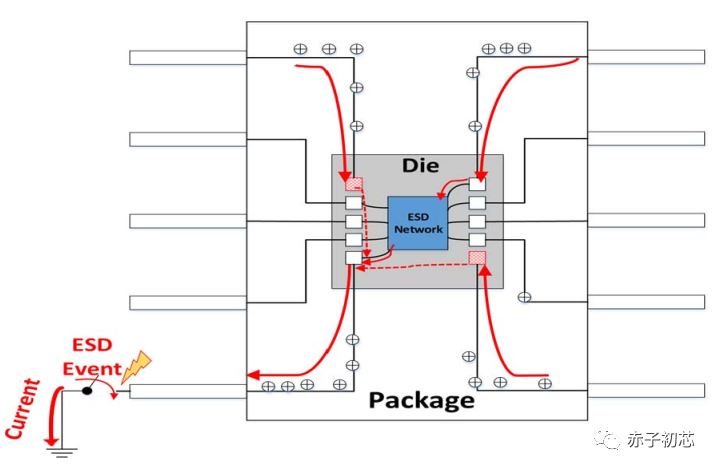

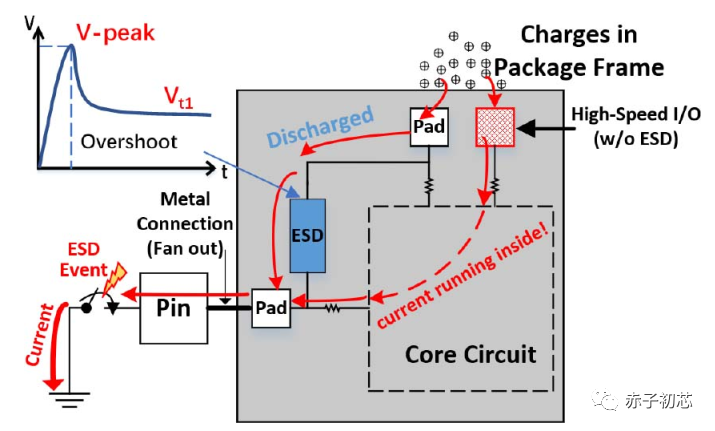

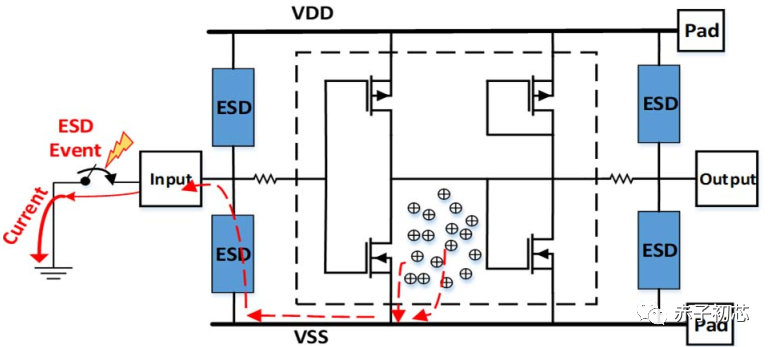

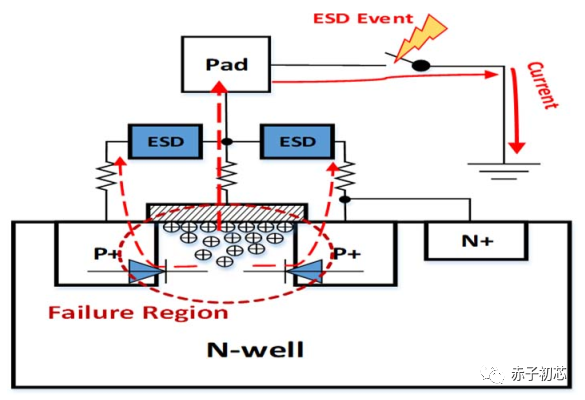

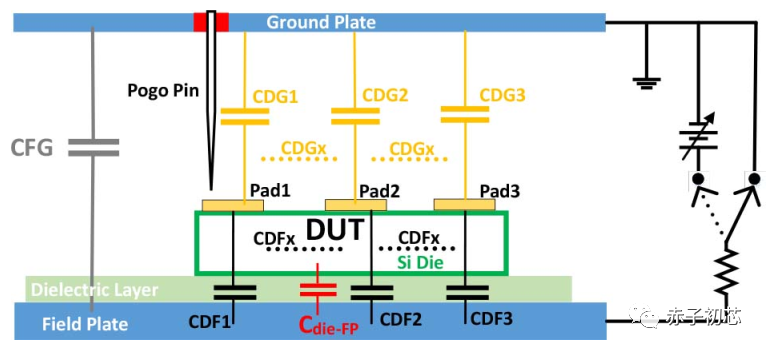

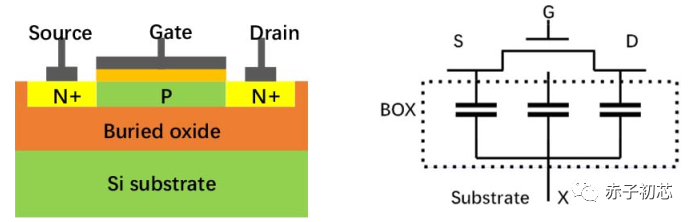

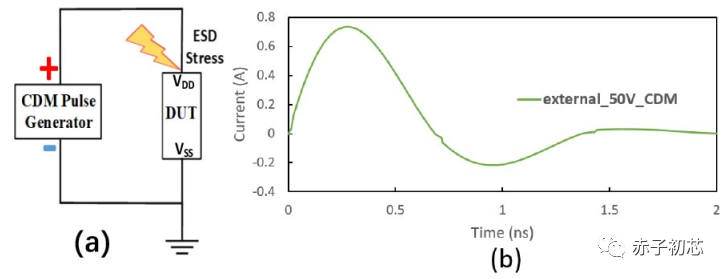

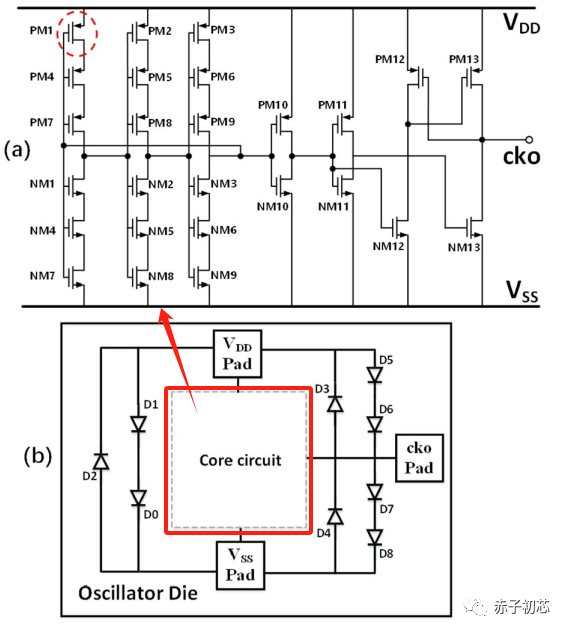

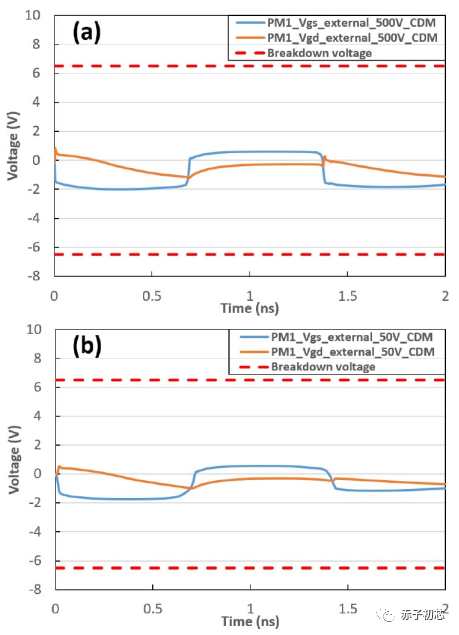

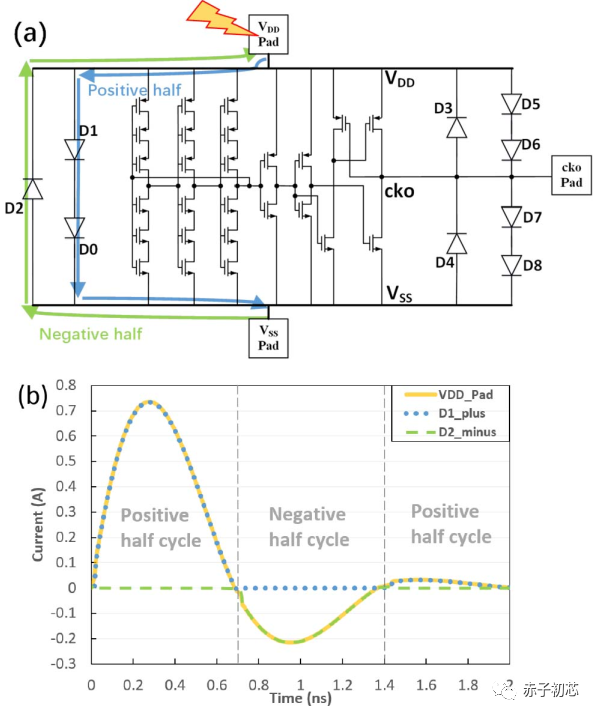

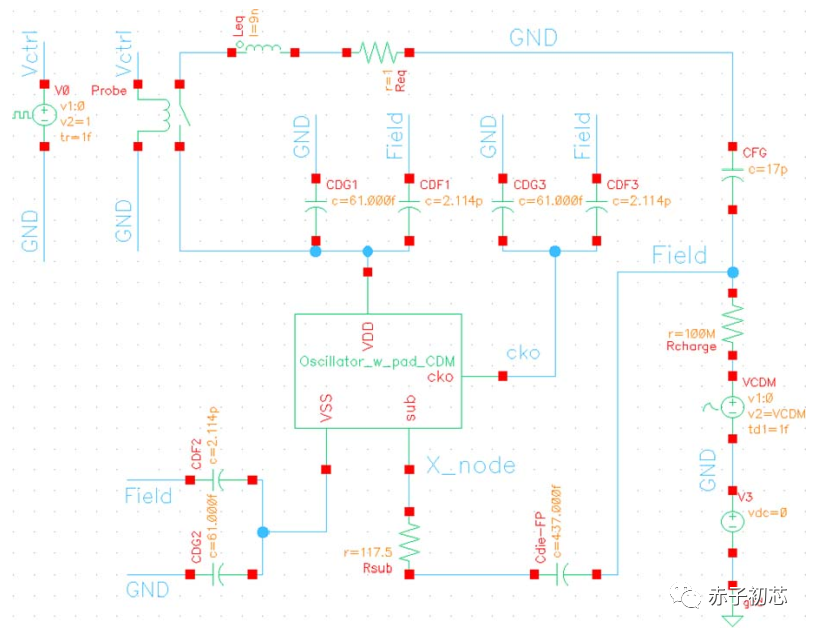

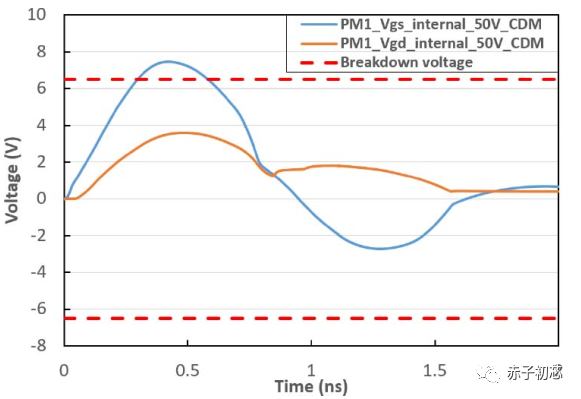

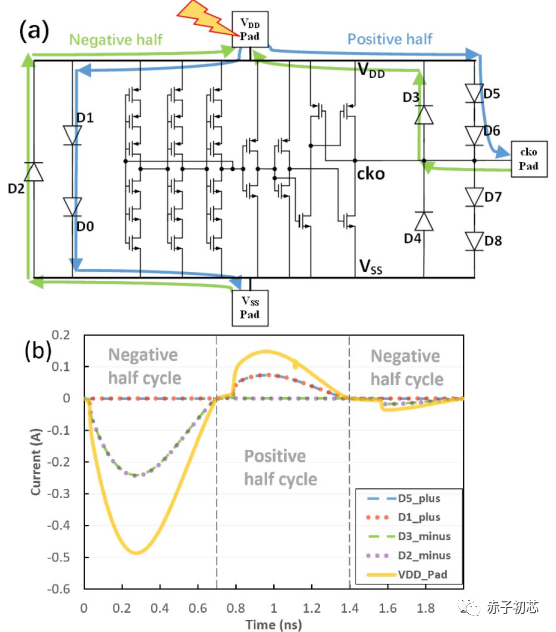

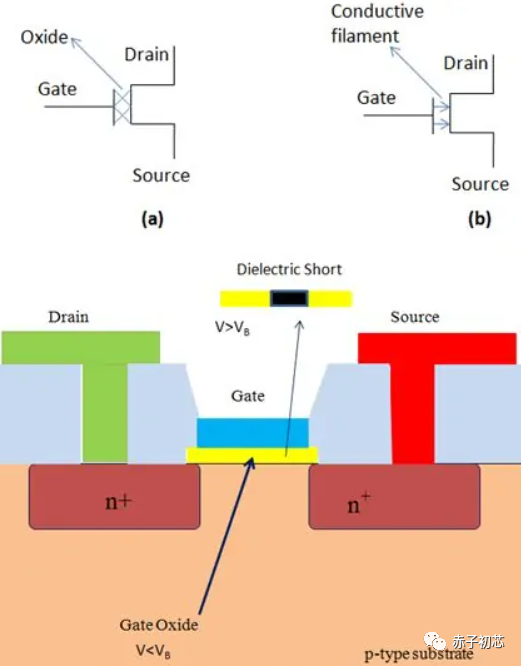

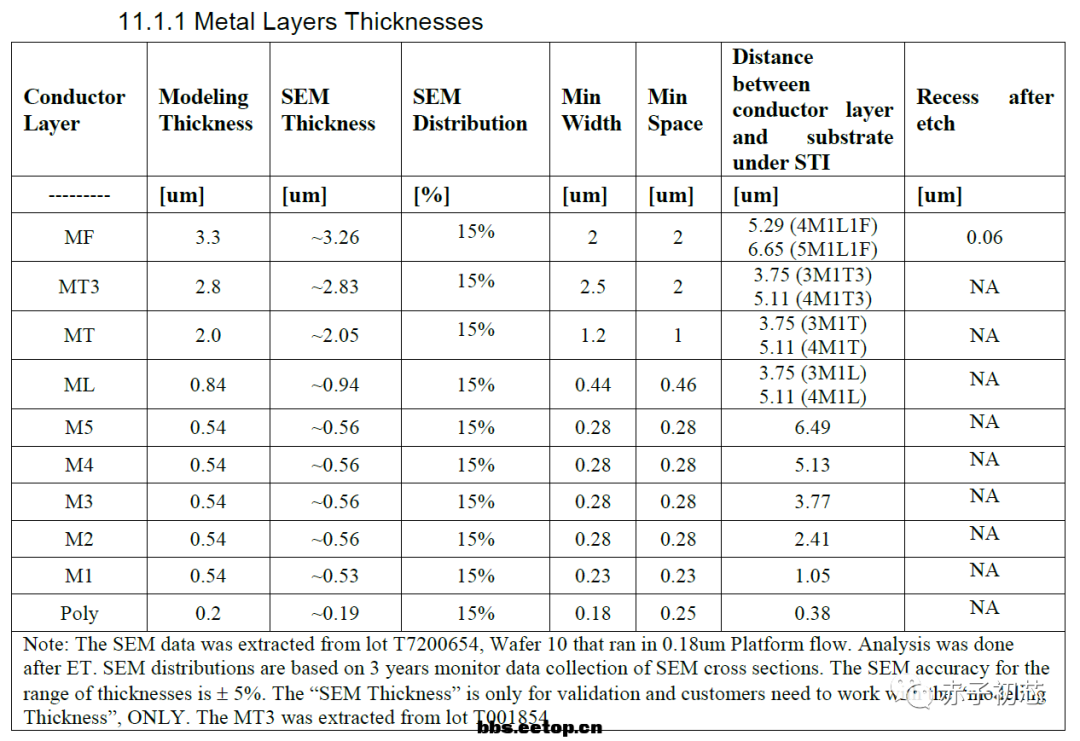

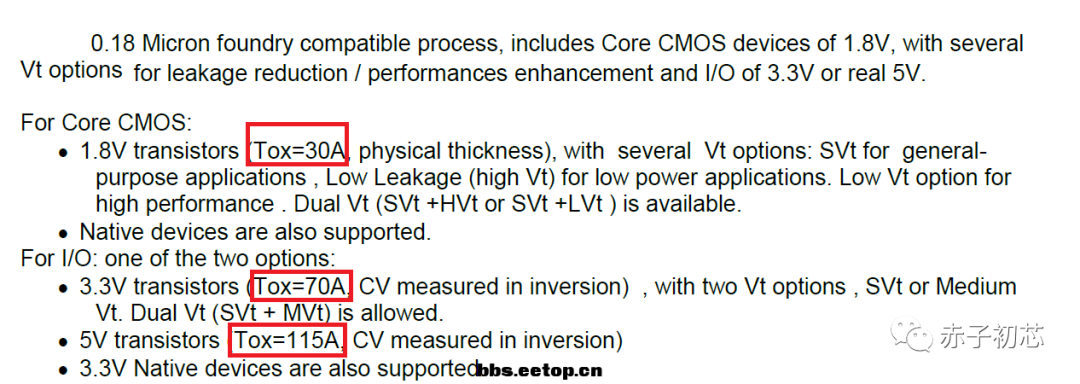

通常用于“从外部到内部”HBM ESD保护,理论上不适用于“从内部到外部”CDM ESD保护,常见的基于焊盘的CDM ESD保护设计具有随机性和不确定性。HBM ESD是一种“面向外部”的ESD现象,人体内积聚的静电通过芯片焊盘在触摸芯片时放电到IC芯片中。其标准模型如下,  图 HBM ESD波形  图 HBM模型 HBM脉冲的关键参数是波形上升时间tr(~10ns)和衰减时间td(~150ns)。HBM ESD保护需要仔细设计ESD关键参数,包括触发电压(Vt1)、触发时间(t1)和放电电阻(RON)。理论上,基于焊盘的ESD保护方法是一种“从外部到内部”的ESD保护方式,其中焊盘处的ESD器件充当焊盘处的“防护装置”。  图 常见HBM防护电路     图 HBM&MM放电测试   图 HBM ESD如何破坏芯片 CDM ESD本质上是一种“内部导向”事件,与“外部导向”HBM事件完全不同。CDM ESD是一种自充电/放电ESD现象,芯片通过各种可能的机制(摩擦电或场感应)充电。感应的静电电荷以随机和分布式的方式存储在芯片内部。当IC接地时,存储在内部的静态电荷将放电到地。  图 CDM测试   图 CDM波形 CDM ESD标准(ANSI/ESDA/JEDEC JS-002-2014)提供了构建场感应CDM(FICDM)ESD测试仪的细节,包括两个步骤:1)通过场感应对IC部件充电;2)通过使用pogo引脚接触被测器件使其接地,使被测器件(DUT)放电。因此,存储在DUT内部的静电荷将放电到地中,这显然是一个“从内部到外部”的过程,不同于“从外部到内部”的HBM ESD事件。CDM和HBM ESD事件在性质上的巨大差异表明,它们的ESD保护方法也应不同。在使用基于FICDM的CDM测试器的充电过程中感应到DUT器件中的电荷可能不会像在现实世界中那样完全分布在整个IC芯片中,因此,导致CDM ESD故障的很大变化。CDM ESD故障可以发生在任何级别:裸硅管芯、封装IC或系统模块。  图 FICDM CDM ESD test set-up 基于焊盘的CDM ESD保护方法存在根本缺陷,导致了观察到的CDM ESD设计失败的不确定性和随机性。首先,由于有问题的静态电荷已经留在IC部件内,焊盘上的ESD器件失去了其“保护”功能。其次,从理论上讲,由于存储在芯片内部的电荷在被放电到GND之前必须穿过电路,因此CDM损坏很可能由于电压或电流积聚而发生在芯片内部的某个地方,CDM故障取决于CDM放电过程中的内部电流路径。 完整的全芯片ESD保护需要一个由每个焊盘上的ESD器件组成的全局ESD保护网络,每两个焊盘之间总是有一个低电阻ESD放电路径,使用HBM&MM。全芯片ESD保护网络可能存在于芯片上,对于CDM-charged封装芯片,静态电荷通常被认为存储在封装框架或电源总线上,封装上存储的电荷将始终能够找到一种方式放电到接地引脚中,要么直接通过位于附近的封装金属总线,要么通过连接到芯片上焊盘的全局ESD保护网络,然后放电到接地引脚中,如下图所示。  图 CDM-charged封装芯片 ESD放电示意图 从IC管芯的角度来看,封装IC的CDM ESD事件类似于封装内IC管芯“从外部到内部”的HBM ESD事件。因此,理想情况下,基于焊盘的HBM ESD保护方法应适用于CDM ESD事件中的封装IC。在实际ESD设计中常见的是,ESD器件可能无法在两个方向上针对ESD关键参数(t1、Vt1、RON等)进行优化,一些ESD器件无法在正向或反向打开。因此,随机存储在封装框架上的电荷将不可避免地流入内部核心电路,导致内部CDM ESD损坏,即使电荷最终将被释放到接地的封装引脚中。在另一种情况下,对于高频、宽带宽IC或高数据速率IC,信号焊盘通常不受ESD保护,以避免ESD引起的寄生效应,这将影响高速IC的性能,如下图所示。在这种情况下,ESD保护网络是不完整的。因此,在CDM ESD作用下,存储在封装框架上的电荷将在到达封装GND的途中进入内部核心电路的情况,导致CDM ESD对核心电路的损坏。  图 存储在封装框架内的电荷进入无ESD保护的高速IO口 未封装裸IC管芯的CDM ESD问题与封装IC相比更具破坏性,如下图所示,对于裸Si管芯,任何因素引起的电荷随机存储在IC管芯内的任何地方,例如,在衬底中、沿着金属走线等存储到晶体管。经典的基于焊盘的ESD保护方法根本无法为裸IC管芯提供CDM ESD保护。在电荷存储在GND焊盘(例如VSS)附近的情况下,可以通过靠近焊盘的ESD器件将电荷安全地释放到附近的地中。不幸的是,对于复杂芯片来说,可能大量电荷随机分布在管芯上的各处,这些管芯必须在CDM ESD下找到通向接地焊盘的路径。  图 经典pad-based ESD保护电路 下图显示了一种情况,在CDM放电时,本地存储的电荷可能通过栅极电容耦合到焊盘,从而不可避免地对栅极造成CDM ESD损坏。ESD故障归因于CDM应力期间金属栅极的电压过大。CDM感应的电荷很可能被存储并局部限制在MOSFET中,在CDM ESD应力下,一些电荷将不可避免地穿过S/D结或栅极,导致CDM ESD损坏,无论焊盘是否受到ESD保护。即MOSFET在放电过程中很可能穿过局部栅极,并导致栅极损坏,即使所有焊盘都受到设计的ESD保护。随机CDM ESD故障对于SOI芯片来说变得更糟,每个MOSFET与电路的其余部分隔离。  图 MOS由于自身存储的大量静态电荷通过漏源栅释放产生ESD损坏 过于简化的FICDM测试电路模型无法准确地对真实世界的CDM事件进行建模,因为集总电容电路根本无法反映DUT IC内CDM电荷存储的完全分布性质,因此导致现场CDM测试的主要不确定性。为了解决这个问题,采用一种新的伪分布式等效电路模型,用于FICDM CDM测试,如图所示。  图 伪分布式等效电路模型 在新模型中,CDG被认为是跨所有IC焊盘的分布式电容器网络(CDG1、CDG2…CDGx),在一阶近似中,假设所有焊盘相同,则每个焊盘的电容器网络可以相等。Cdie−FP表示从管芯衬底到场板的电容,CDF表示从每个焊盘到场板之间的电容。之所以称作伪分布式FICDM测试模型,因为电容网络在很大程度上取决于与DUT相关的电容网格有多细包括跨所有封装焊盘的分布式电容(CDF1、CDF2……CDFx)。下图45nm SOI MOSFET,其中与掩埋氧化物(BOX)层和衬底节点“X”相关的电容包含在PDK中,避免了建模所需的额外工作。  图 SOI截面图及主要电容分布  图 击穿相对于VSS焊盘的VDD焊盘,外部CDM脉冲施加到管芯  图 ESD防护电路实例 简单ESD失效标准:MOSFET的栅极击穿电压(|VGS|或|VGD|),在2ns的CDM脉冲周期内,假设不超过6.5V。使用不同电压和电流的CDM ESD脉冲来对管芯进行电击,下图表明在500V和50V CDM跳变下,不会发生CDM诱导的MOSFET击穿,表明随着CDM从50V增加到500V,峰值瞬态VGS和VGD略有增加,这意味着基于焊盘的ESD保护在抵御外部定向ESD效果良好。  图 PM1的VGS和VGD的示例性瞬态电压  图 使用外部50V CDM脉冲对VDD焊盘进行电击: (a)CDM ESD放电路径,(b)瞬态CDM电流波形 从上图可以看到,由于CDM放电波形振荡,两个CDM放电路径交替开启:正循环期间的D1+D0路径和负循环期间的D2路径。  Figure. A schematic deck used to simulate the oscillator under CDM ESD stressing due to internal charges where “VDD” padis zapped 上图模拟了从内部到外部的FICDM ESD电击(伪分布式等效电路模型),芯片通过感应充电,然后通过VDD焊盘接地放电。其中,“GND”和“Field”分别表示接地板和场板,“sub”是MOSFET的“X”节点。当pogo引脚接近DUT焊盘时,电压控制开关模拟火花。电压源VCDM是FICDM充电电压。电压源V0控制开关以触发CDM放电。下图描绘了示例MOSFET PM1在FICDM跳变下瞬态CDM放电电压波形,CDM故障发生在一些MOSFET上,例如PM1处的VGS击穿。  图 PM1的VGS和VGD的示例性瞬态电压  图 VDD焊盘被来自每个FICDM模型的内部电荷的CDM脉冲击穿: (a)CDM放电路径,和(b)瞬态CDM电流波形 从上图可以看到,由于CDM放电波形振荡,四条CDM放电路径交替导通:正循环期间的D1+D0路径(VDD到VSS)和D5+D6路径(VDD到cko),负循环期间的D2路径(VSS到VDD)和D3路径(cko到VDD)。由于内部电荷存储的分布式性质,静态电荷可能停留在IC核心内的任何地方。具体而言,在VSS焊盘和cko焊盘附近累积的电荷将找到不同的放电路径。因此,流经芯片内不同路径的放电电流会在不超过50V ESD水平下导致内部CDM故障。显然,“从外部到内部”的CDM电击方法高估了ESD能力(超过500V),而“从内部到外部”的FICDM电击显示内部CDM在低得多的ESD水平下失效。在不考虑存储在IC管芯内的电荷的情况下,可以使用分布式管芯电容网格进行建模,不过即使是增强的FICDM模型也仍然相当于对“由外向内”的CDM事件。由于IC核心内部静态电荷的内部分布在其寿命期间可能是随机的,因此无论现有FICDM测试方法的内部测试结果如何,实际的现场CDM故障都是不可预测的。 IC器件内部积累的电荷,无论在其寿命期间以何种方式,都可能随机分布在整个芯片中,这无法通过过于简化的集总FICDM模型进行建模。内部分布的电荷可以通过IC管芯内的分布式电容网络来建模。CDM故障与IC管芯内累积电荷的内部分布密切相关,并且集中FICDM测试模型被过度简化。对于所有焊盘都由ESD器件保护的IC管芯,使用集中FICDM跳变模型所预测的ESD水平偏高。 补充1:MOS管击穿电压 MOS管的击穿电压是由其结构和材料决定的。MOS管的击穿电压主要分为两种:漏极-源极击穿电压BVDS和栅极-源极击穿电压BVGS。 MOSFET产生漏源击穿的机理有两种:一是PN结的雪崩击穿,二是漏源两区的穿通。当源极与衬底相连时,漏源电压VDS对漏PN结是反向电压。当VDS增加到一定程度时,漏PN结就会发生雪崩击穿。雪崩击穿电压大小由衬底掺杂浓度和结深决定。在结深为1~3um的典型MOSFET中,漏源击穿电压BVDS的典型值只有25~40V,远低于PN结击穿电压的理论值,这是由于受到了由金属栅极引起的附加电场的影响。 MOSFET的金属栅极一般覆盖了漏区边缘的一部分,如果金属栅极的电势低于漏区的电势,就会在漏区与金属栅极之间形成一个附加电场。这个附加电场使栅极下面漏PN结耗尽区中的电场增大,因而击穿首先发生在该处。 如果MOSFET的沟道长度较短而衬底电阻率较高,则当VDS增加到某一数值时,虽然漏区与衬底间尚未发生雪崩击穿,但漏PN 结的耗尽区却已经扩展到与源区相连接了,这种现象称为漏源穿通。发生漏源穿通后,如果 VDS继续增加,源PN结上会出现正偏,使电子从源区注入沟道,这些电子将被耗尽层区内的强电场扫入漏区,从而产生较大的漏极电流。使漏源区发生穿通的漏源电压称为穿通电压,沟道长度越短,穿通电压就越低。源漏穿通限制了MOSFET的沟道长度不能太短,否则会使BVDS降得太低。源漏击穿电压是由漏PN结雪崩击穿电压和穿通电压两者中的较小者决定的。 补充2:MOS管发生击穿的原因 MOS管一个ESD敏感器件,本身输入电阻很高,而栅源极间电容又非常小,所以极易受外界电磁场或静电的感应而带电,又因在静电较强的场合难于泄放电荷,容易引起静电击穿。 静电击穿一般分为两种类型:一是电压型,即栅极的薄氧化层发生击穿,形成针孔,使栅极和源极间短路或者使栅极和漏极间短路; 二是功率型,即金属化薄膜铝条被熔断,造成栅极开路或者是源极开路。(电压型击穿导致短路,功率型击穿导致开路) MOS电路输入端的保护二极管导通时可能出现过大瞬态输入电流,应串接输入保护电阻。由于保护电路吸收的瞬间能量有限,太大的瞬间信号和过高的静电电压将使保护电路失去作用。 MOS是电压驱动元件,对电压很敏感,悬空的G很容易接受外部干扰使MOS导通,外部干扰信号对G-S结电容充电,这个微小的电荷可以储存很长时间。MOS管漏源之间接电阻的作用:保护栅极G、源极S,场效应管的G-S极间的电阻值是很大的,这样只要有少量的静电就能使G-S极间的等效电容两端产生很高的电压,这时栅极与源极之间加的电阻就能把上述的静电泻放掉,从而起到了保护场效应管的作用。 补充3:栅氧化层 为了有效地抑制短沟道效应,并保持良好的亚阈值斜率,栅氧化层厚度要和沟道长度以同样的比例下降。  图 MOS管截面图 众所周知多栅氧工艺(multiple gate oxide)中不同电压类型的管子的栅氧厚度是不同的,鉴于多晶硅后续还要做CMP,那么不同电压类型的管子多晶硅栅的厚度是不同的? 可以通过查询实际的poly厚度和栅氧厚度来理解:1、因为poly厚度的精度差,栅氧厚度控制的精度高,而poly厚度远远大于栅氧,所以栅氧厚度不同对poly厚度的影响很小;2、下图为某0.18微米BCD工艺中的参数,poly厚度在model中取0.2um=2000Å(1nm=10Å),SEM实测~0.19um,SEM分布15%。而1.8V、3.3V、5VMOS的栅氧Tox分别是30Å、70Å、115Å,工艺节点越先进,栅氧越薄,而poly厚度不会下降很多;3、poly厚度受到CMP影响小。   栅长不是受栅极电阻决定的:比较1.8V和5V器件的栅电阻由于栅氧厚度影响导致的电阻差异,假设W=5um,L=0.5um,栅极poly电阻为10个方块(这种按照线性近似了),硅化的poly方块电阻一般在10欧姆/方块之内,这里取10,总电阻大概100欧姆,栅氧厚度带来的差异: 1.8V:30Å/2000Å*100Ω=1.5Ω, 5V:115Å/2000Å*100Ω=6Ω,这点差别能有什么关系呢?连接栅极连线跳线时加了一个通孔,电阻就上来了。如果提到另一层次的问题,最小栅长是受什么影响的,那就复杂了,为了提高密度,降低成本,工艺工程师们孜孜不倦降低各种尺寸,典型的是最小栅长。但是随着器件的特征尺寸不断缩小,出现了许多问题,热载流子注入,短沟道调制,亚阈值漏电流(沟道离子注入/晕环halo/口袋pocket)等。 |