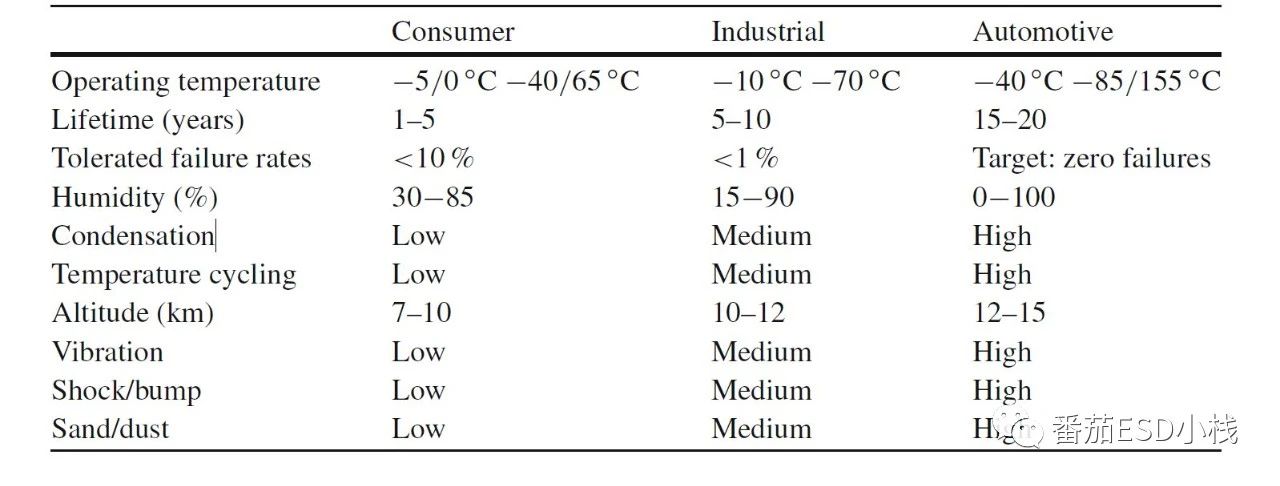

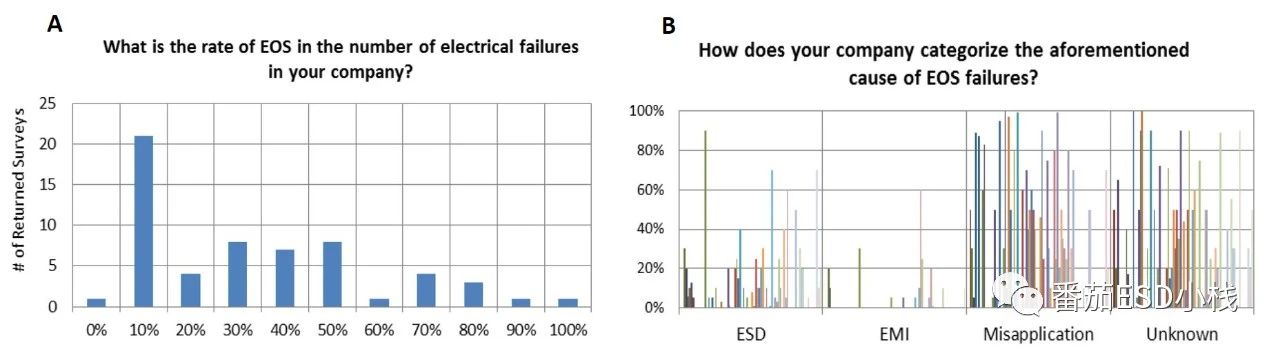

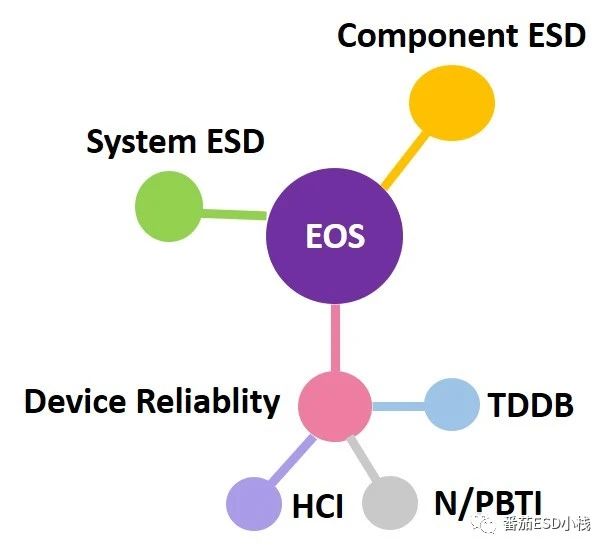

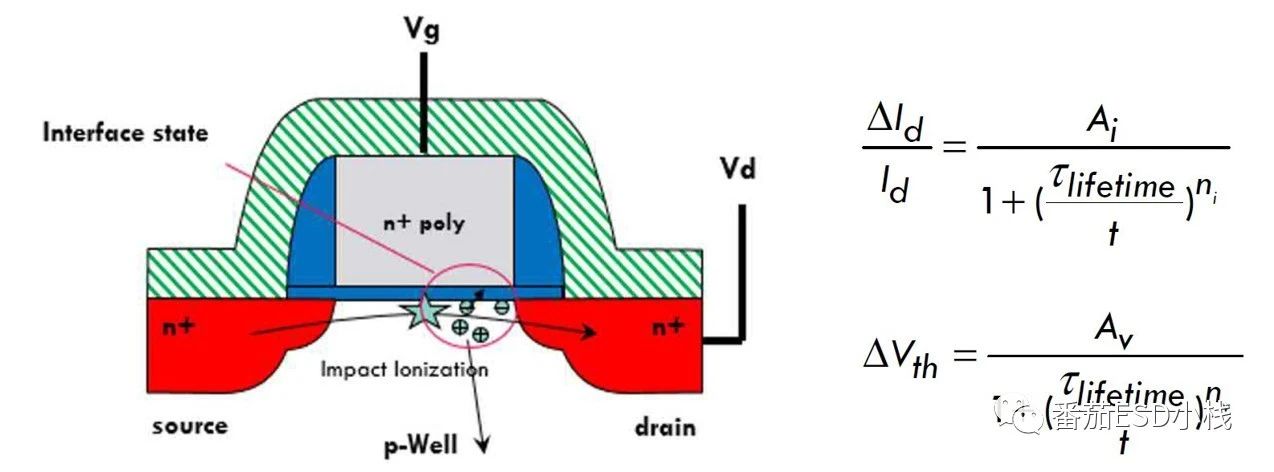

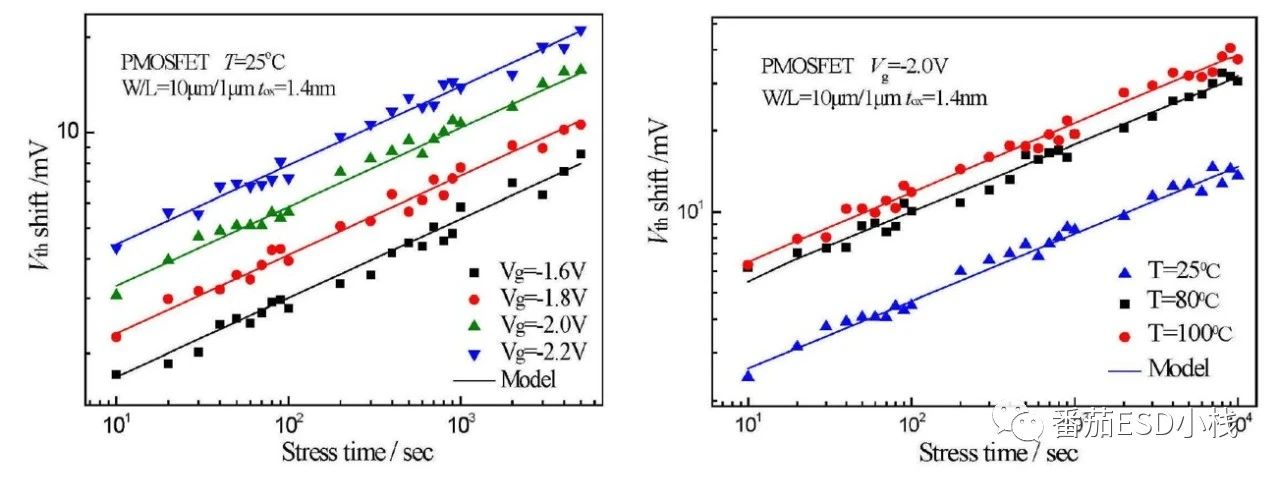

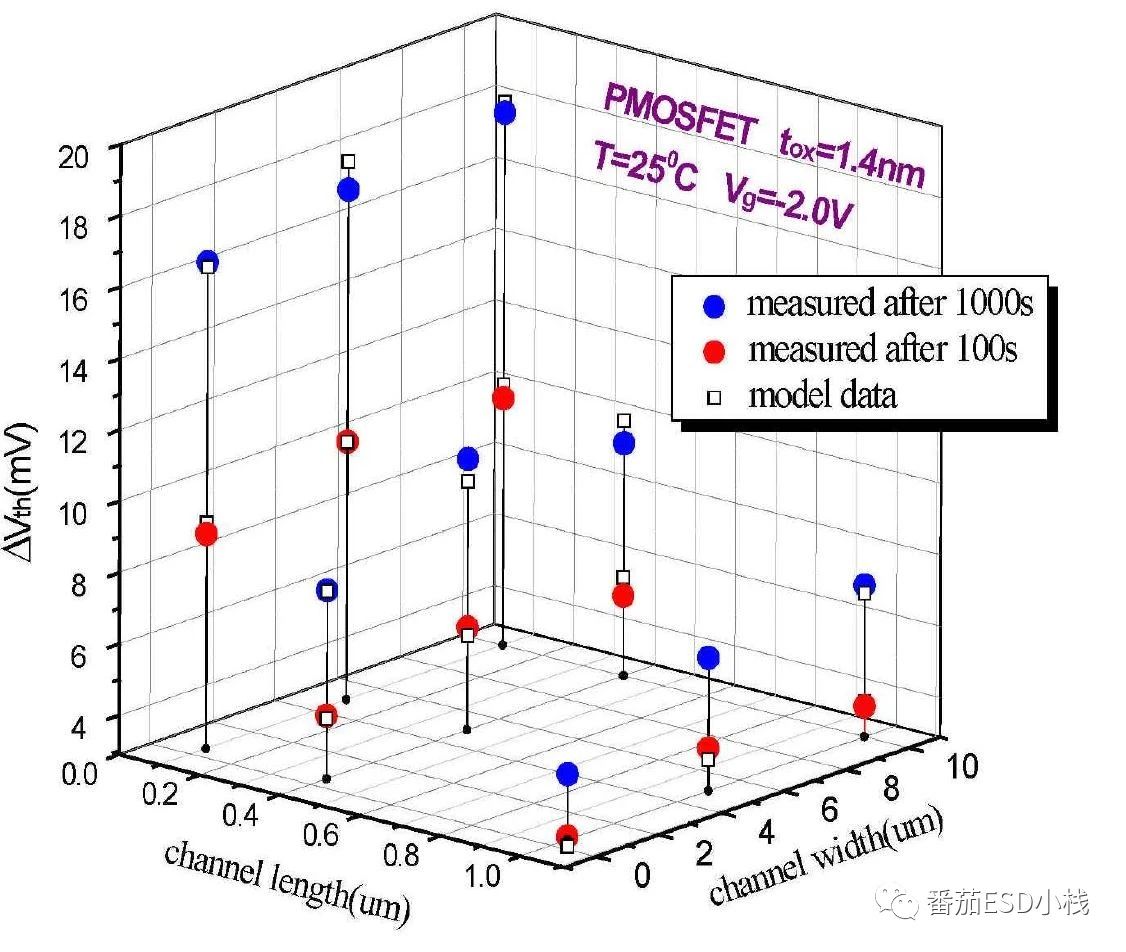

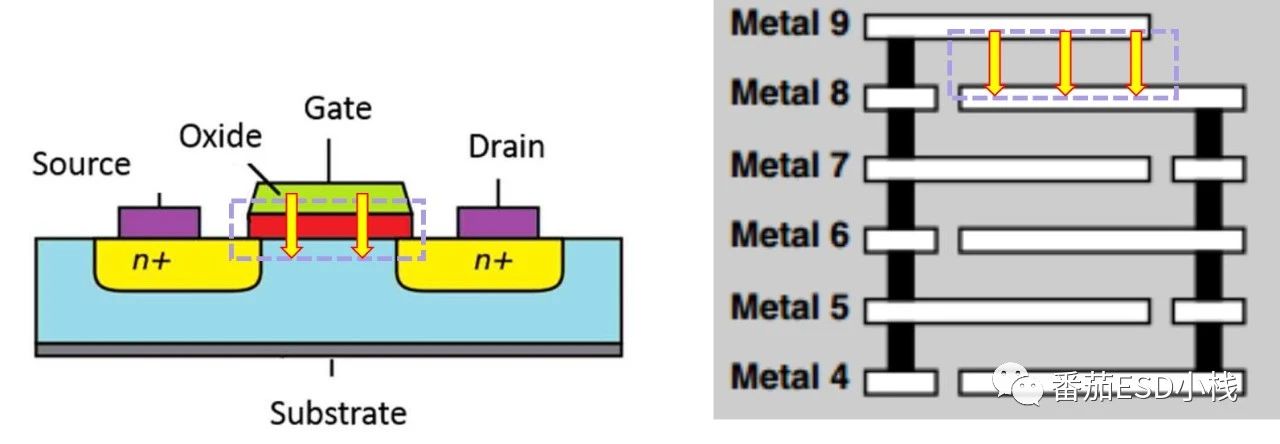

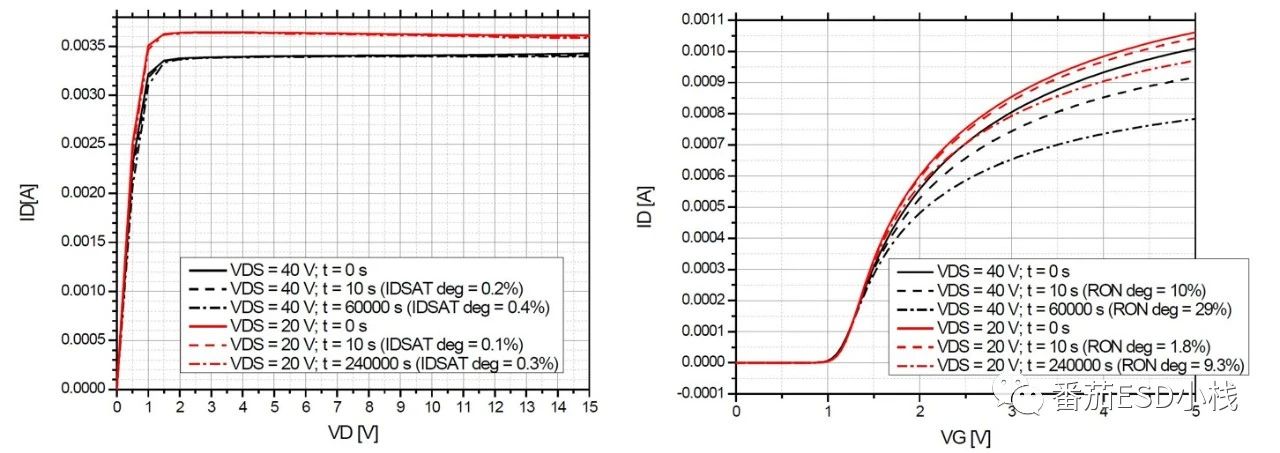

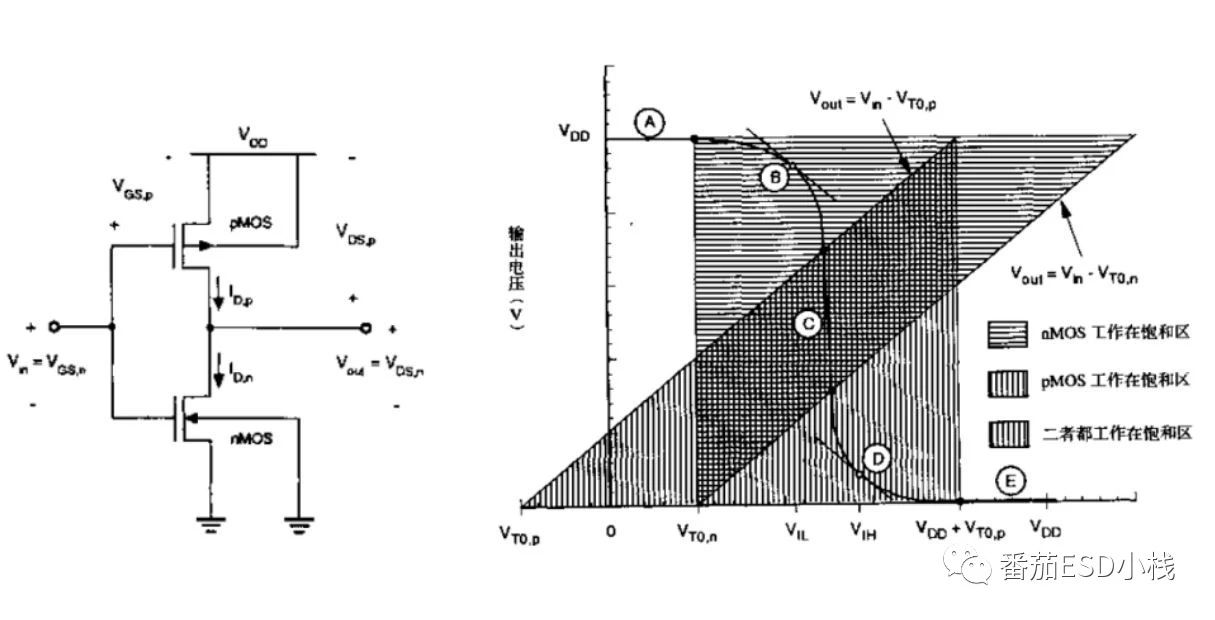

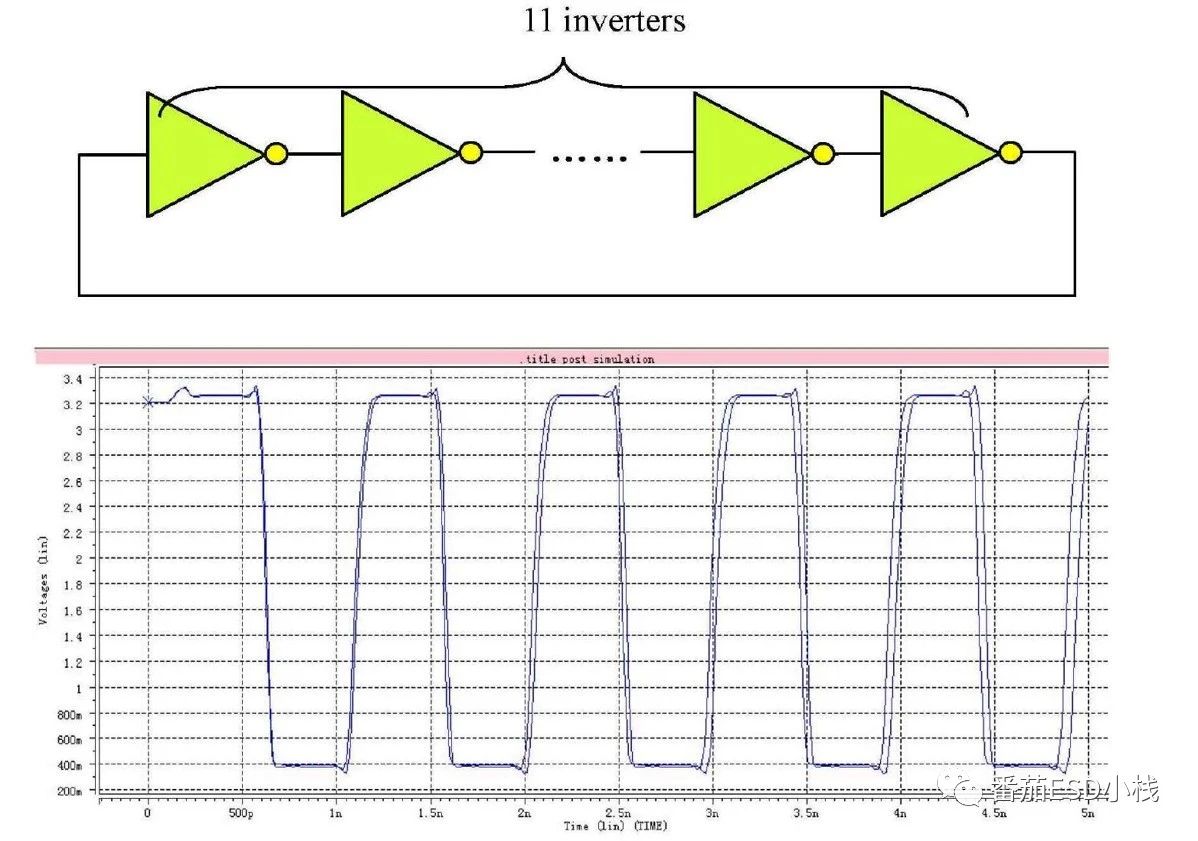

随着芯片需求的日益旺盛,对高可靠性芯片的追求也水涨船高。尤其是车规级,工业级,军工级更是对可靠性提出了严苛要求。而这一期笔者将要探讨芯片的电可靠性。 图一.不同行业对芯片可靠性要求。 如图二A所示,IEC提供的电失效中因EOS(Electrical overstress)失效的占比,对于大部分企业来说EOS已经成为芯片电失效的主要原因之一。  图二.IEC关于电学失效与EOS的统计结果。 而EOS又包含了很多失效原因,如图二B所示,IEC对EOS失效原因进行统计,其中占比最大的是不当的应用,其次是ESD。在实际使用场景中,诸如超限使用、不规范应用场景、引脚连接不当、短路等情况都会使芯片面临EOS冲击,这些情况大部分都是可以避免的。但是在芯片设计过程中也需要通过电路/版图设计来提升芯片可靠性,降低芯片EOS失效风险。 如图三所示,芯片设计人员需要面对的EOS种类有如下三种:1.Component ESD ,芯片本身的ESD事件。2.System ESD,芯片在系统级应用时面对的ESD事件。3.Device Reliablity器件在使用过程中的可靠性,这一期就主要探讨电可靠性—EOS—Device Reliablity。  图三.EOS分类框图。 一. Device Reliablity机理 影响器件可靠性的三种常见机理:1.HCI(Hot Carrier Injection),2.N\PBTI(Negative/Positive Bias Temperature Instability),3.TDDB(Time Dependent Dielectric Break-down),这三种效应会使得器件的性能随着时间的推移发生衰减,从而影响整个芯片的可靠性。 1.1 HCI(Hot Carrier Injection) 如图四所示,MOS器件当载流子在Drain端的强电场作用下会在栅氧层处发生电离作用从而形成界面态,界面态会成为载流子陷阱,影响载流子在沟道中的漂移运动,从而对整个MOS管的性能产生影响,HCI效应对MOS管的损伤是不可逆的。HCI效应在NMOS上更加明显,因为电子的有效质量较小,其抗扰动能力也相对较弱,界面态对其影响更大。该现象会造成NMOS的阈值电压Vth上升,ID电流减小。  图四.HCI效应示意图。 图中公式所示,HCI对NMOS电学性能产生影响的核心原因在于其改变了NMOS载流子寿命。HCI效应会在P-WeLL与氧化层的界面处产生大量陷阱中心,近似于引入了杂质,所以需要更大的栅压才能实现P-WeLL反型,同时载流子的寿命也会降低,增大了电阻率。 如图五所示,VD和Leff(沟道长度)会影响HCI的衰减程度,沟道长度越短/VD越高/VG越高,HCI加剧,寿命越短,反之Finger/Width越大,HCI缓解,寿命越久。NMOS采用LDD工艺也能缓解HCI效应。  图五.HCI效应不同条件下对载流子寿命的影响。 1.2 N\PBTI(Negative/Positive Bias Temperature Instability) 如图六所示,当MOS管栅极在高温和在垂直电场作用下时,其中一些不稳定的悬挂键会发生断裂,从而在栅氧化物与半导体衬底界面形成界面陷阱,从而影响载流子漂移率。因为是在电场作用下感应生成的表面态所以该效应对PMOS的影响远大于NMOS,且是可逆的。但是随着时间的推移,由N\PBTI造成的感应缺陷可能会转变为晶格缺陷。虽然机制上与HCI有所不同,但是NBTI也会提高Vth,降低跨导Gmax。  图六.N\PBTI效应机理示意图。 如图七所示,NBTI效应主要受到Vgs和Temp影响,Vgs/Temp越高,NBTI越明显,阈值电压偏移越大。  图七.NBTI衰减栅压与温度曲线。 如图八所示,W对NBTI所造成的衰退影响不大,而L越小,NBTI造成的衰退越明显。  图八.NBTI衰减栅压与W与L曲线。 1.3 TDDB(Time Dependent Dielectric Breakdown) TDDB氧化物击穿。TDDB有两种:Hard-Breakdown,氧化物瞬时被击穿,器件即时损坏,漏电陡变;Soft-Breakdown,氧化物局部出现熔点,绝缘效果下降,漏电增大,而且会有向Hard-Breakdown转变的趋势。  图九.MOS与MIM发生TDDB示意图。 如图九所示,电路中除了MOS管之外,MIN电容也需要考虑TDDB效应。 上述三种衰减机理中时间都是影响器件衰退的主要原因,随着器件在使用时间越久,HCI、N\PBTI、TDDB等效应就会逐渐显露,慢慢侵蚀整个电路的可靠性,而不适当的工作条件会加速这一过程。三种衰退机制对先进FinFET工艺和高压BCD工艺的影响较大,FinFET工艺虽然工作电压低,但是电路规模大,且频率快,任何微扰都会对系统带来风险。而高压BCD工艺虽然电路规模小,但是工作电压高,会加剧器件衰退,从而对电路产生影响。 二. Device Reliablity的电路影响 HCI和NBTI效应是在不同的机制下生成表面态,从而影响器件的工作特性。如图十所示为器件的输出衰退特性曲线和转移衰退特性曲线,可以看出HCI和NBTI效应对器件的输出特性和转移特性都会产生影响,尤其是随着时间的推移,这种影响愈加明显,过高的工作电压也是诱因。  图十.输出衰退特性曲线和转移衰退特性曲线。 这里举几个简单的电路例子: 1. 反相器 如图十一所示为反相器的工作状态与工作曲线,如果Vth发生变化,反相器的门限电压也会发生变化,从而影响其翻转特性,会降低反相器的噪声容限和增加动态功耗。  图十一.反相器电路与输入-输出曲线。 2. 环形振荡器 如图十二所示为环形振荡器电路图与其振荡特性曲线,该环形振荡器由十一个反相器构成,PMOS因NBTI发生衰减,每个PMOS的阈值电压都会升高,PMOS的开启能力降低,开启延迟增大。从前后振荡特性对比上可以看出发生衰退的环形振荡器的输出曲线会发生比较明显的延迟。  图十二.环形振荡器与振荡特性衰退曲线。 (这可能也是很多SoC芯片越用越慢的原因之一,芯片性能随着时间发生了衰退) 全片设计中,除了Component ESD外还要考虑应用端ESD和芯片可靠性等一系列问题,芯片设计这种系统性工程需要工程师做到面面俱到。下期将进一步继续探究器件可靠性对复杂电路的影响,以及解决办法和仿真方法。 |