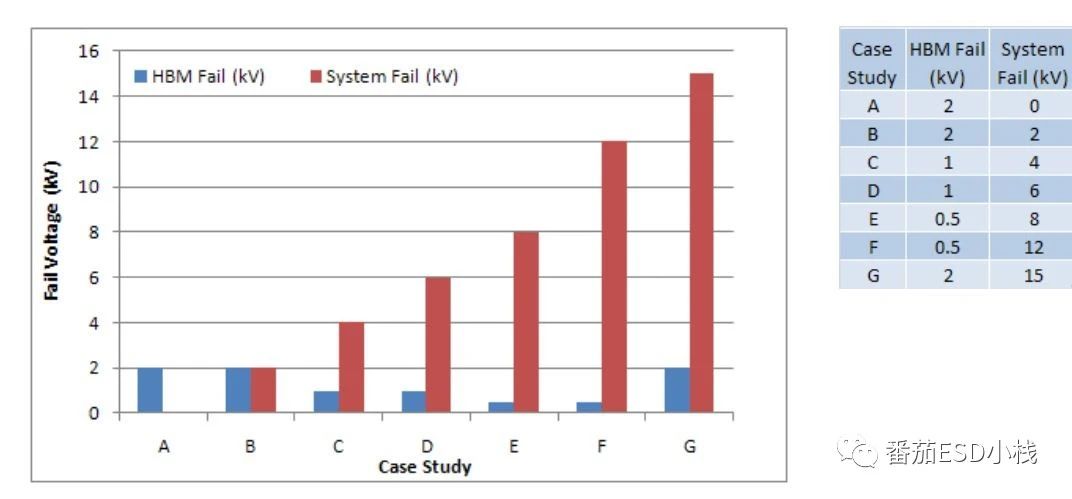

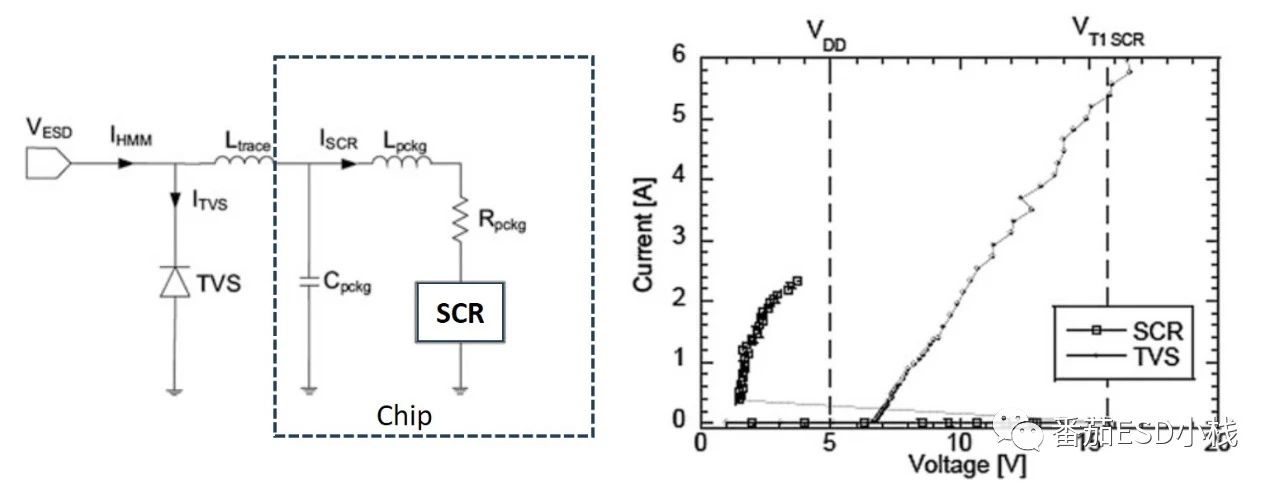

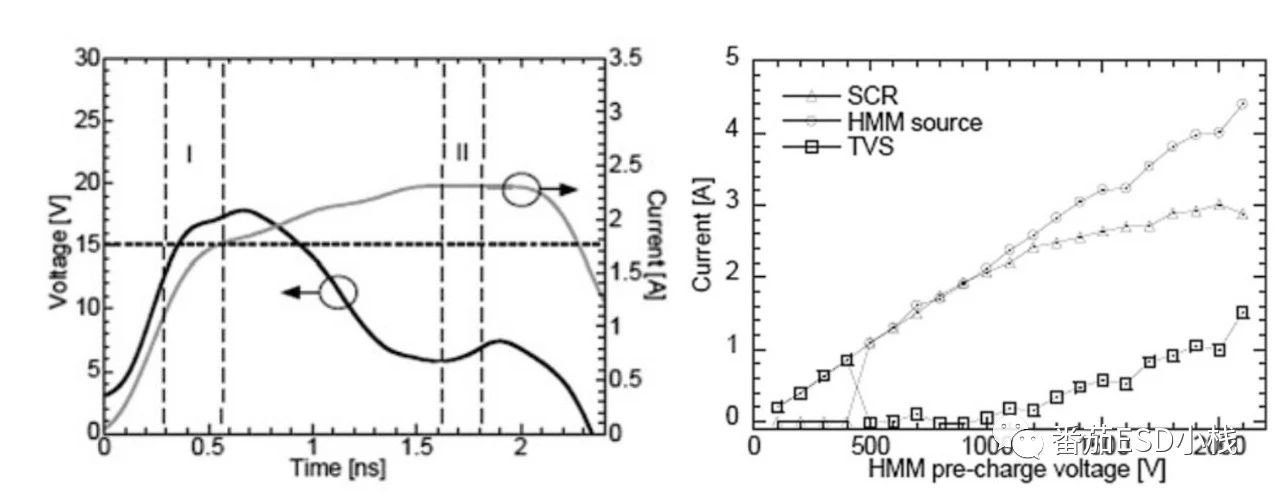

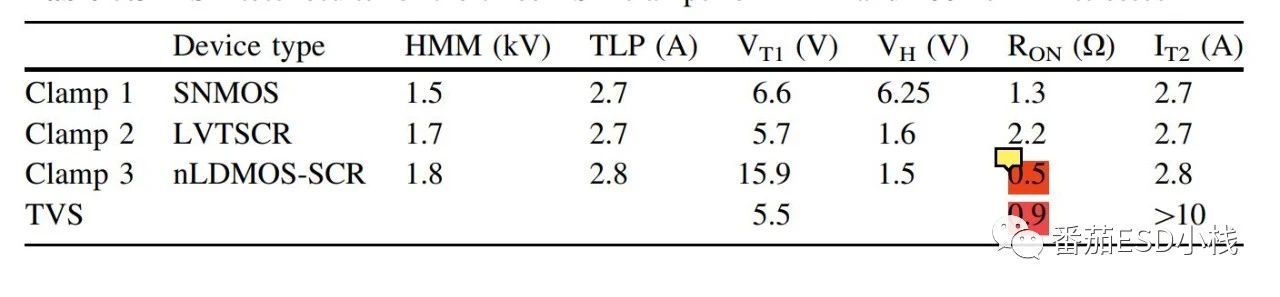

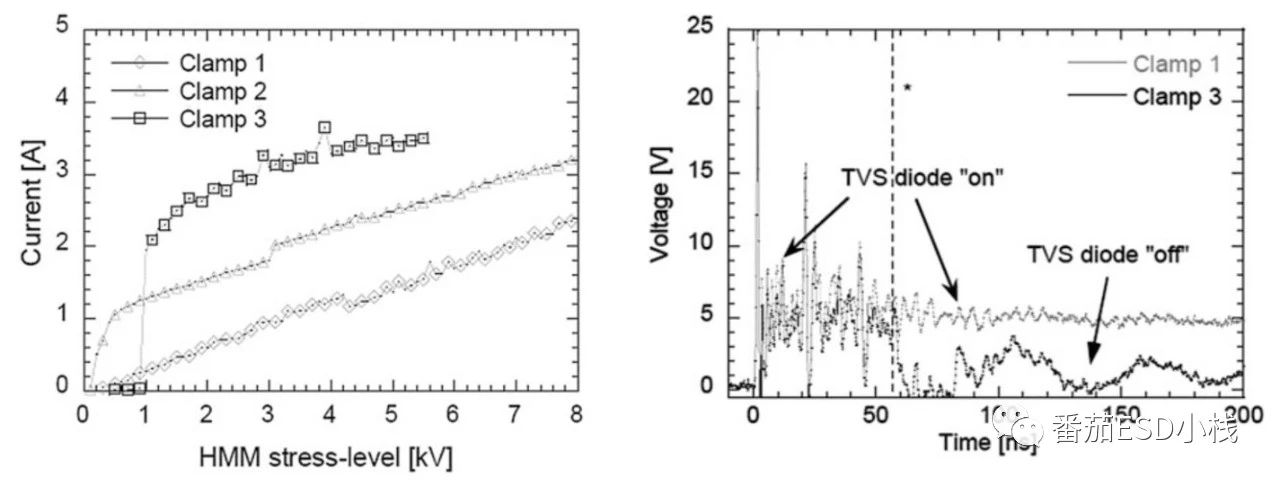

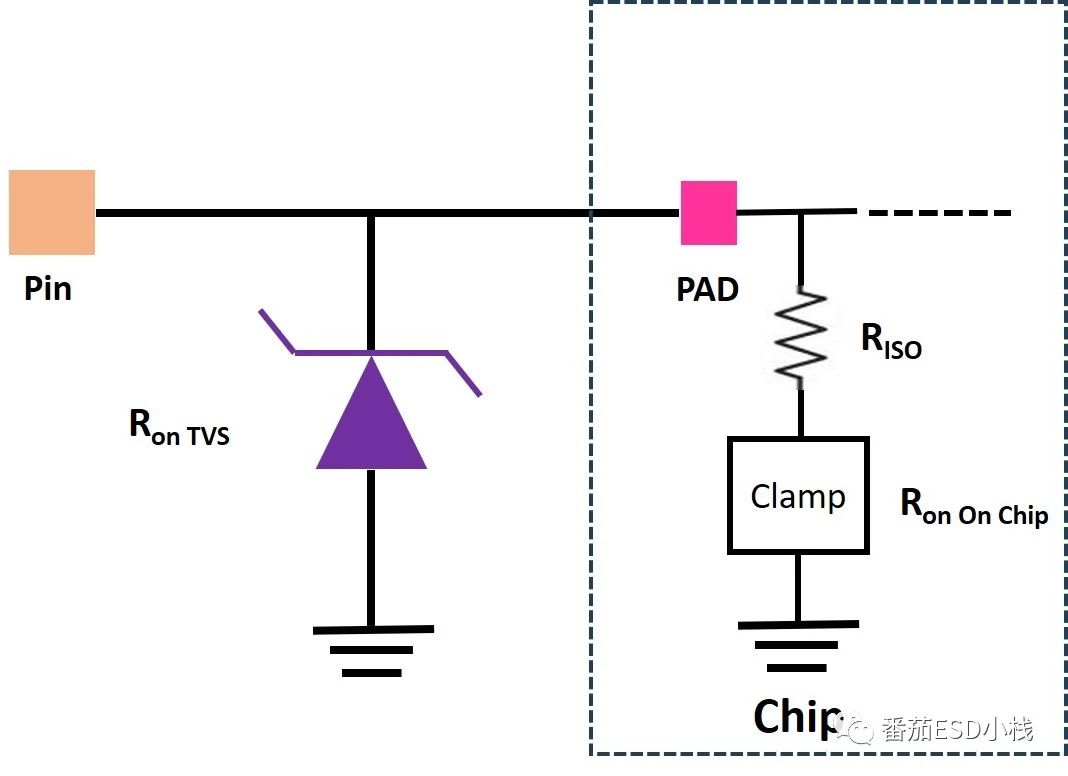

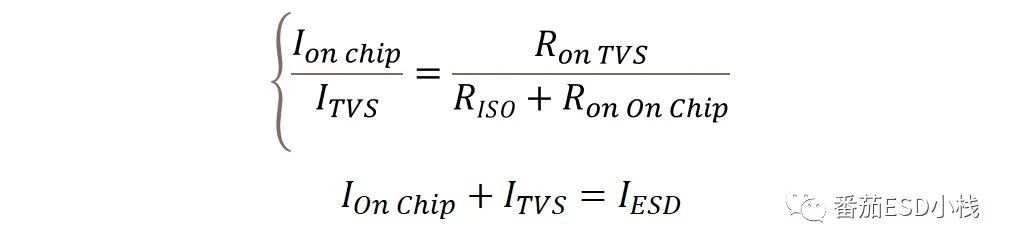

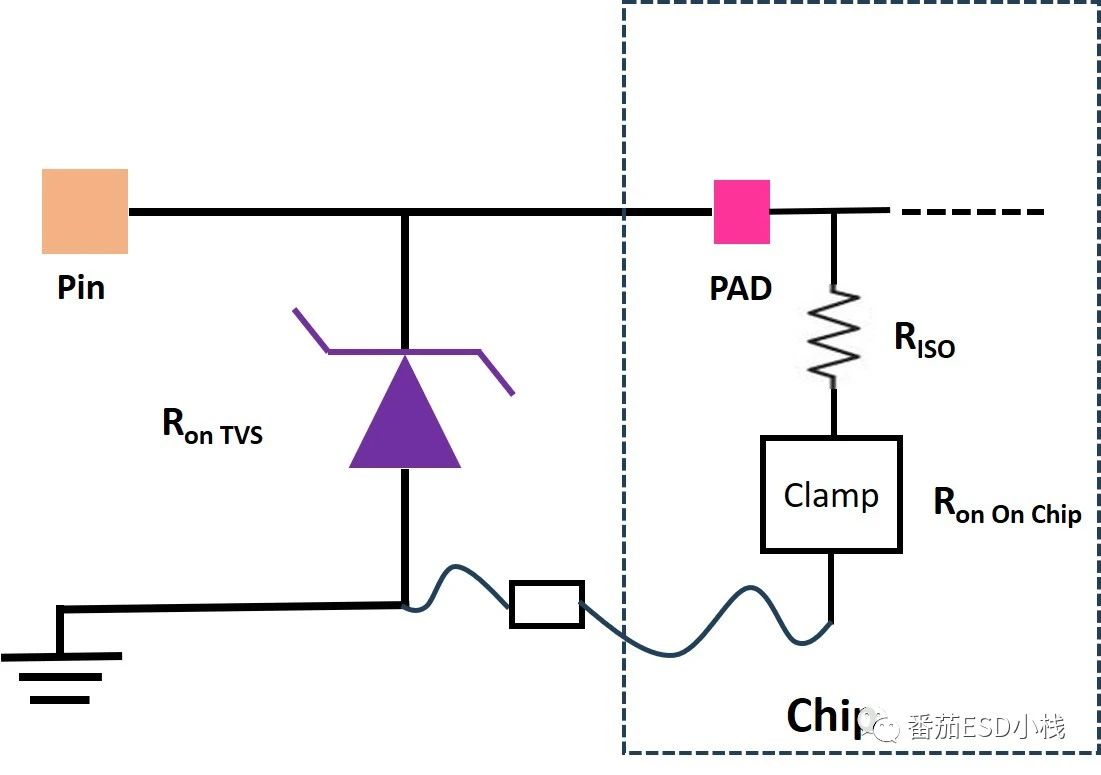

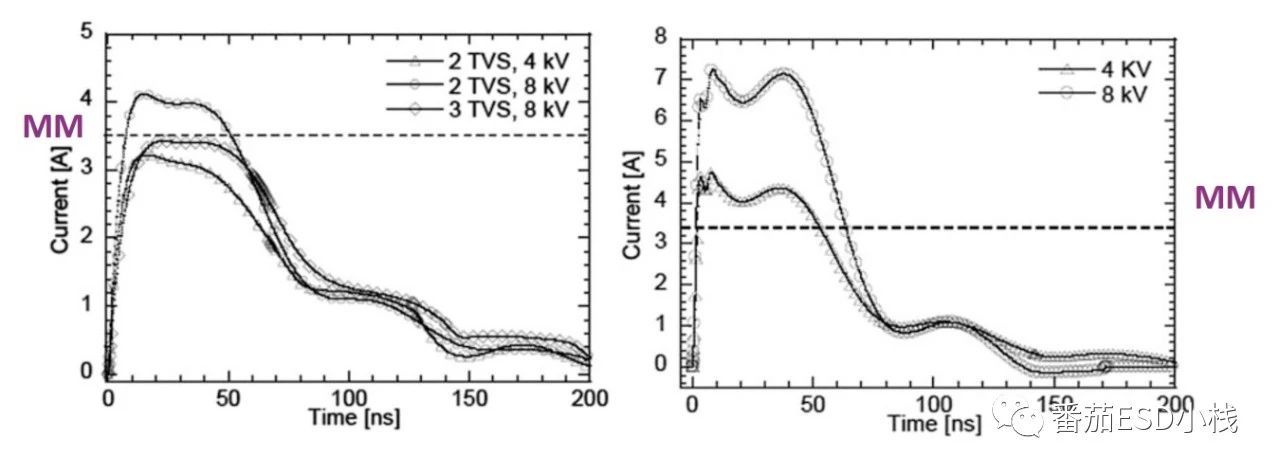

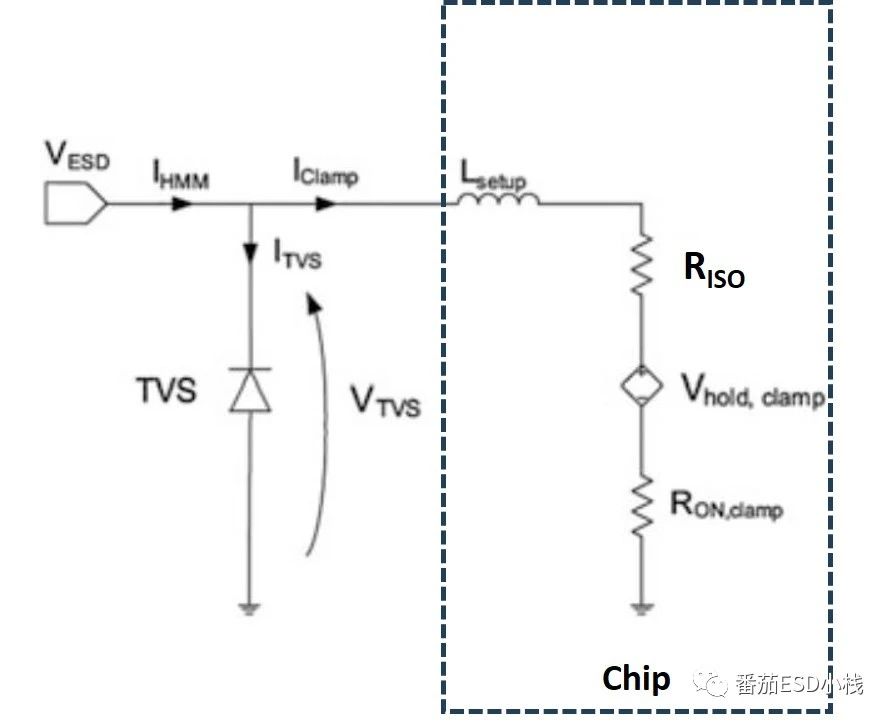

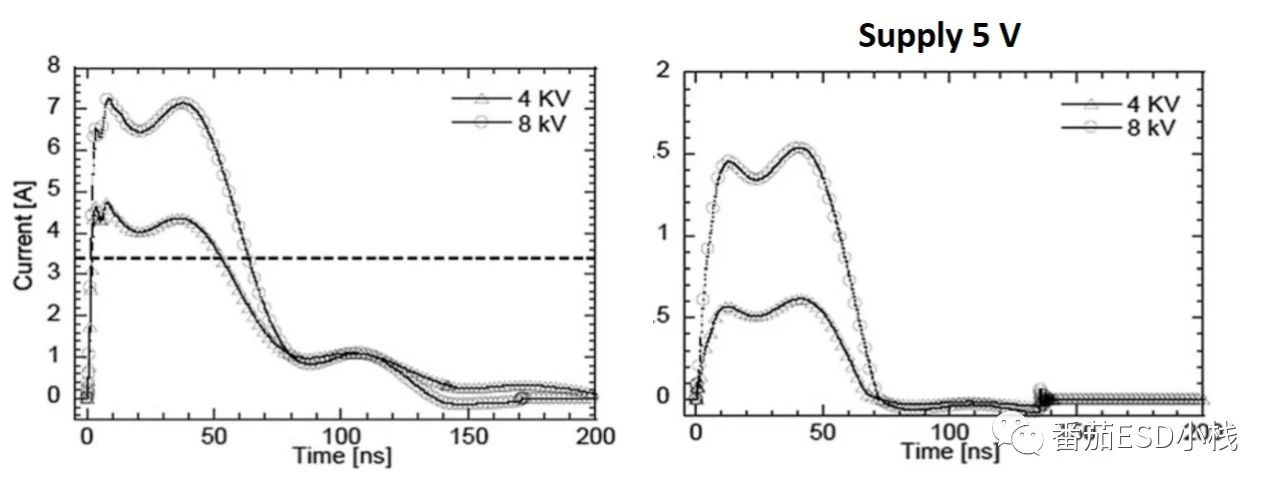

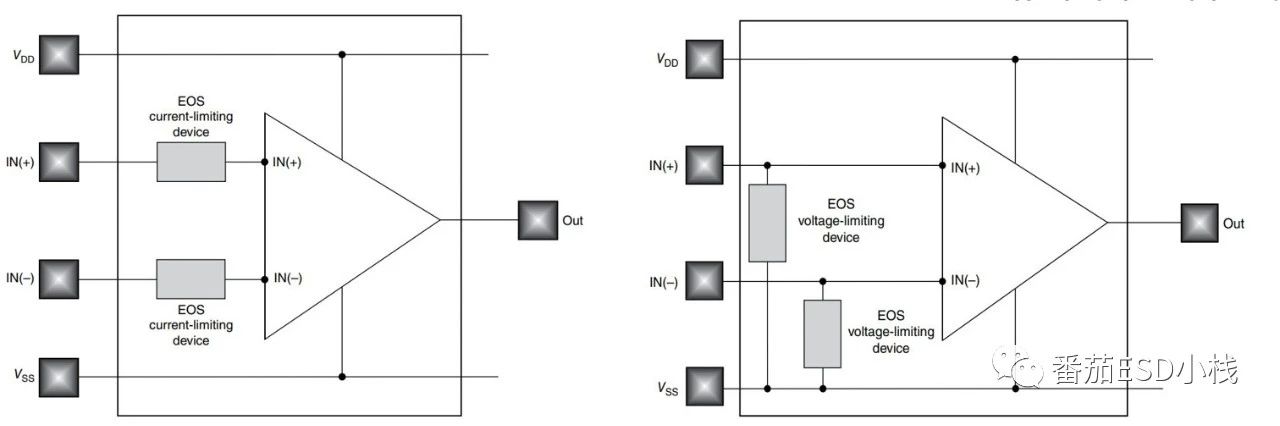

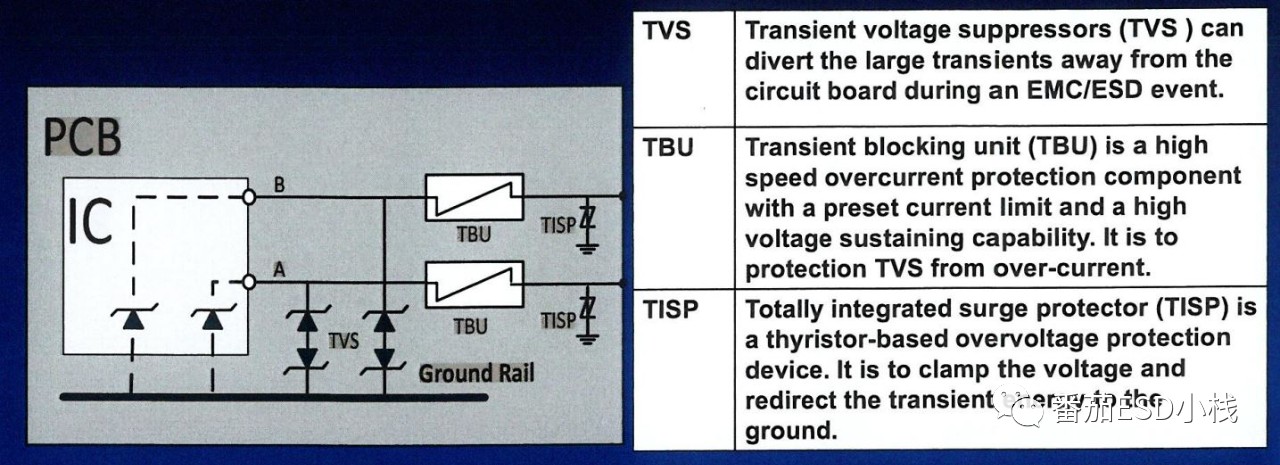

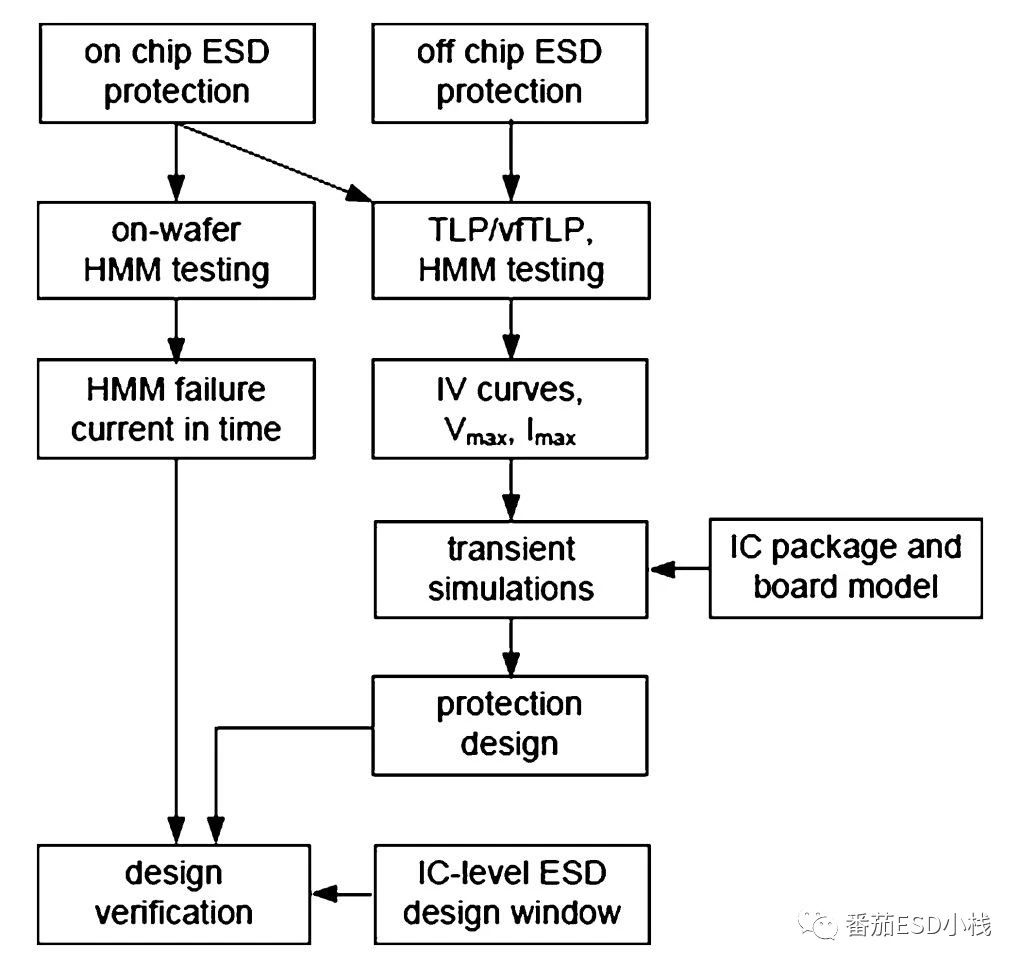

On-Chip ESD防护器件与Off-Chip ESD防护器件之间存在耦合关系。如图一所示,所以System ESD与Component ESD防护能力间的关系也并不简单。 图一.HBM与System ESD失效电压对比。一.Off Chip ESD与On Chip ESD的相互作用: 1.1 竞争冒险 Off Chip ESD与On Chip ESD发生竞争冒险时,On Chip ESD会把System ESD电流“抢走”,大部分ESD电流会由On Chip ESD泄放,从而造成芯片损坏。  图二.On Chip SCR与TVS示意图与TLP曲线。如图二所示,一款采用SCR作为On Chip ESD 防护结构的芯片,其HBM防护等级为4 kV,Trigger Voltage 为15 V,Holding Voltage为2 V,Holding Current 为0.2 A,SCR It2为2.4 A。而TVS的击穿电压为6 V,两者的TLP结果如图所示。当系统发生ESD时,TVS首先开启,随着流经TVS电流的增加,两端压降也会上升,当电压上升到15 V后,On-Chip SCR就会开启,发生Snap-Back,Holding Voltage 降为2 V,System ESD电流转由On-Chip SCR泄放,相当于SCR把TVS短路,On Chip ESD与Off Chip ESD发生竞争冒险,从而造成失效。  图三.TVS瞬态TLP曲线与 System ESD电流分配关系。 如图三所示为Off Chip TVS的瞬态TLP曲线,可以看出当Off Chip TVS压降超过15 V后,立马又降回15 V以下,过电流能力(电流对时间的导数)在电压超过15 V后也会下降。从电流分配上看,随着System ESD电压上升,流经Off Chip TVS的电流在500V HMM后会骤降,反之流经SCR的电流会骤升,System ESD泄放通道由Off Chip TVS转为On Chip SCR。如图四所示,该系统中TVS起到的作用非常有限。  图四.On Chip SCR与On Chip SCR+Off Chip TVS面对System ESD 防护能力对比。 1.2 协同分流如同硬币的两面,竞争冒险与协同分流的本质一样,只是竞争冒险中On Chip ESD泄放的电流超过了其安全阈值,反之协同分流泄放的电流是在安全阈值之内。如图五所示为三种常见On Chip ESD Device的性能参数,其中LVTSCR & LDMOS_SCR Holding Voltage都小于TVS Vt1,而LVTSCR Ron大于TVS Ron。  图五.三种常见On Chip ESD Device性能参数对比。 三种Clamp的I-HMM图像如图六所示,LDMOS_SCR的电流在1 kV HMM下骤升到2 A,说明其在1 kV下便发生了竞争冒险,而SNMOS(Snap-back NMOS)与LVTSCR的过电流是随着HMM等级呈线性上升趋势,直到4 kv和8 kV下才达到 2A。从TVS的瞬态电压中可以看出连接LDMOS_SCR的TVS开启一段时间后便Shut down,之后电流都是由LDMOS_SCR泄放。SNMOS(Clamp 1)和LVTSCR(Clamp 2)与TVS相互协同分流,而LDMOS_SCR(Clamp 3)与TVS间相互竞争冒险。  图六.三种常见On Chip ESD Device的I-V曲线与TVS的瞬态TLP。 所以除了Holding Voltage之外Ron也是判断是否会发生竞争冒险的关键参数,Ron On Chip小于Ron Off Chip,Holding Voltage小于TVS Vt1,Off Chip ESD与On Chip ESD便会发生竞争冒险。三种结构中虽然LVTSCR(Clamp 2)的Holding Voltage小于TVS Vt1,但是Ron On Chip大于Ron Off Chip,所以其System ESD防护性能优于LDMOS_SCR。  图七.隔离电阻示意图。 如图七所示,增加隔离电阻RISO也能避免发生竞争冒险,即便On Chip ESD器件的Holding Voltage小于Vt1,但是放置电阻能有效抑制System ESD的灌入。设,TVS的开启电阻为RonTVS,On Chip ESD的开启电阻为Ron On Chip,理想化的公式如下:  通过放置RISO能降低流入芯片的ESD电流,从而降低发生竞争冒险的风险。这种设计方法就是利用隔离电阻作为电流抑制器件,阻止System ESD进入芯片内部,后面会提到这种设计思路。  图八.GND隔离示意图。 如图八所示,如果On Chip ESD防护能力有限,可以将Off Chip ESD与On Chip ESD的GND隔开,形成两条回路,这样能大幅度限制System ESD进入芯片。IEC 61000-4-2中的波形在最开始的1 nS内会存在一个很高的尖峰放电,这部分静电能量较低但是峰值很高,在实际设计中因为PCB trace与封装寄生电感与电阻,对On Chip ESD的影响较小,但是最好避免Input Buffer的栅极直连PAD。 1.3 相互独立在面对雷击或者浪涌这种大能量System ESD时就需要Off Chip ESD与On Chip ESD间完全独立,互不干涉。面对这类需求时,TVS的选型就需要参考10/1000波形。而且需要较大的限流电阻去保护On Chip ESD避免雷击/浪涌的冲击。另外芯片与防雷端口最好不要共地,防雷端口连接其专门的GND。 二.System ESD Design Window上一期提出了System ESD Design Window的概念,发生竞争冒险的根源在于Design Window的选取不合理。  图九.System ESD Design Window示意图。 如图九所示,以芯片手册上的MM防护等级为电流上限(MM比HBM更贴近IEC 61000-4-2波形),System ESD进入芯片后的“残流”不能超过这个阈值。之前提到的无论是Holding Voltage还是RISO,其核心都是保证On Chip ESD的电流不能超过其可承受的范围。  图十.System ESD 仿真电路图。 如图十所示,可以通过建立简单的仿真模型计算出流经TVS和On Chip ESD Device的电流比值。针对Snap-Back型器件,选取一个Break Down Voltage等于Trigger Voltage的反偏二极管加一个Ron On Chip电阻进行替代,这种仿真电路关注的是反偏二极管击穿前的电流分配问题,器件本身的Snap-Back特性需要另外考虑。 在得知System ESD Design Window后就能根据窗口确定TVS的技术指标与RISO的大小,以及其它细节。另外当System ESD发生时,系统大多数时刻都处于上电状态,所以很多测试需要在上电状态下进行,上电状态的TLP与未上电的结果有一定差异。如图十一所示,上电状态下器件都处于稳定状态,流入芯片内的“残流”会远小于未上电状态,所以保持芯片处于上电状态也是能有效拓宽System ESD Design Window的手段之一。以笔者的工作经验来看,这种差距在体隔离工艺上较为明显,究其原因是未上电状态下衬底电位不固定,隔离未生效,导致整个芯片都不稳定,所以才会造成上电与未上电的情况下产生差距。(隔离与衬底的问题,电路前仿很难顾及,因为又涉及到PCB级仿真,怎样兼顾有源器件的隔离与衬底,又能兼顾PCB级的仿真也是摆在笔者面前的难题)  图十一.上电与下电状态下System ESD “残流”对比。 三.Off Chip ESD设计方法  图十一.Off Chip ESD器件类型。Off Chip ESD器件主要分为两种:一种是Voltage-limiting Device,最常见的是TVS。另一种是Current-limiting Device,无源电容,电阻与有源TBU都属于该类。  图十二.Off Chip ESD器件简介。在设计过程中Current-limiting Device和Voltage-limiting Device需要相互配合共同使用,Current-limiting Device对System ESD进行抑制,Voltage-limiting Device建立了System ESD的泄放通道。  图十三.Co-Design设计流程。 四.结语 因为System ESD设计是个系统性设计,还需要与硬件工程师沟通进行PCB板级设计,PCB板对System ESD的影响也是不容小觑的,而这方面笔者也不甚清楚。所以只能从芯片设计的角度出发,探讨一下System ESD与Component ESD的Co-Design,希望能为整体系统的ESD设计提供新思路。 |