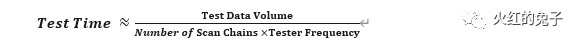

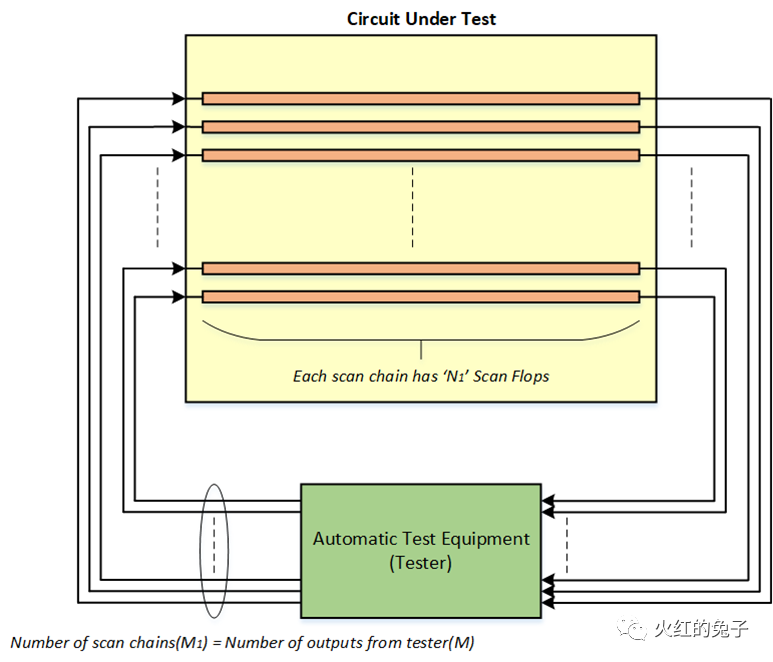

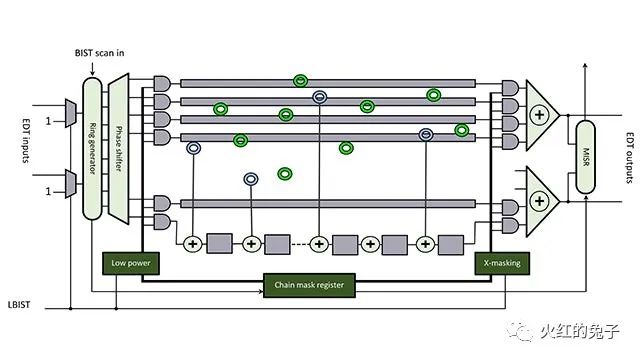

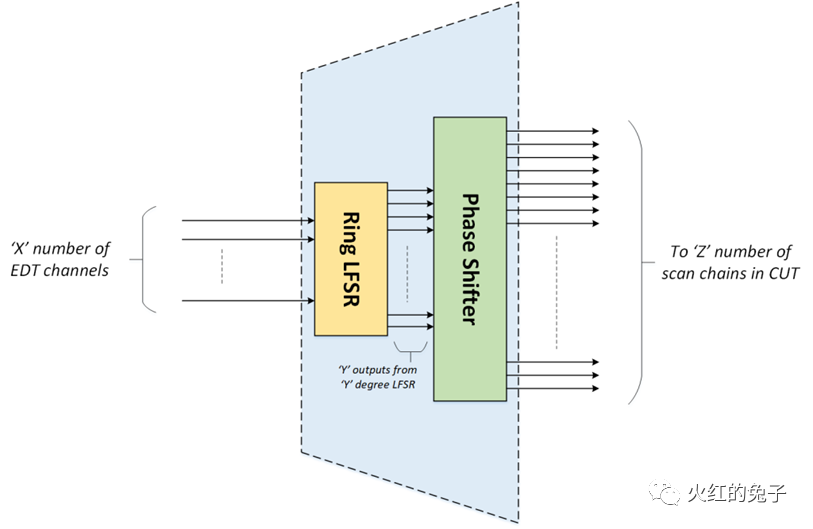

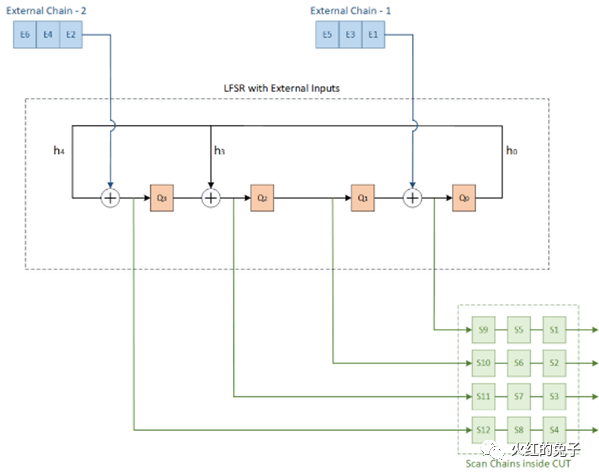

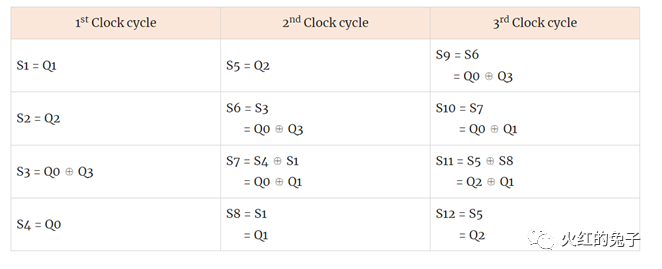

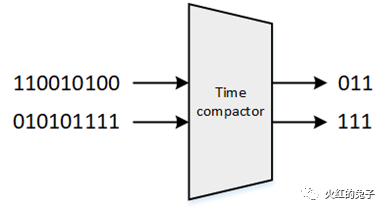

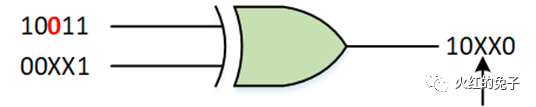

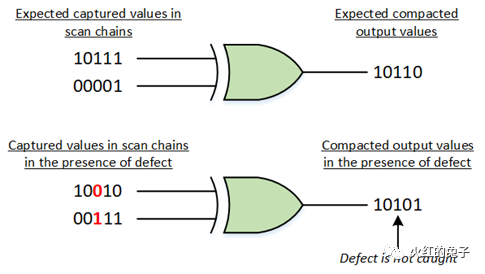

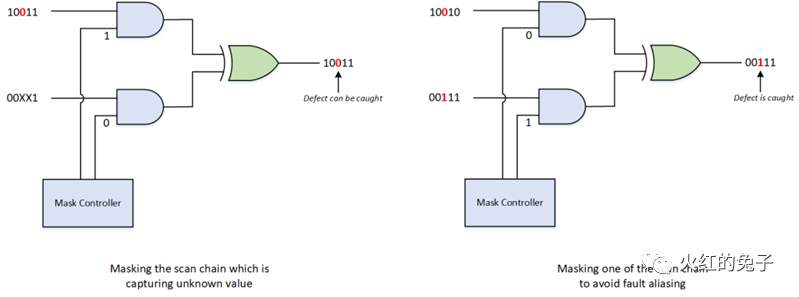

压缩技术的讨论大致的发展史可以简单分为:第一代压缩技术:自动测试pattern生成(ATPG)工具以复杂算法形式实现的测试压缩的软件技术第二代压缩技术:采用基于硬件的测试压缩技术,通过增加额外的逻辑到电路,如EDT。第2.5代压缩技术: 利用高速IO,通过串并转换的方式增加Scan测试的带宽。第三代压缩技术:基于1149.10的高速IO协议+内部channel bus的方式,减少IO、增加带宽、提高测试频率。代表之作:EDT硬件逻辑介绍 ①② 大规模集成电路中,测试数据量随着电路尺寸的增加而呈指数级增长。当前日益创新的电路规模,测试数据量的增长会导致测试成本显著增加,因为测试时间更长,存储测试数据的测试器内存需求也增加。EDT测试压缩技术对于在保持的测试质量的同时减少scan patterns的背景下提出的一个优秀的解决方案。 Test Data Volume ≈ Number of Scan Cells in all the Scan Chains × Scan Patterns  测试数据量大致等于所有扫描链中的扫描单元数量乘以pattern的数量。由自动测试pattern生成(ATPG)工具以复杂算法形式实现的测试压缩的软件技术不足以实现高度的测试压缩。因此,现在常采用基于硬件的测试压缩技术,通过增加额外的逻辑到电路中,但代价是增加了面积。  EDT电路介绍 嵌入式确定性测试 (EDT) 最常见的硬件测试压缩技术之一是嵌入式确定性测试(EDT)。Tessent TestKompress是可以在RTL级别生成decompressor和Compressor逻辑的工具。如图2所示,Decompressor驱动扫描链输入,Compressor输出与扫描链连接。 通常,当ATPG工具针对一组故障生成一条pattern时,结果只有少数扫描触发器需要取特定值。它会使用随机值来填充那些不能提高目标故障检测的未指定的扫描触发器。因此,在传统的ATPG中,pattern包含许多“x”或不关心的位,这增加了测试数据量,并且将这些位加载到扫描链中增加了测试时间。  更加详细的EDT示意图如下:  EDT处理ATPG pattern的所需bit位,并确定如何通过decompressor以EDTpattern的形式加载它们。处理后,通过decompressor加载结果压缩pattern(或EDTpattern),并将ATPG pattern的指定位加载到其相应的扫描触发器中。decompressor的一个潜在的作用是所有未指定的位都加载了随机数据,这个作用实际上是帮助压缩的原因。因此,测试量通过不必存储这些未指定的位而减少,通过不必特别加载随机数据而节省了许多测试周期。 Decompressor 由一个Ring Generator组成,它基本上是一个带有外部输入的RingLFSR,如图3所示。馈送Ring Generator的外部输入通常被称为EDT通道。Ring Generator触发器的输出将通过由XOR门组成的相移器连接到扫描链输入。Phase Shifter有助于支持相比于Ring LFSR更多的扫描链。 Ring Generator的输入由存储在ATE上的压缩pattern驱动。而由原始ATPG测试pattern创建压缩的pattern是基于Ring Generator多项式和相移器连接的线性方程组的求解。  Ring LFSR及其优势考虑一个带有外部输入的简单LFSR,如图4所示。首先运行ATPG以确定S1、S2、...、S12的值,然后解决线性方程。 注意:在第一个链(包含触发器S1, S5和S9)中,s1, s5和s9的值将串行加载到链中,这样s1将在第1个时钟周期中首先加载到链中,然后在下一个时钟周期中向右移位,同时S5将加载到链中。这继续了3个时钟周期,直到所有的值都加载到了它所需的位置。其他3个链以类似的方式加载。  当存在外部Chain时每个周期的计算公式如下:  包含12个等式和10个变量(4个LFSR seed 和8个外部chain输入)。 当不存在外部Chain时每个周期的计算公式如下:  包含12个等式和4个变量(4个LFSR seed)。 Compressor 基本上有两种类型的测试响应Compressor: 1. 空间Compressor [减少与输入引脚相比的输出引脚数量]  2.时间Compressor [减少与输入位流长度相比的输出位流长度]  EDT使用的是空间Compressor,它由XOR树的组合组成。允许在给定的扫描输出通道上同时观察多个扫描链。如下所示,几个扫描链被XOR组合到单个扫描通道中。  但是我们可能会遇到两个问题: a.由于未知值传播导致的'X'污染 Scan cells能够从black boxes、非Non-Scan cells,false paths等等捕获未知的”X”值,让我们假设有两条scan chains作用在同一个scan channels上使用XOR门,如图所示:X的捕获值将引入可观测的损失。  b.故障混叠(Probability of Aliasing -PAL) 当一个故障被观察到的扫描单元的偶数次数恰好在不同的扫描链中对齐到相同的位置,并且被压缩到相同的输出通道时,这个故障就被称为混叠。下面的例子说明了这种情况。对于这种独特的情境,我们无法看出良好电路和有故障的电路之间的区别  为了处理这些问题,mask控制器也被认为是Compressor逻辑的一部分。这个mask控制器连同扫描链输出的遮罩逻辑可以基于在pattern移入的末尾的几个位(称为mask bits)选择性地mask扫描链。  mask控制器 mask控制器的工作是基于遮罩代码来决定哪些扫描链应该被mask。例如,如果我们有4个扫描链和2位的mask code,那么我们可以有以下的遮罩选择: 00 - 不mask任何链 01 - mask第1个链 10 - mask第2个链 11 - mask第1和第2个链 这样,我们可以选择性地mask那些可能因为'X'污染或坏的PAL而导致故障混叠的扫描链。 Mask控制器还可以用于处理其他的测试响应问题,例如处理动态故障,其中一些扫描链可能会受到其他扫描链中的故障的影响。 总之,测试压缩技术,特别是嵌入式确定性测试(EDT),为我们提供了一种有效的方法来减少测试数据量和测试时间,同时还能够保持高质量的测试。通过使用decompressor和Compressor,我们可以实现高达1000倍的测试压缩,这对于大型电路来说是必不可少的。 |