在高速数字芯片的ATE测试中,我们总会遇到一个令人头疼的世纪难题:DUT 要求的差分阻抗是 80Ω、90Ω 甚至是75Ω,而大多数ATE机台专用差分通道等效阻抗却雷打不动地固定在 100Ω!是选择 Z_LB 匹配 Z_DUT 造成 ATE 接口不匹配?还是选择Z_LB匹配 Z_ATE造成 DUT 接口不匹配? 这个选择直接决定了LoadBoard (LB) 信号完整性(SI)和最终的测试良率。今天,将通过详尽的分析和实践经验,剖析True-Differential Coupling 和 Pseudo-Differential Coupling 两种模式下的阻抗匹配陷阱,尝试给出 ATE工程师LB 阻抗匹配的最优解法。 一、 基础知识:常用高速协议阻抗对照表 设计 LoadBoard 的第一步,是明确 DUT接口遵循的协议标准。不同协议对阻抗有着严格的要求,下表Summary了常见的差分协议阻抗匹配需求。

关键认知:LB 走线必须首先瞄准Zdiff或 Zse这一目标值,而不是 ATE Pogo的阻抗值。 二、 紧耦合差分对阻抗匹配(True Differential Coupling) 场景描述: DUT阻抗:Zdut = 80Ω (例如 DDR clock) LB 走线: Z_LB 必须为80Ω紧耦合差分 · ATE 终结:Z_ATE = 100Ω (true diff pair 阻抗固定) · 问题: 链路末端 (80Ω ->100Ω) 存在阻抗不匹配 链路分析:DUT->LB->ATE (接收/Read)信号从 DUT 驱动出来,通过 LB 走线,被 ATE 接收和比较。LB 最优设计:消除反射在这个场景下,我们的核心目标是:LB走线必须匹配Z_DUT,LB与ATE均采用true-differential couple,同时通过外部元件补偿 ATE 的不匹配(当ATE 差分通道输入阻抗可配置或可采用共模电平Vcom实现差分耦合时,则不许用此外部补偿电阻)。

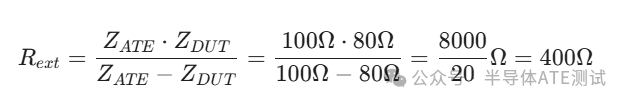

,我们需要的外部并联电阻Rext为:  最佳方案:在 LoadBoard 靠近ATE Pogo端,Pos vs Neg trace 之间放置一个400Ω的贴片电阻,同时ATE 采用Differential Pari channel 端接。 ATE Level 设置:如果LB 采用了Rext 方案,反射基本消除,此时ATE程序只需要:1. 时序校准:PinMargin确认ReciverStrobe(采样)时间,补偿Rext引入的微小延时。 2. 电平校准:设置Vterm和 Vcom,与 DUT协议的偏置点保持一致。 3. 链路分析:ATE->LB->DUT (驱动/Write) 信号从 ATE 驱动出来,通过 LB 走线,驱动 DUT 接收端。

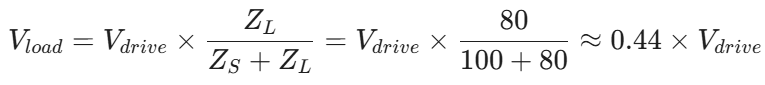

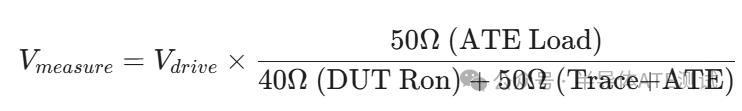

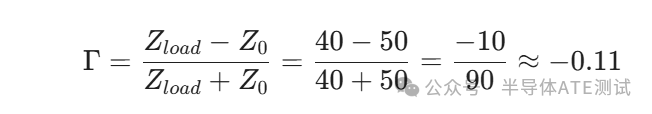

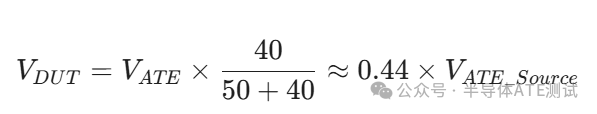

ATE Level 设置: 1. Driver Level 补偿:ATE driver(100Ω), 驱动80Ω传输线时,会发生分压:  ATE工程师可在程序中设置更高的驱动电压(Voh/Vol) 来补偿这个电压衰减,确保信号到达 DUT 端的幅度满足 Vih/Vil 规格2. 时序设置:ATE driver Strobe的时间应与DUT规格的建立时间Tsetup和保持时间Thold对齐。 三、 松耦合伪差分对阻抗匹配(Pseudo-Differential Coupling) 场景描述: DUT阻抗:Zdut = 80Ω (例如 DDR clock) ATE 端提供单端50Ω LB 走线: 必须匹配ATE 50Ω单端 · ATE 终结:Pos和 Neg 各自连接到两个独立的50ohm单端, 终结到Vterm · 问题: DUT端 (80Ω ->100Ω) 存在阻抗不匹配 在ATE仅能提供单端50Ω时,最佳方案:LB上差分对应该采用松耦合,50Ω走线阻抗匹配方式进行走线。链路分析:DUT->LB->ATE (接收/Read) 信号从 DUT 驱动出来,通过 LB 走线,被 ATE 接收和比较。 LB 最优设计:50Ω单端优先 在这个模式下,优先级是传输模式的连续性。 LB走线:P和N必须作为松耦合的50Ω单端线来设计,以确保每条线都匹配 ATE 的 50Ω 输入。 禁忌:绝不能采用40Ω紧耦合差分走线,否则会在ATEPogoPin处形成 40Ω→50Ω 的巨大不连续点,导致反射。 信号完整性:此时Z_LB = Z_ATE = 50Ω,ATE 端的反射为零 (Γ=0),信号以最干净的形式到达 ATE 比较器。 DUT负载:DUT看到的有效差分负载为:Zeff_diff=50Ω+50Ω=100Ω 影响:DUT发出信号 ->进入50Ω Trace线(由于 40Ω 驱动 50Ω 线,此处发生分压,信号幅度略微增大) -> 到达 ATE,因为ATE端完全匹配,信号被吸收,没有任何反射波弹回来。既然没有反射波弹回 DUT,DUT 就“感觉”不到线路末端发生了什么,也就不会产生振铃(Ringing)。 ATE Level 设置: 假设DUT为diff80 pari,此时Rdut=40Ω,连接到 LB (50Ω) 和 ATE (50Ω) 后,根据戴维南等效分压电路可得:  当理想匹配时(40Ω drive 40Ω load): 分压系数为:40/(40+40) = 0.5 当前方案(40Ω drive 50Ω load): 分压系数是 50/(40+50)≈0.55 ATE测到的电压幅度实际上比理论匹配情况下更大一点(约大10%),这对测试是有利的!因为它增加了信号的眼图张开度(EyeOpening)和电压裕量(Voltage Margin)。 设置Vterm:为了模拟DUT工作时真实的SystemBoard环境(通常DDR总线有上拉/下拉或ODT到VDDQ/2),可将ATE的Vterm设置为VDDQ/2(例如DDR4 1.2V 时设为 0.6V)。 链路分析:ATE->LB->DUT (驱动/Write) 信号从 ATE 的两个 50Ω 驱动器发出,驱动 80Ω 的 DUT 接收端, LB 走线:依然是松耦合 50Ω 单端线。 匹配分析:链路为 50Ω→50Ω→ZDUT,不匹配点在 DUT 接收端 (50Ω→80Ω)整个传输路径(ATE 板卡Cable + ATE Pogo + LB Trace)保持了 50Ω 的恒定阻抗。这意味着信号在到达 DUT 之前,波形是非常干净、没有因反射导致的台阶的,虽然在 DUT 处有反射,但因为 DUT 是接收端,且距离很短(封装内部),这种反射通常表现为信号幅度的轻微变化,而不是严重的振铃(Ringing) 反射系数:  这意味着: · 负反射(-11%):遇到比传输线更低的阻抗,电压波形会产生一个下冲,实际表现为信号幅度被“拉低”了。 能量吸收:绝大部分能量(1−Γ2≈99%)还是被DUT吸收了,仅有少部分能量反射回去。 Level设置:根据分压公式,ATE Vil/Vih 可设置为1.1*原始Vil/Vih  即如果DUT要求的Vih=1.0V,因阻抗不匹配,实际到达只有0.9V,ATE 工程师只需在程序中将Vih设置为1.13V(通常设置为1.2V), 即可完美补偿线路上的损耗和阻抗不匹配带来的幅度下降。 Summary: LB 阻抗匹配的优先级应该为“模式”优先,在ATE True Differential 和ATE Pseudo Differential 模式下阻抗匹配的优先级完全不同: 如果 ATE 提供 True Differential Pin: 保证DUT 协议的Zdiff 于LB 阻抗匹配优先级更高,即Z_LB 必须等于Z_DUT,且LB 上采用紧耦合方式走线。但因ATE differential pair端接阻抗100Ω 无法改变,当DUT需要 diff 80Ω 时,应在 LB 上P/N 端并联 400Ω 电阻以消除反射、确保信号质量。 如果 ATE只能使用单端 Pin: 优先级是保证50Ω传输路径的连续性,即Z_LB 必须等于Z_ATE,且LB 上采用松耦合的走线方式。 |