|

随着国家对集成电路行业的大力支持,国内集成电路行业发展如火如荼,一路高歌猛进,集成电路设计公司,晶圆厂,封测厂等相关企业的数量急剧增加,整个集成电路的产业都在迅速国产化,令人欣喜的是集成电路的品质也得到了前所未有的重视,其中与品质息息相关的可靠性测试,也成为重中之重,今天我们来简单谈谈:如何完美的做好可靠性测试中最重要的一项测试:高温工作寿命测试(简称老化测试或者HTOL)。

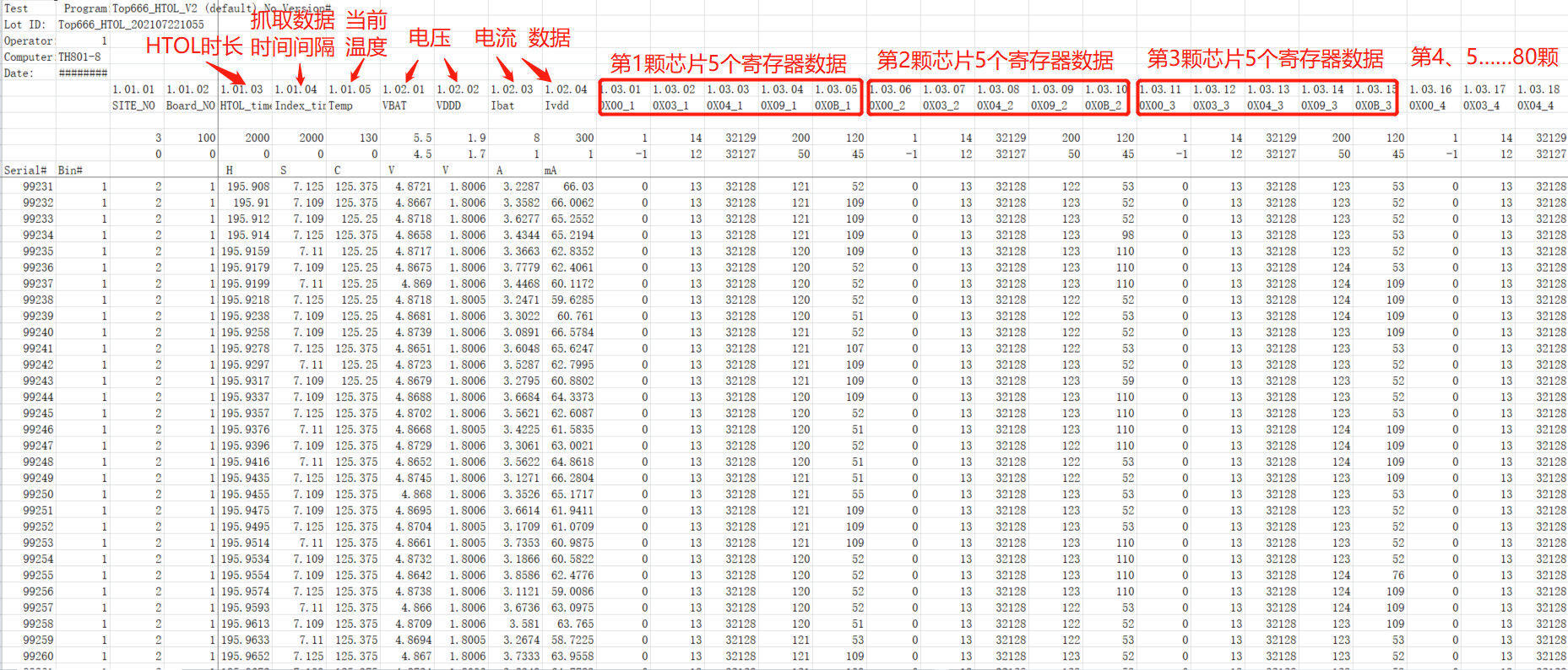

首先,我们先简单了解下什么是HTOL,HTOL(High TemperatureOperating Life)测试是评估集成电路(芯片)可靠性的一项关键性测试,它主要采用高温,高压的应力加速方式来模拟芯片的长期运行,以此评估芯片寿命和长期上电运行的可靠性、稳定性,通常称为老化测试。 简单来说HTOL就是芯片在高温度(>=125度),高电压(>=最大工作电压)的条件下,持续工作规定的时间(>=1000小时,不同应用场景,时间的规定也不同)后,观察芯片是否有失效现象。一般芯片在正式量产前,至少需要做三个批次的芯片老化测试,每个批次至少77颗样品,正式量产后也会选择性的抽样测试。一般老化前需要对每颗芯片进行ATE测试并记录数据,老化后如果ATE测试也全部pass,则说明HTOL测试通过(严格一点还要看关键参数的漂移情况),如有芯片失效,则需要分析具体失效原因,查明原因后再重新进行HTOL试验,直至全部pass,才能认为HTOL测试OK。 所以整个HTOL每个环节都非常重要,一旦某个环节出现问题引起芯片失效,就会直接导致额外投入大量的人力、物力、财力分析相关原因,而且很多时候因为没有足够的老化过程数据,很难分析出具体原因。另外因为老化测试周期比较长,重新做老化测试所耗费的时间成本也是很多公司很难承受的。所以针对老化测试,从样品的选择及测试,老化板方案设计,外围器件选择,老化板PCB设计制作,老化测试调试,setup,老化过程监控,老化下电操作等诸多细节都需要特别认真仔细。本文将重点讲解HTOL过程中容易出现问题的地方,以供大家参考。 首先,在芯片老化方案设计上,我们通常会参考芯片应用电路图进行老化方案设计,对于功能简单的芯片也基本OK,不过对于复杂一些的芯片,需要考虑更多因素,因为老化测试首先需要芯片上电正常工作,另外需要让芯片内部的每个模块都能参与工作,这样的老化测试才更有意义,如果某个模块在老化过程中没有参与工作,那么这部分电路则没有起到老化作用,需要对老化方案进行优化。具体需要跟设计工程师详细沟通。 另外,当我们参考芯片应用电路图进行设计老化电路时,外围器件的选型,要留有充足的余量,如电源滤波电容,可选用比推荐的容值、耐压、耐温都要高一些的,以确保在高温状态下也能让芯片稳定工作,每颗芯片的电源也最好加一个保险丝,这样当其中一颗电源短路失效时,不会波及到其他芯片。还有老化板总电源输入端还可以加上合适的TVS以降低上下电产生的浪涌影响。如果条件允许还可以加一些必要的LED指示灯,以方便确认芯片工作状态,以及后续老化过程中的观测。 其次,在整体结构设计上,一般主要采用两种方式:子母板的方式和socket的方式。这两种方式的选择上,可以从芯片的封装形式,引脚数量的多少,功耗的大小来综合考虑。如封装比较小,引脚比较少的,我们可以优先考虑采用子母板的方式进行,这种连接方式,对同一系列的产品(功能类似,封装不同),只需要设计子板即可,母板可以复用,成本会低不少,另外这种方式也方便对芯片进行编号,以及在ATE测试时也都方便些,此方案需要针对子板排针定义做一个对应的ATE测试板,这类小封装的芯片比较容易出问题的是WLCSP封装,这类封装体比较小,而且封装体也比较脆弱,如果采用socket的方式进行HTOL,那么在ATE测试时需要特别注意,特别在用镊子夹持的时候容易导致芯片产生裂纹,此时采用塑料镊子会有所改善。 子板的设计需要考虑连接器的选择,一般有排针、排母的方式,也有野口座、金手指的连接方式,排针排母的方式成本更低一些,同时需要考虑子板的大小及厚度,因为ATE回测时需要拔插子板,拔插时会导致子板PCB变形,产生的应力可能会导致芯片产生裂纹,或者焊点断裂,具体操作时需要特别注意,一般建议子板小一些,厚一些,这样不太容易变形,会好一些。另外连接器的PIN最好采用双保险的方式(电源,地可以更多些),以确保在高温状态下接触良好,同时也可以延长老化板的使用寿命。 当引脚数量过多的时候,子母板的方式就会有些局限,因为此时需要的连接器PIN数较多,拔插子板比较困难,更容易带来子板变形的问题,这种情况采用socket的连接方式比较好,socket的选择需要根据芯片参数指标进行,socket的连接方式每一款芯片都需要重新设计母板,成本比较高,不过这种方式的ATE回测相对简单,不需要重新制作HTOL ATE测试板,用量产FT的loadboard即可实现。 整体结构确定了之后,接下来就是老化子、母板的PCB layout了,这个也至关重要。先说一下子板,首先子板上需要预留一些必要且关键的外围器件,尤其那些需要尽量靠近芯片引脚放置的器件,以确保芯片能够稳定工作,另外layout时尽量避免引脚下过孔,尤其是CSP或者BGA封装的产品,否则特别容易出现问题。另外控制子板大小适中,方便标记和拔插。相对于简单些的子板来说,老化母板的PCB layout尤其重要,从大的方面来说,母板上电流要大很多,电源、地最好能有单独的一层甚至多层,以确保不同工位的芯片电压保持一致,另外有些芯片需要大的负载电阻,这些需要特别处理,可以放置于母板背面,以免负载发热过大,影响芯片周围环境温度。细节方面,输入信号有时是一对多,需要注意阻抗匹配及信号负载能力,如对信号质量要求较高的,需要注意对信号屏蔽,以增强抗干扰能力,另外需要注意老化炉内的风循环方向,子母板结构设计上注意尽量让空气对流通畅,以免影响环境温度及均匀性。 在PCB layout完成后,就进入老化板加工及贴片:首先PCB板材的选择,必须根据实际老化温度采用耐高温板材,PCB加工时采用沉金或镀金工艺为佳。外围器件也必须采用耐高温器件,贴片焊接时接插件注意定位摆正,避免歪斜,以免引起接触不良,金手指或者与socket接触的PAD需要镀金,尽量厚一些,以确保接触良好及耐用。 当老化板制作完成后,可以开始老化测试的调试工作了,一般我们可以先简单测试一下有没有电源短路的情况,确认没问题后,可以先进行单颗芯片的调试,当单颗调试OK后,再逐步增加其余的芯片进行调试,这样可以避免因为某个环节出错,导致大量烧坏芯片的情况,当整个老化板调试完成后,就可以入炉老化,入炉老化也特别需要注意上电,下电的操作,一般老化板的总电流都比较大,电源走线也会有寄生电感,在上下电的瞬间,会产生较大的过冲,此时特别容易打坏芯片,有条件的可以采用逐一控制每颗芯片的开启和关闭,让电流缓慢变大、缓慢变小,这样可以尽可能的避免过冲或者降低过冲,以保证芯片不被打坏。另外要尽量避免在高温时上下电操作,如果老化过程中出现问题需要排查,尽量降温后操作,一般降温到40度以下操作为宜。 最后再说一下老化过程监控的问题,也是非常重要的一个环节,传统的老化测试主要依靠人工观测整个老化板的电压、电流,每天记录数据,发现异常需要降温开炉,工程师再用万用表,示波器等工具确认每颗芯片工作状态,排查具体哪颗芯片失效,这样效率非常低,也及其浪费人力。另外在实际的老化测试中,我们也经常遇到一块老化板的80颗芯片,有些电流变大了,有些变小了,这样虽然总的电压,电流正常,但实际上有些芯片已失效的情况。也有的时候总的电流变化比较大,而单颗芯片的异常导致的电流变化比较小,这样即使有个别芯片异常也很难从总电流上体现出来。还有更严重的情况,由于接触或其他问题,导致芯片没有正常工作,这样即使1000小时后ATE测试pass,也无法真正说明HTOL通过。所以传统的监控方式很难保证可靠性测试的质量,也远远无法满足芯片质量提升的需求,亟需在线实时监控的解决方案。 目前国内比较领先的可靠性测试设备厂家已经有全参数监控的老化设备,比如上海顶策科技有限公司(Top ictest)推出的TH801,智能在线监控动态老化设备,可以监控的参数除了整板的电压,电流,还可以根据需求,监控到老化中每颗芯片的电压、电流,寄存器数据,时间,频率等诸多参数,并实时记录保存成Excel文档。这样不仅可以确保每颗芯片都处于正常的老化状态,保证老化测试的质量,同时还可以清楚的知道具体失效的参数,以及在什么时间点失效等诸多信息,非常有益于失效后的FA分析。另外由于可以监控更多芯片参数,这使得免除ATE回测成为可能,这将大大提高老化测试效率,节省更多人力成本!这项技术目前已在对芯片质量要求较高的芯片设计公司广泛应用。 如下为一款混合信号芯片的老化过程监测数据:  另外这类高端老化设备,除了实时在线监控电气参数的同时,也能非常方便针对不同芯片施加正玄波,方波,跑数字向量(pattern)等各类信号,这使得老化板的调试变的异常简单,高效!同时也大大简化了老化板的设计,据了解,顶策科技已研发出各类芯片(模拟,数字,混合信号芯片等)的通用老化板,这将大大缩短了老化测试的开发周期,同时也大大降低了老化测试的成本,使得更多芯片设计公司可以更低的成本来提高产品质量。 当前,中国芯片行业正处于从追求数量到追求质量的发展阶段,越来越多的芯片设计公司将加大质量提升的投入,追求高品质的芯片将是未来中国芯片行业的主流趋势,这也意味着提升芯片品质的可靠性测试设备也将随之创新发展,我们也欣喜的发现:像顶策科技这类创新型科技公司,将会引领可靠性测试设备的技术潮流,同时更快的推动国内集成电路的高质量发展,相信中国芯在不久的将来必定成就非凡,称霸世界! 上海顶策科技有限公司(Top-ictest),是一家致力于帮助芯片设计公司提升产品质量的高科技公司,目前已经拥有多项可靠性测试相关专利技术,公司于2021年取得国家级高新技术企业,其核心团队在芯片测试行业有着20年以上的技术积累,在可靠性测试整体解决方案上,有着异于他人的强大优势。目前顶策科技推出的智能在线监控动态老化设备,可以轻松实现芯片老化测试的整体监控和单颗监控,完美解决老化过程中的一系列问题,深得业内人士好评。 具体详情可联系:孙鹏程/13816654535(微信同号) 如下为智能老化设备简介,可先行了解下:  |